Abstract

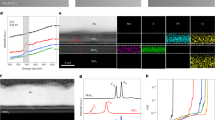

Two-dimensional (2D) semiconductors such as molybdenum disulfide (MoS2) have attracted tremendous interest for transistor applications. However, the fabrication of 2D transistors using traditional lithography or deposition processes often causes undesired damage and contamination to the atomically thin lattices, partially degrading the device performance and leading to large variation between devices. Here we demonstrate a highly reproducible van der Waals integration process for wafer-scale fabrication of high-performance transistors and logic circuits from monolayer MoS2 grown by chemical vapour deposition. By designing a quartz/polydimethylsiloxane semirigid stamp and adapting a standard photolithography mask-aligner for the van der Waals integration process, our strategy ensures a uniform mechanical force and a bubble-free wrinkle-free interface during the pickup/release process, which is crucial for robust van der Waals integration over a large area. Our scalable van der Waals integration process allows damage-free integration of high-quality contacts on monolayer MoS2 at the wafer scale and enables high-performance 2D transistors. The van-der-Waals-contacted devices display an atomically clean interface with much smaller threshold variation, higher on-current, smaller off-current, larger on/off ratio and smaller subthreshold swing than those fabricated with conventional lithography. The approach is further used to create various logic gates and circuits, including inverters with a voltage gain of up to 585, and logic OR gates, NAND gates, AND gates and half-adder circuits. This scalable van der Waals integration method may be useful for reliable integration of 2D semiconductors with mature industry technology, facilitating the technological transition of 2D semiconductor electronics.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available within the paper and the Supplementary Information. Other relevant data are available from the corresponding authors on reasonable request. Source data are provided with this paper.

References

Sangwan, V. K. et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS2. Nat. Nanotechnol. 10, 403–406 (2015).

Sangwan, V. K. et al. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature 554, 500–504 (2018).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Liu, C. S. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Zhou, J. D. et al. A library of atomically thin metal chalcogenides. Nature 556, 355–359 (2018).

Li, W. S. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Duan, X. D., Wang, C., Pan, A. L., Yu, R. Q. & Duan, X. F. Two-dimensional transition metal dichalcogenides as atomically thin semiconductors: opportunities and challenges. Chem. Soc. Rev. 44, 8859–8876 (2015).

Shim, J. et al. Controlled crack propagation for atomic precision handling of wafer-scale two-dimensional materials. Science 362, 665–670 (2018).

Yu, H. et al. Wafer-scale growth and transfer of highly-oriented monolayer MoS2 continuous films. ACS Nano 11, 12001–12007 (2017).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Asselberghs, I. et al. Wafer-scale integration of double gated WS2-transistors in 300 mm Si CMOS fab. In 2020 IEEE International Electron Devices Meeting 893–896 (IEEE, 2020).

Jung, Y. et al. Transferred via contacts as a platform for ideal two-dimensional transistors. Nat. Electron. 2, 187–194 (2019).

Zheng, X. R. et al. Patterning metal contacts on monolayer MoS2 with vanishing Schottky barriers using thermal nanolithography. Nat. Electron. 2, 17–25 (2019).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Liu, Y., Huang, Y. & Duan, X. F. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Liu, G. Y. et al. Graphene-assisted metal transfer printing for wafer-scale integration of metal electrodes and two-dimensional materials. Nat. Electron. 5, 275–280 (2022).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Chuang, H. J. et al. Low-resistance 2D/2D ohmic contacts: a universal approach to high-performance WSe2, MoS2, and MoSe2 transistors. Nano Lett. 16, 1896–1902 (2016).

Wu, R. X. et al. Van der Waals epitaxial growth of atomically thin 2D metals on dangling-bond-free WSe2 and WS2. Adv. Funct. Mater. 29, 1806611 (2019).

Leong, W. S. et al. Low resistance metal contacts to MoS2 devices with nickel-etched-graphene electrodes. ACS Nano 9, 869–877 (2015).

Liu, Y. et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. Nano Lett. 16, 6337–6342 (2016).

Wang, Y. L. et al. Probing photoelectrical transport in lead halide perovskites with van der Waals contacts. Nat. Nanotechnol. 15, 768–775 (2020).

Wang, J. L. et al. Low-power complementary inverter with negative capacitance 2D semiconductor transistors. Adv. Funct. Mater. 30, 2003859 (2020).

Ngo, T. D. et al. Fermi-level pinning free high-performance 2D CMOS inverter fabricated with van der Waals bottom contacts. Adv. Electron. Mater. 7, 2001212 (2021).

Purdie, D. G. et al. Cleaning interfaces in layered materials heterostructures. Nat. Commun. 9, 5387 (2018).

Guo, T. et al. Van der Waals integration of AZO/MoS2 ohmic junctions toward high-performance transparent 2D electronics. J. Mater. Chem. C 8, 9960–9967 (2020).

Li, J. et al. General synthesis of two-dimensional van der Waals heterostructure arrays. Nature 579, 368–374 (2020).

Kong, L. A. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Liu, L. T. et al. Transferred van der Waals metal electrodes for sub-1-nm MoS2 vertical transistors. Nat. Electron. 4, 342–347 (2021).

Carlson, A., Bowen, A. M., Huang, Y. G., Nuzzo, R. G. & Rogers, J. A. Transfer printing techniques for materials assembly and micro/nanodevice fabrication. Adv. Mater. 24, 5284–5318 (2012).

Linghu, C. H., Zhang, S., Wang, C. J. & Song, J. Z. Transfer printing techniques for flexible and stretchable inorganic electronics. npj Flex. Electron. 2, 26 (2018).

Mannix, A. J. et al. Robotic four-dimensional pixel assembly of van der Waals solids. Nat. Nanotechnol. 17, 361–366 (2022).

Huang, J. K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Popov, I., Seifert, G. & Tomanek, D. Designing electrical contacts to MoS2 monolayers: a computational study. Phys. Rev. Lett. 108, 156802 (2012).

Chuang, S. et al. MoS2 p-type transistors and diodes enabled by high work function MoOx contacts. Nano Lett. 14, 1337–1342 (2014).

Li, N. et al. Atomic layer deposition of Al2O3 Directly on 2D materials for high-performance electronics. Adv. Mater. Interfaces 6, 1802055 (2019).

Wang, H. et al. Large-scale 2D electronics based on single-layer MoS2 grown by chemical vapor deposition. In 2012 IEEE International Electron Devices Meeting 88–91 (IEEE, 2012).

Yu, L. et al. Enhancement-mode single-layer CVD MoS2 FET technology for digital electronics. In 2015 IEEE International Electron Devices Meeting 835–838 (IEEE, 2015).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Wang, L. et al. Electronic devices and circuits based on wafer-scale polycrystalline monolayer MoS2 by chemical vapor deposition. Adv. Electron. Mater. 5, 1900393 (2019).

Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934–9938 (2011).

Amani, M., Burke, R. A., Proie, R. M. & Dubey, M. Flexible integrated circuits and multifunctional electronics based on single atomic layers of MoS2 and graphene. Nanotechnology 26, 115202 (2015).

Huang, J.-K. et al. Large-area synthesis of highly crystalline WSe2 monolayers and device applications. ACS Nano 8, 923–930 (2014).

Song, H. S. et al. High-performance top-gated monolayer SnS2 field-effect transistors and their integrated logic circuits. Nanoscale 5, 9666–9670 (2013).

Zhao, M. V. et al. Large-scale chemical assembly of atomically thin transistors and circuits. Nat. Nanotechnol. 11, 954–959 (2016).

Yu, L. L. et al. Graphene/MoS2 hybrid technology for large-scale two-dimensional electronics. Nano Lett. 14, 3055–3063 (2014).

Pu, J. et al. Highly flexible and high-performance complementary inverters of large-area transition metal dichalcogenide monolayers. Adv. Mater. 28, 4111–4119 (2016).

Das, T. et al. Highly fexible hybrid CMOS inverter based on Si nanomembrane and molybdenum disulfide. Small 12, 5720–5727 (2016).

Yeh, C. H. et al. Graphene-transition metal dichalcogenide heterojunctions for scalable and low-power complementary integrated circuits. ACS Nano 14, 985–992 (2020).

Duan, X. D. et al. Lateral epitaxial growth of two-dimensional layered semiconductor heterojunctions. Nat. Nanotechnol. 9, 1024–1030 (2014).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Acknowledgements

We at Hunan University acknowledge the support from the National Natural Science Foundation of China (grant nos. 51802090, 51872086, 51991341, 52102168, 61874041, 61925403), the Innovative Research Groups of Hunan Province (grant no. 2020JJ1001), the Hunan Key Laboratory of Two-Dimensional Materials (grant no. 2018TP1010) and the National Key R&D Program of China (grant no. 2021YFA1200503). The author at Ningbo University of Technology acknowledges the support from the Scientific Research Starting Foundation of Ningbo University of Technology (grant no. 2022KQ37).

Author information

Authors and Affiliations

Contributions

Xidong Duan and Y.L. conceived and supervised the project. X.Y. designed the experiments. J.L. and R.S. performed the growth of the 2 inch MoS2 wafers with help from B.Z. and Z.Z.; X.Y. fabricated and measured the devices with help from J.T., L.K., H.H., L.L. and Y.L.; X.Y., J.L., H.H., Y.L. Xidong Duan and Xiangfeng Duan contributed to the data analysis and discussions of the results. X.Y., J.L., Xidong Duan, Y.L. and Xiangfeng Duan cowrote the manuscript, and all authors commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Nanotechnology thanks Won Jong Yoo and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary figs. 1–9 and text.

Supplementary video 1. The formation process of the bubble-free and wrinkle-free PDMS/PMMA interface.

Source data

Source Data Fig. 2

Statistical source data of Fig. 2.

Source Data Fig. 3

Statistical source data of Fig. 3.

Source Data Fig. 4

Statistical source data of Fig. 4.

Source Data Fig. 5

Statistical source data of Fig. 5.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Yang, X., Li, J., Song, R. et al. Highly reproducible van der Waals integration of two-dimensional electronics on the wafer scale. Nat. Nanotechnol. 18, 471–478 (2023). https://doi.org/10.1038/s41565-023-01342-1

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41565-023-01342-1

This article is cited by

-

Beyond the Silicon Plateau: A Convergence of Novel Materials for Transistor Evolution

Nano-Micro Letters (2026)

-

Orthogonal photopatterning of two-dimensional percolated network films for wafer-scale heterostructures

Nature Electronics (2025)

-

A mass transfer technology for high-density two-dimensional device integration

Nature Electronics (2025)

-

Sacrifice-layer-free transfer of wafer-scale atomic-layer-deposited dielectrics and full-device stacks for two-dimensional electronics

Nature Communications (2025)

-

Reconfigurable and nonvolatile ferroelectric bulk photovoltaics based on 3R-WS2 for machine vision

Nature Communications (2025)