Abstract

Layered dielectric materials and their van der Waals (vdW) heterostructures offer high potential for next-generation two-dimensional (2D) electronic devices, but materials that combine a wide bandgap and high dielectric constant are rare. Here, we present the controllable synthesis of quasi-vdW layered samarium oxysulfate (Sm2O2SO4) single crystals via a molten-salt-assisted chemical vapor deposition (CVD) method. These atomically thin crystals exhibit remarkable dielectric properties, including a wide bandgap (~5.54 eV), high dielectric constant (~18), robust breakdown voltage (>12 MV cm-1) and good thermal reliability. By integrating ultrathin Sm2O2SO4 nanoplates with 2D molybdenum disulfide (MoS2) via vdW forces, we fabricate field-effect transistors (FETs) showing a subthreshold swing down to 65.2 mV dec-1, hysteresis down to 5.4 mV, on/off current ratios of ~109, and gate leakage currents down to around 7 × 10-7 A cm-2. Furthermore, a high gate coupling ratio (GCR ~ 0.83) non-volatile memory device was developed based on the MoS2/h-BN/MLG/Sm2O2SO4/MLG heterostructure. The flash memory achieves ultrafast (~50 ns) programming/erasing operations, robust endurance (>2000 cycles) and long-term retention (>10 years). This work shows promising results for the integration of Sm2O2SO4 as a high-κ dielectric in future 2D devices, with implications for low-power, high-performance electronics.

Similar content being viewed by others

Introduction

Two-dimensional (2D) semiconductors, with high carrier mobility, tunable bandgaps, and atomic-scale thickness, are widely regarded as ideal channel materials for future technologies that aim to surpass silicon-based integrated circuits and memory computing architectures1,2,3. In recent years, floating-gate field-effect transistors (FGFETs) based on 2D materials have gained widespread attention4,5,6,7,8,9,10,11,12,13. 2D materials such as MoS2, ReSe2, HfS2, and MoTe2 demonstrate excellent electric field control, effectively reduce parasitic defect capture, and facilitate the scaling of memory and computing systems, thereby showing significant advantages in high-density integration14,15. However, the lack of high-quality blocking dielectric materials limits further improvements in low-power and ultrafast FGFET performance. Dielectrics must not only exhibit excellent electrical properties but also achieve low operating voltage, low leakage current, and stable thermal and electrical characteristics16,17.

Conventional high-κ oxides (HfO2, ZrO2, Ta2O5) enhance electrostatic control but are limited by atomic layer deposition (ALD) processes, which cause crystallization at the nanoscale and introduce interface defects, reducing device reliability18,19,20,21. Additionally, in-situ deposition may induce interface trap states, increase charge scattering, degrade carrier mobility, and elevate leakage current, restricting their applicability in 2D devices. Meanwhile, silicon-based floating-gate memory suffers from high tunneling barriers at the Si/SiO2 interface and dangling bonds, leading to a low gate coupling ratio (GCR), high power consumption, and short data retention times22,23,24. High-quality single crystal dielectric materials such as h-BN, Gd2O5, MgNb2O6, Eu2SOx, and Mn3O4, due to their excellent interface quality, have been widely used in 2D electronic devices as vdW dielectric materials, preserving the intrinsic properties of 2D semiconductors25,26,27,28,29,30. Recently, all-2D floating-gate memory utilizing h-BN as a blocking layer has been demonstrated, achieving atomically sharp interfaces and enabling miniaturization for high-density integration8. However, its low dielectric constant (κ = 2–4) limits electrostatic control, preventing further scaling of the equivalent oxide thickness (EOT), and constrains GCR improvement, ultimately affecting storage efficiency. Furthermore, an ideal gate dielectric should possess a wide bandgap to suppress leakage current, reduce interface state density, and enhance breakdown strength. For example, perovskite strontium titanate (SrTiO3) has an ultrahigh dielectric constant and holds promise for sub-1 nm EOT applications, but its relatively narrow bandgap (~3.2 eV <5 eV) leads to excessive leakage current, limiting its potential for future 2D CMOS applications31,32. Therefore, there is an urgent need to develop new dielectric materials with high GCR, a high dielectric constant, low leakage current, and stable interfaces to advance 2D electronics and storage technologies.

In this study, we report the successful synthesis of atomically thin samarium oxysulfate (Sm2O2SO4) dielectric single crystals using a molten-salt-assisted chemical vapor deposition (CVD) method. This quasi-vdW layered Sm2O2SO4 single crystal exhibits remarkable potential as a gate dielectric for 2D heterostructure devices due to its high dielectric constant (~18), wide bandgap (~5.54 eV), high breakdown field strength (>12 MV cm−1), and excellent thermal and electrical stability. Molybdenum disulfide (MoS2) with Sm2O2SO4 gate dielectrics operates with minimal hysteresis of 5.4 mV, a subthreshold slope (SS) of 65.2 mV dec−1, an on/off current ratio of 109, a low top-gate leakage current of 7 × 10−7 A cm−2, and high operational reliability at 500 K. Furthermore, leveraging the wide bandgap and high dielectric performance of Sm2O2SO4, we constructed a low-power (2.97 pJ) all-2D floating-gate memory device based on a MoS2/h-BN/MLG/Sm2O2SO4/MLG vdW heterostructure (here h-BN stands for hexagonal boron nitride and MLG stands for multilayer graphene), where Sm2O2SO4 was employed as a blocking layer. The resulting FG device exhibits outstanding non-volatile memory performance, including a low-voltage storage window (<3 V), high on/off ratio (>107), long data retention (>10 years), stable endurance (>2000 cycles) and fast (~50 ns) programming/erasing operations. These characteristics stem from its high-κ properties, which enhance GCR ( ~ 0.83), and the atomically sharp vdW interface. These findings highlight the potential of Sm2O2SO4 as a promising high-κ layered dielectric material for 2D nanoelectronics and high-GCR floating-gate memory devices.

Results

Controlled growth and structural characterization of Sm2O2SO4

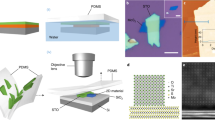

As shown in Fig. 1a, europium oxysulfate SmOSO crystallizes in the tetragonal lattice with an 224\({{\rm{I}}}\bar{4}2{{\rm{m}}}\) space group, and it possesses a quasi-vdW layered structure with a covalently saturated surface in the [001] direction. From the side view of the SmOSO structure, the crystal structure consists of alternating [SmO]⁺ cationic layers and [SO]⁻ anionic layers via electrostatic forces instead of vdW attractions. From the top view, the structure appears as consisting of multiple [SmO] units, where the Sm atoms form the framework and the O atoms occupy the central positions, with each Sm atom coordinated to two O atoms, creating a [SmO] subunit. Additionally, the [SO] group is symmetrically placed around the [SmO] units, with the S atom at the center and the four O atoms positioned around it in a tetrahedral arrangement.224222422222422

aThe crystal structure of SmOSO. Blue, yellow and red spheres represent Sm, S and O atoms, respectively. 224bSchematic of the strategy for the growth of layered SmOSO single crystals. 224cOptical microscopy (OM) image of SmOSO nanoplates. Scale bars: 10 µm. 224dThe optical band gap (Eg) is determined to be ~5.54 eV from the Tauc plot of the ultraviolet-visible absorption spectrum, where α, hand νare the absorption coefficient, Planck’s constant, and the light frequency, respectively. Inset: The calculated electronic band structure of Sm2O2SO4. e Typical Raman spectra of ultrathin SmOSO nanoplates transferred onto SiO/Si substrate acquired at room temperature. 2242fX-ray photoelectron spectroscopy (XPS) spectra of Sm 3 dorbitals. gThe energy dispersive X-ray spectroscopy (EDS) elemental mapping images of SmOSO nanoplate. Scale bars: 0.5 µm. 224hThe high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) image of SmOSO. Scale bars: 2 nm. 224iThe high-magnification HAADF-STEM image (top) and selected-area electron diffraction (SAED) pattern (bottom) of SmOSO nanoplate. Scale bars: 0.5 nm and 5 nm. 224−1j, kCross-sectional atomic-resolution HAADF-STEM images and corresponding atomic models of ultrathin SmOSO nanoplate taken along the zone axes of 224j[100], and k [\(\bar{1}30\)]. Scale bars: 1 nm.

High-quality ultrathin Sm2O2SO4 nanoplates were synthesized using the molten-salt-assisted chemical vapor deposition (CVD) system, employing mica as growth substrate, Sm2(SO4)3 · xH2O as the growth precursor and KI as eutectic melt (Fig. 1b and Supplementary Fig. 1 for details). During the melting process, molten salts promote the dissolution of precursors, ion diffusion, and the assembly of basic units, with nucleation and growth primarily occurring in the lateral direction based on the reaction process as follows: Sm2(SO4)3 · xH2O + 2H2 + KI → Sm2O2SO4 + 2SO2 + (2+x)H2O + KI. Optical microscopy (OM) images confirm that the Sm2O2SO4 nanoplates exhibit a transparent rhombic-like shape and atomically thin nature, with maximum lateral sizes of 50 μm (Fig. 1c and Supplementary Fig. 2a). Supplementary Fig. 2c shows the atomic force microscope (AFM) image of a typical Sm2O2SO4 nanoplate, which features atomically smooth surface and ultrathin thickness of ~5.2 nm. The crystal size and thickness can be commendably controlled by modulating the growth parameters (Supplementary Fig. 3). The statistical results, as shown in Supplementary Fig. 3c, f, and i, indicate that the lateral crystal sizes are mainly distributed in the range of 20-60 μm, with a concentration around 40 μm. Besides, the as-synthesized Sm2O2SO4 nanoplates are prone to wrinkling when washing residual salts, indicating a weak adhesion force between nanoplate and mica substrate, originating from the vdW epitaxy mechanism (Supplementary Fig. 4)29. Therefore, ultrathin Sm2O2SO4 nanoplates can be easily released from the growth substrate and transferred onto other target substrates or constructing artificial heterostructures. Density functional theory (DFT) calculations are performed to investigate the electronic band structure of layered Sm2O2SO4. As plotted in Fig. 1d, Sm2O2SO4 displays a large indirect band gap of ~5.67 eV, with the conduction band minimum (CBM) and valence band maximum (VBM) both located at the Γ and near the X points of the 2D Brillouin zone, respectively. The conduction band is made up hybridized Sm p and S p states associated with the empty O 1 s lone pair, while the valence band consists mainly of S p states. Furthermore, we analysed the optical bandgap from the absorption spectrum using ultraviolet-visible spectroscopy and found that the bandgap of ultrathin Sm2O2SO4 nanoplates is ~5.54 eV, which is higher than that of the most crystalline high-κ dielectrics such as SrTiO3 (3.2 eV)32, Bi2SeO5 (3.9 eV)33, Sb2O3 (4.06 eV)34 and Bi2SiO5 (3.79 eV)35. To study the chemical structure and crystallinity of Sm2O2SO4, Raman and Photoluminescence (PL) spectra measurements were conducted. As shown in Fig. 1e, the Sm2O2SO4 crystal exhibits four vibrational modes (ν1, ν2, ν3 and ν4) corresponding to the free [SO4]2⁻ ions with Td symmetry, and two prominent peaks at 333.4 and 418.8 cm−1, which are attributed to the Sm-O fundamental modes, consistent with previous experimental Raman results36. We systematically performed Raman spectroscopy on Sm2O2SO4 crystals of different thicknesses (Supplementary Fig. 5). As the thickness decreases, the peaks (ν1, ν2, ν3 and ν4) become less pronounced, which can be attributed to the weaker intensities of four vibrational modes in few-layer Sm2O2SO4 nanoplates. PL spectra of the bulk Sm2O2SO4 crystal is recorded using excitation wavelength 532 nm in Supplementary Fig. 6a. Four peaks can be observed at 562 nm, 608 nm, 644 nm, and 658 nm, corresponding to the characteristic luminescent bands of the Sm3+ ions, arising from the transitions of the 4G5/2 state to the 6H5/2, 6H7/2 and 6H9/2 multiplets, respectively. However, as the thickness decreases, the three peaks at 608 nm, 644 nm, and 658 nm become less pronounced, which can be attributed to the reduced luminous efficiency in few-layer Sm2O2SO4 nanoplates due to enhanced surface effects and non-radiative recombination pathways37,38. Supplementary Fig. 6b shows the cathodoluminescence (CL) spectra of ultrathin Sm2O2SO4 nanoplates transferred onto a SiO2/Si substrate. Two distinct peaks are observed at 606 nm and 652 nm, which correspond to the electronic transitions labeled 6H7/2 and 6H9/2 due to the f-f transitions of Sm3+ ions. Additionally, the chemical states of ultrathin Sm2O2SO4 nanoplates were analyzed using X-ray photoelectron spectroscopy (XPS) (Fig. 1f and Supplementary Fig. 7). The binding energies of 1083.5 and 1110.4 eV confirm the presence of Sm3+ 3d5/2 and Sm3+ 3d3/2, respectively. The O 1 s binding energies of 529.2 and 532.1 eV are attributed to Sm-O and [SO4]2⁻ species, while the S 2p3/2 binding energies of 168.9 and 170.1 eV are assigned to Sm-S.

Scanning transmission electron microscopy (STEM) studies are used to investigate more information about the crystal structure of the transferred ultrathin Sm2O2SO4 nanoplates (Supplementary Fig. 8a). The typical high-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) images of the rhombic Sm2O2SO4 crystal (Fig. 1g and Supplementary Fig. 8b) along the [001] zone axis is shown in Fig. 1h and Supplementary Fig. 9a, b. The intuitive plan-view STEM images reveal a highly-crystallized tetragonal crystal structure with no atomic vacancies or lattice deformation. The lattice spacings are estimated to be ~4.15 and ~2.93 Å, as verified by the enlarged HAADF-STEM image (Fig. 1i), matching well with the structure of (100) and (110) plane of the tetragonal phase Sm2O2SO4 crystal. Besides, the selected-area electron diffraction (SAED) pattern along the [001] zone axis shows the corresponding tetragonal structure. The energy dispersive X-ray spectroscopy (EDS) elemental mapping confirms the uniform distribution of Sm, S and O throughout the entire nanoplate (Supplementary Fig. 9c). To identify the layered characteristic in Sm2O2SO4 single crystal, a nanoplate was cut using a focused ion beam (Supplementary Fig. 10), followed by atomic-resolution cross-sectional HAADF-STEM imaging. Figure 2j, k and Supplementary Fig. 11 show atomic-resolution STEM imaging along three-zone axes ([100], [\(\bar{1}30\)]., and [110]) with a regular layered arrangement, as well as corresponding atomic models of Sm2O2SO4. The alternative stacking of [Sm2O2]2⁺ and [SO4]2⁻ layers with a layer space of 7.4 Å is observed, and the measured lattice fringes of 4.15, 2.93, and 1.72 Å can be attributed to the lattice planes of (010), (\(1\bar{1}0\)), and (310), respectively. These results indicate the successful fabrications of the 2D quasi-vdW layered Sm2O2SO4 single crystal.

a Schematic (top) and OM image (left bottom) and Raman spectroscopy (right bottom) of the double-gate graphene (Gr) field-effect transistor (FET) with the Sm2O2SO4 top-gate dielectric on SiO2/Si substrate (here Vtg, Vbg and Vds represent the top-gate voltage, back-gate voltage, and drain-to-source voltage, respectively). Scale bars: 5 µm. b Total resistance of a typical dual-gate graphene FET as the function of Vtg at different Vbg. c Vbg-dependent top-gate Dirac point voltages of the dual-gate graphene FET. d Thickness-dependent capacitance–voltage (C-V) measurements of Sm2O2SO4 nanoplates at measurement frequency of 100 kHz. e Thickness-dependent dielectric constant of Sm2O2SO4 measured by the C-V method. Inset: thickness dependent equivalent oxide thickness (EOT) of Sm2O2SO4. f Current leakage and breakdown characteristics of Sm2O2SO4 nanoplates measured by metal-insulator-metal (MIM) devices with thicknesses ranging from 6.5 to 22.3 nm. The dashed lines mark the limits for various electronic applications. DRAM, dynamic random access memory. g The breakdown field of Sm2O2SO4 at different temperatures. Inset: OM image of the MIM device. Scale bars: 5 µm. h Breakdown field versus effective dielectric constant of ultrathin Sm2O2SO4, compared with various dielectric materials18,20,26,27,32,33,34,35,41,42,43,53,54,55.

Dielectric properties of Sm2O2SO4

Dielectric constant, and breakdown field strength are key parameters that determine the performance of dielectric materials. To evaluate the dielectric properties of layered Sm2O2SO4 single crystals, dual-gate graphene FETs were fabricated by integrating graphene channels with ultrathin Sm2O2SO4 nanoplates on a p-Si substrate with a 285 nm SiO2 capping layer (Fig. 2a). The thicknesses of Sm2O2SO4 (15 nm) and graphene (single layer) were determined by AFM and Raman spectroscopy, respectively (Fig. 2a and Supplementary Fig. 12). In this setup, Sm2O2SO4 and SiO2 serve as the top- and back-gate dielectrics, respectively. The charge carriers in the graphene channel can be controlled simultaneously by applying top- and back-gate voltages28,30,39,40. The top-gate Dirac point voltage (VDirac, tg) can be modulated by the back-gate voltage (Vbg), as shown in Fig. 2b. Using a parallel plate capacitor model for the top- and back-gate, the slope of VDirac, tg with respect to Vbg corresponds to the ratio of the back-gate capacitance to the top-gate capacitance (CSiO₂/CSm₂O₂SO₄), as expressed in the following equation:

where \({\varepsilon }_{{{\mbox{Sm}}}_{2}{{\mbox{O}}}_{2}{{\mbox{SO}}}_{4}}\) and \({\varepsilon }_{{{\mbox{SiO}}}_{2}}\) (3.9) are the dielectric constants of Sm2O2SO4 and SiO2, respectively, and \({t}_{{{\mbox{Sm}}}_{2}{{\mbox{O}}}_{2}{{\mbox{SO}}}_{4}}\) and \({t}_{{{\mbox{SiO}}}_{2}}\) are their respectively thicknesses, we obtain the dielectric constant of 16.9 for 15-nm-thick Sm2O2SO4 from this device (Fig. 2c). To obtain the effective dielectric constant of Sm2O2SO4 more precisely, more dual-gate graphene FETs are fabricated using Sm2O2SO4 with various thicknesses as the top-gate dielectric (Supplementary Fig. 13).

Additionally, the parallel-plate capacitor device with ertical metal-insulator-metal (MIM) structure were also constructed to characterize the dielectric properties of Sm2O2SO4 (Supplementary Fig. 14a). In this setup, the Sm2O2SO4 layer was sandwiched between two vertically stacked Cr/Au electrodes on a quartz substrate. The corresponding capacitance–voltage (C-V) measurements at various frequencies (f) are shown in Supplementary Fig. 14b. The effective permittivity (εeff) can be calculated calculated using the following equation:

in which Ceff is the measured capacitance, A is the effective area, t is the thickness of the Sm2O2SO4 layer, and ε0 is the vacuum permittivity. Thus, the Sm2O2SO4 nanoplate with a thickness of 14.6 nm demonstrated a high εeff of 17.8, which is much higher than that of 2D hexagonal boron nitride (h-BN) (~5)25 and comparable with that of traditional high-κ oxide dielectrics such as HfO241, ZrOx42 and Al2O343. As shown in Fig. 2d and Supplementary Fig. 15, the capacitance exhibited a significant dependence on the thickness of the Sm2O2SO4 nanoplates. Correspondingly, the εeff of Sm2O2SO4 with different thicknesses is plotted in Fig. 2e, which shows a decreasing trend as the thickness reduces and can be well described by the typical ‘dead layer’ model due to the existence of interfacial capacitance (Supplementary Fig. 16)44,45. The corresponding EOT for Sm2O2SO4 can be calculated by the following equation:

where 3.9 is the dielectric constant of silicon oxide. Notably, the EOT shows a near-linear relationship with the Sm2O2SO4 thickness, implying that a 1.7 nm EOT can be achieved with a thickness of 6.5 nm nanoplate (Fig. 2e).

Beyond the dielectric constant, a low leakage current and high breakdown strength (Ebd) of dielectric materials are also important performance parameters for reducing device power consumption46,47,48. The Sm2O2SO4 nanoplates sandwiched between Cr/Au electrodes demonstrate the large Ebd in the range 1215 MV cm−1 (Fig. 2f), almost triple that of perovskite SrTiO3 membranes32, which are significantly higher than the required by the International Technology Roadmap for Semiconductors (ITRS)49. The thermal stability and electrical reliability of Sm2O2SO4 nanoplates were also evaluated, as these properties are critical for ensuring their performance in device applications. To ensure the reliability of the breakdown field strength results, we performed at least three independent measurements on different samples, as shown in Supplementary Fig. 17. All experimental results indicate that the breakdown field strength exceeds 10 MV/cm for samples of different thicknesses. Thanks to its high crystallinity and wide bandgap, the Sm2O2SO4 nanoplates maintain a high breakdown field strength of up to 10 MV/cm even at a high testing temperature of 500 K, demonstrating the robust breakdown performance of Sm2O2SO4 at various thicknesses. They exhibited a low leakage current of the order of 10−2 A cm−2 under 7.5 MV cm−1 (Fig. 2g). Low leakage current can be attributed to the well-defined vdW gap, which primarily improves leakage and stability by introducing an additional barrier at the interface to extend the carrier tunneling path, suppressing the interference of interfacial defects with charge transport, and alleviating stress concentration induced by lattice or thermal mismatch. To further confirm the potential of Sm2O2SO4 as a dielectric, the relationship between the breakdown field strength and corresponding dielectric constant of currently reported dielectrics was summarized in Fig. 2h. Given the superior dielectric properties of crystalline Sm2O2SO4 nanoplate, it is a promising insulating candidate for integration into high-performance FETs with 2D semiconductor channels.

High-performance 2D FETs with Sm2O2SO4 as gate insulator

To investigate the dielectric modulation effect of Sm2O2SO4, MoS2 FETs with Sm2O2SO4 as the top-gate dielectric were fabricated using the mechanical stacking method. (Supplementary Fig. 18). The device structure is shown schematically in Fig. 3a. The Sm2O2SO4/MoS2 top-gate FET was fabricated on a SiO2/Si substrate, utilizing Cr/Au as the source and drain electrodes. To ensure that Cr/Au exhibits a low contact resistance, we extracted its contact resistance Rc of 0.97 kΩ·μm using the TLM method, demonstrating reliable ohmic contact (see Supplementary Note 1 and Supplementary Fig. 19). It is important to emphasize that the focus of this work is not on the scaling of contact resistance. The output curves of the Sm2O2SO4/MoS2 FET show excellent gate control, as evidenced by the linear Ids-Vds curve at low Vds and saturation at high Vds, and exhibit a good ohmic contact between the electrodes and MoS2 (Fig. 3b). The corresponding transfer curves demonstrates a high on/off ratio of 107 and low gate leakage currents as low as 7 × 10−7 A cm−2 across a Vtg sweep from −1.0 to 1.0 V (Fig. 3c). There was a sharp increase in drain current in the subthreshold region, with an average subthreshold slope (SS) of ~65.2 mV dec−1 and a low drain-induced barrier lowering (DIBL) value of ~21 mV/V (Supplementary Fig. 20). Particularly, remains close to 60 mV dec−1 across more than two orders of magnitude of the drain-source current and stays below 100 mV dec−1 over three orders of magnitude of Ids (Fig. 3d). More importantly, we also investigated the thermal stability and electrical reliability of the Sm2O2SO4/MoS2 FETs. For a typical MoS2 FET device, the on/off current states could be well maintained even after being stored in air for 1 month, with an insignificant shift in threshold voltage (Supplementary Fig. 21). Benefitting from the high-quality interface with the low interfacial defect density between the Sm2O2SO4 and MoS2, the devices had an negligible hysteresis as low as 5.4 mV in the Ids-Vtg curve (Fig. 3e), ensuring the operational stability. The thermal stability of the dielectric properties in single-crystalline Sm2O2SO4 allowed the MoS2 FET device to maintain consistent performance without noticeable degradation even at a testing temperature of 500 K, exhibiting a small hysteresis width ΔVtg of no more than 24.4 mV (Fig. 3e, Supplementary Fig. 22).

a Schematic of the top-gated MoS2 FETs. b, c The output curves and transfer curves of a typical MoS2 FET with Sm2O2SO4 top gate. Inset: OM image of Sm2O2SO4/MoS2 FET. (channel width/channel length: WCH/LCH = 2.6 µm/7.5 µm, MoS2 thickness: 3.1 nm). Scale bars: 5 µm. d SS versus Ids extracted from the transfer curves. The dashed line marks 60 mV dec−1. e The transfer curves curves of the same device measured at 300, 400 and 500 K. Insets: corresponding hysteresis widths and OM image of Sm2O2SO4/MoS2 FET. Scale bars: 5 µm. f, g EDS elemental mapping images and a cross-sectional STEM image of the a Sm2O2SO4/MoS2 heterointerface. Scale bars: 10 and 1 nm. h Plane-averaged differential charge density of the Sm2O2SO4/MoS2 vdW heterostructure as a function of position along z direction.

To further validate the performance of the Sm2O2SO4-based top-gate FET devices, we fabricated MoS2 transistors with higher on-state currents. Using high-quality MoS2 single crystals (as shown in Supplementary Fig. 23), we have fabricated MoS2 FETs that achieve a switching ratio of up to 109. We further extracted the transconductance and mobility of the devices, with a maximum transconductance of approximately 38 μS/μm and a maximum mobility of around 81 cm2 V-1 s-1. These results confirm that, under conditions of lower defect density and higher crystal quality, the MoS2 FET devices with Sm2O2SO4 as the gate dielectric demonstrate good electrical performance, further validating the positive impact of material and process optimization on device performance. When the channel length of MoS2 FETs is reduced to 100 nm, Sm2O2SO4 demonstrates good electrical performance as a gate dielectric (Supplementary Fig. 24). Electrical statistics show that all devices exhibit steep subthreshold slopes (Supplementary Fig. 25), with the on/off ratio and field-effect mobility following a Gaussian distribution, averaging 7 × 106 and 48.6 cm2·V-1·s-1, respectively. The key parameters for transistors, such as on/off ratio, SS, hysteresis, EOT and Ebd, listed in Supplementary Table 1, highlight the great potential of Sm2O2SO4 single crystals for application in 2D electronics. These results demonstrate that the MoS2 FETs gated with Sm2O2SO4 dielectrics exhibit excellent thermal stability and electrical reliability.

In the microelectronics industry, traditional amorphous oxide dielectrics are typically integrated with semiconducting channels using ALD method, which often induces a substantial density of defects at the dielectric/semiconductor interface due to uncontrolled chemical bonding. These defects lead to the formation of border traps, which capture charge during device operation, resulting in increased subthreshold swing, wider hysteresis, and threshold voltage shift. The interfacial microstructure of top-gated MoS2 FET was analyzed by cross-sectional STEM image and EDS mapping. Figure 3f and Supplementary Fig. 26, the Sm2O2SO4/MoS2 shows a uniform layer thickness and clean, flat surfaces with a typical vdW gap. Atomic-resolution HAADF-STEM image in Fig. 3g exhibits a vdW gap of ~5.6 Å without any structural disorder, indicating a perfect interface with low carrier tunneling probability. The interface trap density (Dit) was extracted based on the following equation:

where kB is Boltzmann constant, T is absolute temperature, q is the elementary charge and CG is the gate capacitance. A low Dit value of 4.87 × 1011 cm-2 eV-1 can be achieved, which demonstrates its superiority compared to previously reported 2D MoS2 FETs with conventional oxides (Supplementary Table 2). To investigate the vdW interface between the Sm2O2SO4 dielectric and the MoS2 channel, a differential charge density calculation was carried out on the Sm2O2SO4/MoS2 heterostructure using DFT calculations. As shown in Fig. 3h, there is no charge accumulation at the Sm2O2SO4/MoS2 interface, indicating the absence of bonding interactions between Sm2O2SO4 and MoS2. Additionally, from the planar-averaged electron density difference curve, the average vdW gap is 5.2 Å, which is consistent with the cross-sectional atomic-resolution HAADF-STEM data. This value is significantly larger than the combined covalent radii of both O and S atoms, further supporting the existence of a vdW contact.

Non-volatile FG memory based on MoS2/h-BN/MLG/Sm2O2SO4/MLG

Floating gate (FG) memory, as a classic non-volatile storage technology, has been a research focus due to its high storage density, low power consumption, and excellent data retention capabilities17. However, conventional silicon-based FG memory suffers from high tunneling barriers and dangling bond issues at the Si/SiO2 interface, leading to slow operation, increased power consumption, and limited data retention5,50,51,52. 2D layered atomic-scale sharp high-κ dielectric materials, with their outstanding electrical properties and high stability, have emerged as promising alternatives to SiO2. They can effectively enhance the GCR of FG memory while enabling miniaturized integration6,8,10. A high GCR translates to faster programming, a larger memory window, lower power consumption, extended data retention, and low-voltage operation. We have leveraged the high dielectric constant and wide bandgap characteristics of Sm2O2SO4 to successfully fabricate a high-GCR FG memory device based on a MoS2/h-BN/MLG/Sm2O2SO4/MLG vdW heterostructure, where the channel material MoS2, tunneling h-BN, floating gate MLG, blocking Sm2O2SO4 and control gate MLG from top to bottom, respectively (Fig. 4a and Supplementary Fig. 27, 28). The corresponding OM image of the FG memory device is provided in Fig. 4b. With this configuration, our fully 2D memory device achieves a GCR as high as ~0.83 (further explained in the Supplementary Note 2), significantly exceeding that of silicon-based flash memory (0.49-0.57) and the state-of-the-art FG FET using h-BN as the blocking layer (0.6)6,8,10. Figure 4c exhibits the transfer curves obtained by scanning the control gate voltage (Vcg) from negative to positive values and then back to negative values, under a drain-source bias maintained at 0.1 V. A significant clockwise memory window (∆V) increases almost linearly with the maximum Vcg (Supplementary Fig. 29), where ∆V is defined as the difference between the positive and negative Vth offsets. Notably, even at Vcg < 3 V, a memory window exceeding 3.4 V is achieved, attributed to the high-κ Sm2O2SO4 enhancing GCR and effectively increasing the tunneling field in the h-BN layer. The output curves at different control voltages are shown in Fig. 4d. The output characteristic curve of the FG memory device (purple curve, fresh state) under no control gate voltage pulse exhibits a typical on-state with symmetric current due to initial doping of MoS2, also indicating a good ohmic contact at Cr/Au and MoS2 interfaces. When a positive voltage pulse (+20 V, 1 s width) is applied to the MLG control gate, the electrons are injected from the MoS₂ channel into the floating-gate MLG through the tunneling layer h-BN and are blocked by the blocking Sm2O2SO4 layer. This causes a redistribution of the charge in the top MoS2 layer, leading to the device entering the off-state. On the contrary, when a negative control gate voltage pulse is applied, the holes are injected into the floating-gate MLG, causing a change in the floating gate charge, which modulates the electrical properties of the top MoS2 layer. As a result, the device enters the on-state, exhibiting higher conductivity.

a Schematic diagram of the nonvolatile memory device. The functional layers from top to bottom are the channel material MoS2, tunneling hexagonal boron nitride (h-BN), floating gate multilayer graphene (MLG), blocking Sm2O2SO4 and control gate MLG. b Optical image of a memory device based on the MoS2/h-BN/MLG/Sm2O2SO4/MLG heterostructure. Scale bars: 5 µm. c Transfer curves of the device under bidirectional sweeping of different control gate voltage (Vcg) values and a Vds of 0.1 V, step: 200 mV/s. d Output characteristic curves of the device under the fresh state (no charge in the floating gate, orange), off-state and on-state (after a 1-second-wide voltage pulse of +20 V and −20 V applied to MLG control gate, red and purple) configurations. e Endurance performance of the nonvolatile memory device for 2000 cycles, showing the robustness of the all-2D-materials based nonvolatile memory device. f The real-time variation of the channel current value for multiple cycles as highlighted in e with the blue dashed box. g The retention characteristics of the device keep almost unchanged after 1.0 year. h Schematic energy-band diagrams of the nonvolatile memory device for writing and erasing program.

More importantly, our devices operated with excellent long-term memory stability and electrical reliability. The endurance performanceof FG memory device is validated by repeatedly programming and erasing the MoS2/h-BN/MLG/Sm2O2SO4/MLG vdW heterostructure (Fig. 4e), which shows that the on and off states of the current could be well maintained even after operating for more than 1000 cycles. Additionally, after 1.0 year, the repeated programming and erasing of the FG memory device for another 1000 cycles reveals no apparent change in either the program and erase states, demonstrating excellent durability and stability. Figure 4f shows an enlarged real-time memory state, indicating a stable transition between high and low current states. To verify the reliability of Sm2O2SO4 as a blocking dielectric, the maximum allowable voltage of 20 V was used as the operating voltage. After writing (+20 V) and erasing (-20 V) with a pulse duration of 1 s, the on/off ratio remained ~106 after 6000 s under a fixed Vds of 0.1 V at Vcg = 0 V (Fig. 4g), indicating a low back-tunneling probability by using Sm2O2SO4 as the blocking layer. Even after 1.0 year, the two current states characteristics of FG memory device show almost no changes. Additionally, we further evaluated the device’s fast programming/erasing performance (Supplementary Fig. 30). The results demonstrate that the device is capable of performing programming and erasing operations within nanosecond timescales (55.9 ns for erasing and 54.2 ns for programming), showing clear and stable state transitions. We further evaluated its energy efficiency, and the calculation results show that the energy consumption per pulse is 2.97 pJ (detailed in Supplementary Note 3). To further validate the long-term stability of the Sm2O2SO4-based floating-gate memory, we conducted testing using the Arrhenius method6. The results indicate that the memory exhibits over 10 years of stability, with a characteristic temperature of 179.2 °C and an activation energy of 2.03 eV (Supplementary Fig. 31 and Supplementary Note 4). Figure 4h illustrates the writing and erasing mechanisms of the device. When a positive pulse (Vcg > 0 V) is applied, electrons primarily tunnel from the MoS2 channel into the MLG floating gate via Fowler–Nordheim (FN) tunneling. The Sm2O2SO4 blocking layer effectively shields the control gate electric field, facilitating electron accumulation and stable storage. Conversely, when a negative pulse (Vcg < 0 V) is applied, the electrons in the floating gate tunnel back to the MoS₂ channel through FN tunneling, restoring the erased state. As shown in Supplementary Table 3, we compared the key performance of our device with other advanced 2D floating-gate memory devices. Our results demonstrate that the fully 2D high-GCR FG FET structure based on high-κ Sm2O2SO4 can overcome the low-power and low-GCR integration bottlenecks of conventional flash memory, holding potential for the development of next-generation low-power, fast non-volatile memory technologies.

In summary, we have shown that 2D crystalline high-κ Sm2O2SO4 dielectric can be synthesized via a molten-salt-assisted CVD method on a mica substrate. The ultrathin Sm2O2SO4 nanoplates have atomically flat surfaces, wide bandgap, high dielectric constants, and large breakdown strength, which could make it a potential dielectric for 2D FETs and other storage devices. Top-gated MoS2 FETs using Sm2O2SO4 as the dielectric exhibited an Ion/Ioff ratio of 109, a negligible hysteresis of 5.4 mV, a steep SS of 65.2 mV dec−1, and a low top-gate leakage current of 7 × 10−7 A/cm2. Furthermore, we demonstrated the use of Sm2O2SO4 dielectric as a blocking layer in FG memory, verifying the feasibility of miniaturized integration and low power consumption in 2D high-GCR FG devices. The dielectric properties of ultrathin crystalline Sm2O2SO4 nanosheets provide potential opportunities for developing low-power, fast electronic devices using the vdW integration strategy.

Methods

Synthesis and transfer of ultrathin Sm2O2SO4 nanoplates

2D Sm2O2SO4 single crystals were obtained by a molten-salt-assisted CVD system, which equipped with a 2-inch diameter quartz tube. Sm2(SO4)3 · xH2O powders (purity 99.9%, Aladdin) and KI powders (purity 99.9%, Aladdin) were dispersed on fluorophlogopite mica (KMg3(AlSi3O10)F2) substrate and placed in the center of the furnace as the reactant and solvent. Prior to the growth process, the furnace was purged with ultra-high purity argon (Ar) gas at a flow rate of 500 sccm for 10 minutes to eliminate residual oxygen. Then, the system was heated from room temperature to 680 °C in 15 min and maintained for 10 min for ultrathin nanoplates growth at the Ar/H2 carrier gas with the flow rate of 80/20 sccm. After growth, the ultrathin nanoplates were transferred onto a target substrate via the polystyrene (PS) assisted transfer method, as shown in Supplementary Fig. 7. Firstly, PS solution was spin-coated on the mica with grown ultrathin nanoplates, followed by drying at 80 °C for 5 minutes. Then, the PS-capped substrate was placed in deionized water and then the PS film with ultrathin nanoplates was carefully lifted off the mica. Subsequently, the film was attached onto the target substrates (such as copper grid and silicon substrate). Finally, after drying on a hot plate with 80 °C for 2 min, the PS layer was removed by hot acetone (70 °C for 10 min), completing the transfer of the ultrathin nanoplates.

Material characterization

The morphology and thickness characteristics of the ultrathin nanoplates were characterized by OM (Nikon instrument ECLIPSE LV150N) and AFM (Bruker Dimension Icon), respectively. Raman and PL spectra were recorded using a micro-Raman spectrometer (LabRAM HORIBA) with a 532 nm excitation laser source. The chemical composition and crystal microstructure were investigated through XPS (250Xi ESCALAB), TEM (JEM-ARM200F, JEOL), STEM (FEI-Titan Cubed Themis G2 300). The bandgap of ultrathin nanoplates was characterized by the ultraviolet-visible absorption spectrometer (Mstarter ABS).

Density functional theory calculations

All DFT calculations were conducted using the Vienna ab initio simulation package (VASP). The exchange-correlation interactions were described using the Perdew–Burke–Ernzerhof (PBE) form of the generalized gradient approximation (GGA). The interactions between ion cores and valence electrons were treated using the projector augmented wave (PAW) method. A plane-wave cutoff energy of 500 eV was set to ensure convergence and accuracy. For geometry optimization, a Γ-centered 3 × 3 × 1 Monkhorst-Pack k-point grid was used, and all structures were fully relaxed until the residual forces on each atom were below 0.01 eV/Å. To prevent spurious interactions between periodic images in the vertical direction, a vacuum layer larger than 20 Å was introduced. After structural relaxation, the band gap was calculated using a denser 6 × 6 × 3 k-point mesh.

Device fabrication and measurements

To fabricate the metal-insulator-metal (MIM) capacitors, bottom electrodes (5/50 nm Cr/Au) were first patterned on quartz substrates via electron beam lithography (EBL) followed by electron beam evaporation. Subsequently, Sm2O2SO4 nanoplates were transferred onto the patterned bottom electrodes using a PS and polydimethylsiloxane (PDMS)-assisted transfer technique on a 2D material transfer platform. Finally, top electrodes composed of Cr/Au (5/50 nm) were defined through a second EBL patterning and electron beam evaporation process.

For the Gr and MoS2 FETs, mechanically exfoliated Gr and MoS2 flakes were transferred onto a SiO2/Si substrate, followed by the transfer of grown Sm2O2SO4 nanoplates onto the Gr and MoS2 flakes, respectively. After that, Cr/Au (5/50 nm) electrodes were deposited using standard EBL and electron beam evaporation. The fabrication process for the FG memory devices, apart from the use of graphene as the bottom-gate electrode, was largely identical to that of the FETs. Specifically, the graphene stripes through mechanical exfoliation from bulk graphite crystals are firstly transferred on a SiO2/Si substrate as a bottom-gate electrode. Then, Sm2O2SO4, graphene, BN, and MoS2 layers were sequentially transferred onto the back-gate electrode using a 2D material transfer platform. Finally, the Cr/Au source-drain electrodes were fabricated on it by EBL and electron beam evaporation process.

Electrical characterizations of the MIM capacitors, FETs, and FG memory devices were carried out using a semiconductor parameter analyzer (Keithley 4200) equipped with capacitance-voltage measurement modules, in a vacuum probe station (TTPX, Lake Shore) with a base pressure of approximately 10-4 Torr. All electrical measurements were performed at room temperature unless otherwise stated.

Data availability

The Source Data underlying the figures of this study are available with the paper. All raw data generated during the current study are available from the corresponding authors upon request. Source data are provided with this paper.

References

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Liu, H. et al. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Shim, J. et al. Controlled crack propagation for atomic precision handling of wafer-scale two-dimensional materials. Science 362, 665–670 (2018).

Xiang, Y. et al. Subnanosecond flash memory enabled by 2D-enhanced hot-carrier injection. Nature 641, 90–97 (2025).

Lu, H. et al. An ultrafast multibit memory based on the ReS2/h-BN/graphene heterostructure. ACS nano 18, 23403–23411 (2024).

Liu, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotechnol. 16, 874–881 (2021).

Yu, J. et al. Simultaneously ultrafast and robust two-dimensional flash memory devices based on phase-engineered edge contacts. Nat. Commun. 14, 5662 (2023).

Wang, H. et al. Ultrafast non-volatile floating-gate memory based on all-2D materials. Adv. Mater. 36, 2311652 (2024).

Cai, Y. et al. 8-bit states in 2D floating-gate memories using gate-injection mode for large-scale convolutional neural networks. Nat. Commun. 16, 2649 (2025).

Wu, L. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021).

Jiang, Y. et al. A scalable integration process for ultrafast two-dimensional flash memory. Nat. Electron. 7, 868–875 (2024).

Li, W. et al. The realization of dual-mode non-volatile storage by different regulation methods for floating gate devices based on ambipolar MoTe2 channel. Adv. Funct. Mater. https://doi.org/10.1002/adfm.202516861 (2025).

Niu, W. et al. Van der Waals gap enabled robust retention of MoS2 floating-gate memory for logic-in-memory operations. Adv. Funct. Mater. 35, 2422120 (2025).

Marega, G. M. et al. A large-scale integrated vector-matrix multiplication processor based on monolayer molybdenum disulfide memories. Nat. Electron. 6, 991–998 (2023).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Guo, L. et al. A silicon single-electron transistor memory operating at room temperature. Science 275, 649–651 (1997).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Chamlagain, B. et al. Thermally oxidized 2D TaS2 as a high-κ gate dielectric for MoS2 field-effect transistors. 2D Mater 4, 031002 (2017).

Jin, Y. et al. Controllable oxidation of ZrS2 to prepare high-κ, single-crystal m-ZrO2 for 2D electronics. Adv. Mater. 35, 2212079 (2023).

Kim, H. G. et al. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Watanabe, K. Dependence of effective carrier lifetime in iron-doped silicon crystals on the carrier injection level. Semicond. Sci. Technol. 11, 1713 (1996).

Ngo, T. D. et al. Selective electron beam patterning of oxygen-Doped WSe2 for Seamless lateral junction transistors. Adv. Sci. 9, 2202465 (2022).

Kahng, D. et al. A floating gate and its application to memory devices. Bell Syst. Tech. J. 46, 1288–1295 (1967).

Chen, T.-A. et al. Wafer-scale single-crystal hexagonal boron nitride monolayers on Cu (111). Nature 579, 219–223 (2020).

Knobloch, T. et al. The performance limits of hexagonal boron nitride as an insulator for scaled CMOS devices based on two-dimensional materials. Nat. Electron. 4, 98–108 (2021).

Zhu, C.-Y. et al. Magnesium niobate as a high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 7, 1137–1146 (2024).

Yuan, J. et al. Controllable synthesis of nonlayered high-κ Mn3O4 single-crystal thin films for 2D electronics. Nat. Commun. 16, 964 (2025).

Choi, Y. et al. Ionic polarization modulation for wide-bandgap high-κ 2D insulators. Nat. Mater. 24, 163–164 (2025).

Jian, C. et al. Dielectric regulation in quasi-vdW europium oxysulfur compounds by compositional engineering for 2D electronics. Adv. Mater. 37, 2418328 (2025).

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Li, T. et al. A native oxide high-κ gate dielectric for two-dimensional electronics. Nat. Electron. 3, 473–478 (2020).

Liu, K. et al. A wafer-scale van der Waals dielectric made from an inorganic molecular crystal film. Nat. Electron. 4, 906–913 (2021).

Chen, J. et al. Vertically grown ultrathin Bi2SiO5 as high-κ single-crystalline gate dielectric. Nat. Commun. 14, 4406 (2023).

Lee, S. W. et al. Hydrothermal synthesis and characterization of Sm2O2SO4 nanoplates. Bell Syst. Tech. J. 38, 1149–1154 (2017).

Yan, B. et al. Study of band-gap narrowing effect and nonradiative recombination centers for heavily C-doped GaAs by photoluminescence spectroscopy. J. Appl. Phys. 77, 4822–4824 (1995).

Zhu, S. et al. Photoluminescence mechanism in graphene quantum dots: Quantum confinement effect and surface/edge state. Nano Today 13, 10–14 (2017).

Li, Y. et al. Layered deep-UV optical crystal KZn2BO3Br2 as a high-κ dielectric for 2D electronic devices. Adv. Mater. 37, 2409773 (2025).

Xu, H. et al. Top-gated graphene field-effect transistors with high normalized transconductance and designable Dirac point voltage. ACS nano 5, 5031–5037 (2011).

Zou, X. et al. Dielectric engineering of a boron nitride/hafnium oxide heterostructure for high-performance 2D field effect transistors. Adv. Mater. 28, 2062–2069 (2016).

Liu, G. et al. Annealing dependence of solution-processed ultra-thin ZrOx films for gate dielectric applications. J. Nanosci. Nanotechnol. 15, 2185–2191 (2015).

Cheng, L. et al. Sub-10 nm tunable hybrid dielectric engineering on MoS2 for two-dimensional material-based devices. ACS nano 11, 10243–10252 (2017).

Kyeom Kim, H. et al. Scaling of equivalent oxide thickness of atomic layer deposited HfO2 film using RuO2 electrodes suppressing the dielectric dead-layer effect. Appl. Phys. Lett. 101 172910 (2012).

Stengel, M. et al. Origin of the dielectric dead layer in nanoscale capacitors. Nature 443, 679–682 (2006).

Wong, H. et al. On the scaling of subnanometer EOT gate dielectrics for ultimate nano CMOS technology. Microelectron. Eng. 138, 57–76 (2015).

International Roadmap for Devices and Systems (IRDS) 2021 Edition- IEEE IRDS. https://irds.ieee.org/editions/2021, accessed 13.3.2024.

Robertson, J. High dielectric constant gate oxides for metal oxide Si transistors. Rep. Prog. Phys. 69, 327 (2005).

Moore, M. International Roadmap for Devices and Systems (IRDS) 2020 Edition- IEEE IRDS. https://irds.ieee.org/editions/2020 (2020).

Tang, J. et al. A reliable all-2D materials artificial synapse for high energy-efficient neuromorphic computing. Adv. Funct. Mater. 31, 2011083 (2021).

Gwon, O. H. et al. Systematic design and demonstration of multi-bit generation in layered materials heterostructures floating-gate memory. Adv. Funct. Mater. 31, 2170317 (2021).

Li, D. et al. Two-dimensional non-volatile programmable p-n junctions. Nat. Nanotechnol. 12, 901–906 (2017).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Fan, X. et al. 2D edge-seeded heteroepitaxy of ultrathin high-κ dielectric CaNb2O6 for 2D field-effect transistors. Nat. Commun. 16, 2585 (2025).

Yi, K. et al. Integration of high-κ native oxides of gallium for two-dimensional transistors. Nat. Electron. 7, 1126–1136 (2024).

Acknowledgements

This work was supported by the National Natural Science Foundation of China (Nos. 62575285, 92580123 to W.L., Nos. 52372240 and Nos. U23A2094 to Q.C.), the China Postdoctoral Science Foundation (Nos. 2023M733495 to C.J., Nos. 2025M770054 to Q.J.), the Self-deployment Project Research Program of Haixi Institutes, Chinese Academy of Sciences (Nos. CXZX631 2022-GH09 to W.L.), and the Self-deployed Key Project of State Key Laboratory of Functional Crystals and Devices (GNJT-2025-ZD06 to W.L.).

Author information

Authors and Affiliations

Contributions

W.L. conceived the original idea and supervised the entire project. J.Y. and C.J. contributed equally to the work. J.Y. and C.J. completed all the experiments together with Q.J., Q.C. and Y.G. helped to conduct the testing and analysis of capacitor devicesed. J.K. co-supervised the entire project and provided constructive suggestions. All authors participated in scientific discussions.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Cheng-Yan Xu, Yu Zhou, and the other, anonymous, reviewer for their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Source data

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Yuan, J., Jian, C., Gong, Y. et al. High-κ samarium oxysulfate dielectric for two-dimensional electronics with enhanced gate coupling. Nat Commun 17, 1245 (2026). https://doi.org/10.1038/s41467-025-68007-6

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-68007-6

This article is cited by

-

van der Waals dielectrics for threshold engineering in two-dimensional field effect transistors

Nature Communications (2026)