Abstract

Understanding the interfaces between a contact metal and a two-dimensional (2D) semiconductor, as well as the dielectric gate stack and the same 2D material in transition metal dichalcogenide (TMD) based transistors, is a crucial step towards the introduction of TMD materials into advanced logic nodes. In particular, for the contact metal/2D interface, one of the key parameters is the Schottky barrier height (SBH), which is frequently extracted based on temperature-dependent subthreshold characteristics of TMD field-effect transistors (FETs). However, recently, using this methodology has resulted in rather low extracted SBH values for TMD-based transistors, which seems inconsistent with the low on-current levels in said devices. Here, we therefore connect measured device characteristics on monolayer (ML) MoS2 transistors with technology computer-aided design (TCAD) simulations. In particular, our analysis shows that low SBHs can be incorrectly extracted when the interface trap density Dit is substantial and exhibits, at the same time, a significant temperature dependence, as is the case for TMDs. In fact, TCAD simulations and comparison with the obtained electrical data reveal that the actual SBH is substantially larger than what is extracted when ignoring the above mentioned details of Dit.

Similar content being viewed by others

Introduction

Frequently, field-effect transistors based on novel semiconducting channel materials are built without mimicking the n/p/n or p/n/p doping profile of a conventional silicon-based metal oxide semiconductor field-effect transistor (MOSFET). In fact, the most common way of building prototype FETs is to employ metal source/drain contacts in conjunction with a gating scheme that controls the entire semiconducting channel. In most instances, a Si/SiO2 substrate with a thick dielectric layer is used as a global back gate, allowing for quick access to some basic device characteristics. For devices of this type, the contact resistance is dominated by the Schottky barrier at the source/drain-to-channel interfaces. In 20041, we discussed a novel approach to extract information, in particular the Schottky barrier height (SBH), using carbon nanotubes as an example. The idea was that the ultra-thin body of the channel material impacts, i.e., reduces the Schottky barrier thickness (SBT) in the gated channel region. This change, in turn, allows for substantial thermal-assisted tunneling between the contacts and the channel, impacting the inverse subthreshold slope (SS) of the device in its off-state. In fact, for gate voltages in the device off-state close to threshold, SS cannot reach the thermal limit, e.g., ∼60 mV/dec at room temperature, irrespective of the chosen gate oxide thickness, since this regime is impacted by the gate voltage response of the Schottky barrier thickness (SBT). Through a careful analysis of the “effective barrier height” ϕB, the one that can be extracted from an Arrhenius plot of device current versus inverse temperature T for different gate voltages VGS, the actual Schottky barrier height can be identified1. Our method has since been used frequently, including for ultra-thin body devices from transition metal dichalcogenides (TMDs).

In a number of instances very small extracted Schottky barrier heights of 12.5, 64, and 16 meV were reported2,3,4. As we discussed in our original paper, there are a couple of signatures that need to be present to ensure that the extracted SBH is indeed the one that actually determines the current transport. For example, (1) SS needs to be proportional to T in the thermal regime—i.e., in the deep off-state of the device—for our analysis to be applicable. Another sanity check is (2) the expected correlation between log(IDS) vs. VGS and ϕB vs. VGS in the thermal regime. In fact, for fully depleted devices (CD = 0), SS in the thermal regime should be (kBT/q) ∗ ln(10) ∗ m with m = 1 + Cit/Cox for constant Cit and Cox and −(dϕB/dVGS)−1 = m. In case of ref. 4, condition (1) does not apply, as apparent from figure 9b in ref. 4. Condition (2) is clearly violated in refs. 2,3,4 as evident from Fig. 3 if compared to Fig. 4b in ref. 2, from the absence of any ϕB-dependence in figure S3 in ref. 3, and from figure 9b, if compared to figure 9d in ref. 4, where “m” is labeled as “γ−1”, respectively.

In the following, we will elucidate why the above articles presumably vastly underestimated the actual SBH by comparing our own data with those previously published. In particular, we will identify a strong temperature dependence of Cit as the culprit for why our previously proposed SBH extraction method1 cannot be applied. To do that, we fabricated monolayer MoS2 transistors and electrically characterized the devices at different temperatures to extract the SBH and to understand the effect of the interface traps on the transfer characteristics, especially in the subthreshold regime. Additionally, TCAD simulations are employed to model the distribution of interface traps, which explain the change in subthreshold slope with temperature and underestimation of extracted SBH.

Results

Device fabrication and electrical characteristics

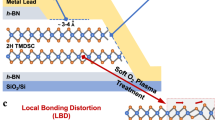

Figure 1a shows the schematic of the as-fabricated MoS2 transistor. The local bottom gates (LBGs) were first fabricated on a Si/SiO2 substrate by lithography (100 kV JEOL system) and metallization (e-beam evaporator—3 nm Cr/12 nm Au), followed by the deposition of 5.5 nm ALD HfO2 (200 oC thermal deposition, 50 cycles) and 3.6 nm amorphous boron nitride (a-BN), serving as the bottom gate dielectric. Next, a monolayer MoS2 film was wet transferred onto the LBG substrate and etched by reactive ion etching with Cl2/O2 (15 sccm/5 sccm) at a RF power of 40 W for 15 s. Finally, Ni source/drain (S/D) contacts were patterned using e-beam lithography and e-beam evaporation. Figure 1b, c show the transfer and output characteristics of an exemplary MoS2 transistor with a channel length of 200 nm. The device shows good off-state behavior, such as negligible drain-induced barrier lowering (DIBL) and low inverse subthreshold slope (SS ∼100 mV/decade, extracted between 1e-3 to 1e-4 µA/µm), and a high on-state current of ∼180 µA/µm at VDS = 1 V.

a Schematic diagram of an as-fabricated device. b Transfer and c output characteristics of an exemplary transistor with a channel length of Lch = 200 nm. d Temperature-dependent transfer characteristics and e Arrhenius plot (log(IDS/T2) vs. 1000/T) showing expected negative slopes for lower gate biases and unexpected positive slopes at high gate biases (f) extracted effective barrier height (ϕB) as a function of applied gate voltage. Note that negative effective barriers are extracted for gate voltages larger than ~2.3 V.

To study the impact of the interface trap density on the SBH extraction, we measured the transfer characteristics of ML MoS2 transistors at different temperatures for VD = 0.1 V as shown in Fig. 1d. At gate biases below flatband voltage (VGS ≤ VFB, here at current values of around 1e-3 µA/µm) the thermionic current determines the current through the device, with IDS given by ref. 1:

where A is the Richardson’s constant, ϕB is the effective barrier height, kB is the Boltzmann constant, q is the electronic charge, and T is the temperature. In order to extract the actual SBH (ϕSB), the temperature-dependent current values (shown in Fig. 1d) are used to generate an Arrhenius plot (log(IDS/T 2) vs. 1000/T), and the slope of the Arrhenius plot results in a ϕB vs. VGS plot, as shown in Fig. 1e. Note that using this technique over the entire gate voltage range means that ϕB is only capturing the “actual” barrier height for VGS ≤ VFB. This allows to identify the Schottky barrier height ϕSB, given that for gate biases lower than VFB the effective barrier height ϕB varies linearly with VGS in the thermionic transport regime. This leads to the extraction of a Schottky barrier height, SBH ∼90 ± 10 meV. It is important to note that (1) this value of SBH extracted from the transfer characteristics is significantly lower than the SBH obtained from TCAD simulations by fitting our experimental data, which will be discussed later in this paper and (2) the calculations have not been corrected for threshold voltage shifts in transfer characteristics at different temperatures, which is a common practice found in the literature4,5. Hence, to understand the effect of threshold voltage (VT) correction on the SBH extraction and the underlying reason behind the VT shift, the transfer characteristics are adjusted, as shown in Fig. 2a. Using these corrected current values, the Arrhenius plot (log(IDS/T 2) vs. 1000/T) is again generated. This time, the slopes (-qϕB/kB) are positive for all gate voltages as shown in Fig. 2b, resulting in a negative SBH extraction, which is not physically meaningful and also not consistent with our TCAD simulations. This erroneous SBH value extracted post VT correction is a result of the fact that in reality, the VT shifts with temperature in this device originate from a varying interface trap density profile, which we will demonstrate from our TCAD simulations in the next section.

a Temperature-dependent transfer characteristics after correcting for the apparent threshold voltage shifts (VT for all transfer characteristics was extracted by extrapolation in the linear regime. The VT shift at different temperatures, with respect to room temperature VT, was then subtracted from the gate voltage axis in the transfer characteristics, effectively aligning the curves across different temperatures.) and b Arrhenius plot (log(IDS/T2) vs. 1000/T) showing positive slopes. c Expected and extracted inverse subthreshold slope of the transistor in Fig. 1. d Interface trap density vs. temperature extracted from SS, evaluated between 1e-3 to 1e-4 µA/µm.

Noticing that the small extracted Schottky barrier height (without any VT correction) is a result of the very small temperature dependence of the subthreshold currents, we next extracted the inverse subthreshold slope (SS) in the deep off-state for currents between 1e-3 to 1e-4 µA/µm that correspond to the thermionic emission regime. Under these conditions, SS is expected to exhibit the following temperature dependence:

where CD is the depletion capacitance, Cit is the capacitance due to a finite interface trap density (Dit), given by Cit = q2 ∗ Dit and Cox is the gate oxide capacitance. Given the absence of any variation of depletion charge in the MoS2 channel to the applied gate bias, CD is zero in our fully depleted devices. Assuming no dependence of Dit on temperature, the subthreshold slope should linearly increase as the temperature rises, as represented by the black dots in Fig. 2c, assuming that at 300 K the actual Dit value had been extracted. However, the extracted SS values from the subthreshold characteristics at different temperatures, as shown by red dots in Fig. 2c are almost temperature independent. To explain the apparent absence of the expected temperature dependent trend from Eq. (2), one has to conclude that Cit is a function of T. The resulting Dit(T) is plotted in Fig. 2d. Interestingly, Dit increases with decreasing temperature, reaching a maximum value of 3 × 1013 eV−1cm−2 at 80 K. This finding is consistent with previous results by the IMEC group6 which show higher trap densities at lower temperatures from detailed capacitance measurements on TMDs as a function of T. The study combines the static model in the small signal regime with the distributed R-C network of the semiconductor to understand the dynamic nature of the MOS capacitor, focusing on segregating the effects of channel resistance from interface traps. The interface traps in such a way extracted for a 4 nm HfO2/3–5 ML MoS2 stack show an exponentially increasing amount of defect states toward the conduction band edge in the bandgap. In short, despite using different methodologies (temperature-dependent transfer characteristics in this study and C-V characteristics used in IMEC study6), both studies obtain an interface trap density distribution that increases approximately exponentially towards the MoS2 conduction band edge at the MoS2-dielectric interface. Hence, the expected decrease of SS with decreasing T is compensated for by an increase of Dit(T) for decreasing temperature. This implies that, similar to ref. 3 and4 our own MoS2 data cannot be used to extract the Schottky barrier height at the source/drain metal to TMD channel interface employing the methodology proposed in ref. 1. Also, similar to refs. 2,3,4, when using the extraction methodology, nonetheless, a vastly underestimated ϕSB-value is extracted.

One may ask the question whether the strong dependence of our Dit on temperature is a unique result of the TMD-to-gate stack interface. The answer is “no”. In fact, the observed temperature dependence can be translated into a Dit profile inside the TMD bandgap as a function of the energetic position relative to the band edges as discussed in the next section that is qualitatively consistent with what has been previously reported for other semiconducting channels, e.g., III–V7,8 and silicon9,10,11. The difference, however, lies in the magnitude of Dit. While silicon technology has achieved Dit-values in the 1010 to 1011 eV−1 cm−2 range, our extracted Dit-values at room temperature are substantially higher. This is also the reason why the methodology in ref. 1 can readily be applied to other transistor materials for Schottky barrier extraction as long as Cit is sufficiently smaller than Cox. To further understand the exact distribution of trap densities in MoS2 devices, TCAD simulations are employed.

Dit distribution extraction with TCAD

Using TCAD simulations, we have extracted a Dit(E) distribution that is consistent with the experimental temperature dependence of SS. The simulations are carried out with Synopsys Sentaurus Device (SDevice), in which the 2D material channel is represented as a bulk semiconductor with a 2D density of states12. Figure 3a shows the simulated structure, which mimics the experimental device. The source and drain contacts are modeled with a non-local Schottky barrier tunneling model13. An energy- dependent Dit distribution is assumed at the MoS2-a-BN interface and specified in SDevice, using an energy-dependent-Dit lookup table with an overall resolution of 50 meV and a 15 meV refinement for the first point. To capture in particular the on-state performance of our devices, a temperature dependent mobility, μ has been used as obtained from our earlier extraction on the same gate stack14 (see Fig. 3b). Other material parameters for MoS2 are obtained from ref. 15. The remaining calibration parameters are the values of the Dit distribution at each energy inside the TMD bandgap (independent of temperature) and the contact Schottky barrier height. While the deep off-state in the thermionic transport regime is used to determine Dit(E) from the various temperature-dependent measurements, the actual on-state performance is captured by the Schottky barrier height. Note that Dit(T) in Fig. 2d is the result of the integrated impact of Dit(E) for a particular temperature.

a Simulated structure mimicking the experimental structure of Fig. 1a, with a 0.2 nm van der Waals gap between the MoS2 and a-BN, b temperature dependent mobility impacted by phonon scattering as used in these simulations, c calibration of temperature dependent simulated transfer characteristics to experimental measurements of Fig. 1d, d resulting calibrated Dit distribution.

Figure 3c shows that the temperature dependence of the transfer characteristics can be well captured with a SBH of 180 meV and a Dit distribution that peaks towards the conduction band edge (EC) as shown in Fig. 3d. It should be noted that the simulations also show a VT-variation with temperature, even though no additional parameter had been varied with temperature, indicating that the shift between the 200 K and the 300 K curves arises from the interface trap density profile. The calibrated SBH of 180 meV is substantially larger than that obtained from the extraction methodology in the previous section, and Fig. 4a shows that the previously extracted value of 90 meV (calculated without threshold voltage correction of transfer characteristics) would result in a significant overestimation of the device currents, in particular for lower temperatures. For completeness, we also include the case of a higher SBH of 270 meV, showing the uniqueness of the calibrated value of 180 meV mentioned before.

a Comparison of temperature dependent experimental transfer characteristics with simulated curves for varying SBH values. b Simulated SS variation with temperature for a uniform Dit distribution throughout the MoS2 bandgap. c Simulated SS variation with temperature for a calibrated Dit distribution of Fig. 3c. The Dit distribution is scaled by a constant factor (DitFact), such that Dit=Ditfact * (Dit profile in Fig. 3d). SS is extracted in the IDS range of 1e-4 –1e-3 µA/µm. Indicated are also the extracted experimental values corresponding to Fig. 2c.

We further demonstrate that the experimental temperature dependence of the SS cannot be captured using a uniform Dit energy distribution. Figure 4b shows that for any given value of the uniform Dit, the simulated SS increases with temperature as discussed above in the context of Eq. (2), in contrast to the relatively constant experimental SS values of Fig. 2a. On the other hand, Fig. 4c shows that with a temperature independent peaked Dit(E) distribution, the temperature-induced SS increase is compensated as the Fermi-level shifts away from EC and toward lower values of Dit. For the calibrated Dit distribution, the SS is nearly constant within the considered temperature range, which corresponds to the experimentally observed trend.

In conclusion, this study investigated the effect of interface traps on the extraction of Schottky barrier height. The SBH extracted from temperature-dependent transfer characteristics of MoS2 transistors is significantly lower than the value extracted from TCAD simulations. TCAD simulations reveal that the calibrated SBH is two times higher than the experimentally extracted SBH using the approach described in ref. 1. This is due to the high interface trap densities at the 2D material/dielectric (MoS2/a-BN/HfO2) interface which results in underestimation of the SBH. The interface trap density is not only high, of the order of 1014 cm−2 eV−1 at the band edge, but also changes over an appreciable energy range inside the bandgap of MoS2.

Data availability

All data supporting the findings of this study are included in the paper. The corresponding author can also provide additional data upon reasonable request.

References

Appenzeller, J., Radosavljevi´c, M., Knoch, J. & Avouris, P. Tunneling versus thermionic emission in one-dimensional semiconductors. Phys. Rev. Lett. 92, 048301 (2004).

Zheng, X. et al. Patterning metal contacts on monolayer MoS2 with vanishing Schottky barriers using thermal nanolithography. Nat. Electron. 2, 17–25 (2019).

Kwon, J. et al. Thickness-dependent Schottky barrier height of MoS2 field-effect transistors. Nanoscale 9, 6151–6157 (2017).

Mitta, S. B. et al. Electrical characterization of 2D materials-based field-effect transistors. 2D Mater. 8, 012002 (2020).

Kaushik, N. et al Schottky barrier heights for Au and Pd contacts to MoS2. Appl. Phys. Lett. 105, 113505 (2014).

Gaur, A. et al. A MOS capacitor model for ultra-thin 2D semiconductors: the impact of interface defects and channel resistance. 2D Mater. 7, 035018 (2020).

Wang, S.-K., Cao, M., Sun, B., Li, H. & Liu, H. Reducing the interface trap density in Al2O3/InP stacks by low-temperature thermal process. Appl. Phys. Express 8, 091201 (2015).

Kaneki, S. & Hashizume, T. Interface characterization of Al2O3/m-plane GaN structure. AIP Adv. 11, 015301 (2021).

Thomas, S. M. Electrical Characterisation of Novel Silicon MOSFETs and finFETs. PhD thesis, University of Warwick (2011).

Cheng, J.-Y., Yeung, C. W. & Hu, C. Extraction of front and buried oxide interface trap densities in fully depleted silicon-on-insulator metal-oxide-semiconductor field-effect transistor. ECS Solid State Lett. 2, 32 (2013).

Novkovski, N. Modification of the Terman method for determination of interface states in metal–insulator–semiconductor structures. J. Phys. Commun. 1, 035006 (2017).

Verreck, D. et al. The role of nonidealities in the scaling of MoS2 FETs. IEEE Trans. Electron Devices 65, 4635–4640 (2018).

Synopsys. Sentaurus Device User Guide (2015).

Sun, Z., Chen, C., Robinson, J. A., Chen, Z. & Appenzeller, J. A mobility study of monolayer MoS2 on low-κ/high-κ dielectrics. In 2023 Device Research Conference (DRC) 1–2 (IEEE, 2023).

Laturia, A., Put, M. L. & Vandenberghe, W. G. Dielectric properties of hexagonal boron nitride and transition metal dichalcogenides: from monolayer to bulk. Npj 2D Mater. Appl. 2, 6 (2018).

Acknowledgements

H.J., Z.S., and J.A. acknowledge the joint MOU between the Indiana Economic Development Corporation, Purdue University, and imec, with in-kind support from the Applied Research Institute. D.V., S.S., C.J.L.R., and G.S.K. acknowledge imec’s Industrial Affiliation program for exploratory logic.

Author information

Authors and Affiliations

Contributions

H.J. and D.V. contributed equally. H.J. analyzed the experimental data and results. D.V., S.S., C.J.L.R., and G.S.K. discussed the SBH extraction method using TCAD and D.V. performed the TCAD simulations. Z.S. fabricated the device and conducted the electrical characterization. H.J., D.V., Z.S., and J.A. wrote the manuscript. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Jawa, H., Verreck, D., Sun, Z. et al. Interface trap states induced underestimation of Schottky barrier height in metal-MX2 junctions. npj 2D Mater Appl 9, 55 (2025). https://doi.org/10.1038/s41699-025-00576-y

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41699-025-00576-y