Abstract

The integration of high-κ dielectrics with two-dimensional (2D) semiconductors has long been limited by the low reactivity of their dangling-bond-free surfaces and the scalability issues of conventional deposition techniques. Here, we report a universal van der Waals (vdW) integration strategy using HfSe2 as a high-κ precursor that is dry-transferred onto MoS2 and WSe2 and fully converted into amorphous HfO2 via plasma oxidation, while preserving atomically flat vdW interfaces. The resulting HfO2/MoS2 and HfO2/WSe2 gate stacks exhibit suppressed interface trap densities (Dit ≈ 7–8 × 1010 cm-2 eV-1) and high dielectric constants (κ ≈ 23). MoS2 n-type field-effect transistors (nFETs) and WSe2 p-type field-effect transistors (pFETs) fabricated with this approach achieve nearly ideal subthreshold swing ( ≈ 60 mV/dec) and negligible hysteresis ( ≈ 3 mV). This scalable methodology enables the vertical integration of complementary logic, demonstrated by complementary FET inverters and ring oscillators, establishing a promising route toward three-dimensional, energy-efficient logic technologies.

Similar content being viewed by others

Introduction

The International Roadmap for Devices and Systems (IRDS) outlines a vertically integrated complementary metal-oxide-semiconductor (CMOS) architecture as a transformative strategy for advancing ultimate scaling design rules1. Within this framework, two-dimensional (2D) van der Waals (vdW) semiconductors, particularly transition metal dichalcogenides (TMDs) such as MoS2 and WSe2, are representative of n- and p-type channels. Known for their immunity to short-channel effects, chemical stability, and high mobility, they outperform strained silicon with similar thinness2,3,4, making them the most compelling combination for realising future three-dimensional (3D) logic gates5,6. Furthermore, their ability to reduce the overall stack height effectively suppresses parasitic capacitance, whereas their high on-current densities enable exceptional operating frequencies, making them a highly attractive option for advanced 3D integrated circuits7. Despite this promising potential, significant challenges remain for their use in practical applications. The most critical concern is exploring universal high-κ dielectric integration with superior interfacial and dielectric properties for both n- and p-type field-effect transistors (nFET and pFET), respectively, thereby improving gating efficiency in terms of scaled equivalent oxide thickness (EOT) and achieving desirable 3D complementary logic functionality for high-speed and low power dissipation systems considering industrial requirements8.

To date, recent advancements in high-κ dielectric integration on 2D semiconductors have primarily involved direct deposition, native oxidation, and vdW integration. Atomic layer deposition (ALD) is the most preferred method for high-κ dielectric integration owing to its industrial compatibility and capability for wafer-scale integration. However, the dangling-bond-free surface of 2D semiconductors reduces the surface reactivity during initial nucleation, fundamentally leading to non-uniform dielectric formation9,10,11. To address this issue, surface functionalisation using O2 plasma, UV-O3, and electron-beam irradiation has been introduced to assist the adsorption of precursors by creating activated sites12,13,14,15,16,17,18. However, directly modified interfaces introduce defect sites, including chalcogen vacancies in the channel, oxygen vacancies in the dielectric, and impurities, resulting in threshold voltage instability, increased subthreshold swing (SS), and hysteresis19,20,21,22. Sb2O3, an inorganic molecular crystal, is an alternative interlayer material23. Its cage-like molecular structure, which is free of dangling bonds, has shown improvements in the interfacial quality, allowing for high-quality ALD-grown dielectrics on 2D semiconductors. However, its relatively low dielectric constant ( ≈ 11.5) and unproven versatility in other TMDs require further consideration.

Native oxidation, an in-situ process, facilitates chemical conversion within the channel layer, resulting in an atomically sharp interface that is comparable to the SiO2/Si interface24. We recently demonstrated the layer-by-layer oxidation of 2D HfSe2 and HfS2 into HfO2 and particularly for the HfSe2 case achieved a low interface charge trap density (Dit) of ≈5 × 1010 cm−2 eV−1 25. Moreover, single-crystalline Bi2SeO5 native oxide layers have been successfully integrated even in vertically grown 2D Bi2O2Se channels, enabling fin field-effect transistors and broadening structural freedom26,27,28. However, this methodology is only feasible for a limited number of channel materials, excluding Mo- and W-based TMDs, which have the highest application potential, thereby restricting its wide adoption in future 3D complementary logic systems.

vdW integration, which forms an atomically smooth vdW interface between the dielectric and channel (i.e., physical separation with weak vdW coupling), ensures the chemical inertness and mechanical stability of 2D semiconductors, making it a promising approach for dielectric integration29,30,31. vdW integration is typically achieved via transfer methods and can be categorised by the transferred materials, such as single-crystalline dielectrics, amorphous dielectrics, and transferred and oxidised dielectrics. Since the discovery of 2D layered crystalline dielectrics, h-BN has been widely adopted because of its dangling-bond-free surface, which allows for the formation of a clean vdW interface32. Its large-scale synthesis using up to 4-inch wafers has also been demonstrated33, but its inherently low dielectric constant remains a significant limitation for low-power applications. Bi2SeO5 is a single-crystalline vdW-layered dielectric with a high dielectric constant (≈16.5). This system has shown potential, but its practical device applications and interface quality require further comprehensive verification34. Zeng et al. reported single-crystalline Al2O3 using intercalative oxidation on an aluminium surface and demonstrated a remarkably reduced interfacial trap density (≈8.4 × 109 cm-2 eV-1) with MoS235. They fabricated MoS2 FETs that exhibited a low SS of 61 mV/dec at room temperature. Despite this strategy, the minimum EOT is limited to ≈0.77 nm owing to the lowered dielectric constant after crystallisation, which remains a challenge for future scaled nodes. Recently, the transfer of ALD-grown amorphous dielectrics (e.g., HfO2 and Al2O3) on a wafer scale has been proposed as an alternative36,37. However, the use of sacrificial layers (e.g., PVA and TRT/PMMA) during the peel-off and lamination processes causes interfacial contamination, leading to increased SS and performance variability38,39,40,41. The most recent emerging strategy for vdW integration is to transfer and oxidise the dielectric, which process utilises Hf- and Zr-based TMDs as precursors. Jing et al. reported ultrathin amorphous HfOx sandwiched within vdW heterostructures obtained by the selective thermal oxidation of HfSe2 precursors, demonstrating a low leakage current density (≈10−6 A/cm2) and high breakdown field (≈9.5 MV/cm)42. Furthermore, the integration of high-κ HfOx on MoS2 has been achieved by oxidising transferred 2D HfS2 layer with UV-ozone treatment, showing promise as a 2D-compatible dielectric with a vdW interface and a low SS of 63.1 mV/dec43. Despite the progress in vdW integration, recent efforts have predominantly focused on n-type 2D semiconductors, leaving p-type 2D semiconductors underexplored. Moreover, the integration of these 2D semiconductors into circuit-level applications within 3D CMOS architectures remains unaddressed, revealing a critical gap toward realising 3D logic gates. Therefore, the scalable and advanced vdW integration of high-κ dielectric must be studied to successfully realise future 2D semiconductor-based 3D CMOS systems.

In this paper, we present a scalable approach for integrating vdW-interface-based high-κ dielectrics on both n- and p-type 2D semiconductors. By transferring HfSe2, a high-κ precursor, onto both MoS2 and WSe2 channels and subsequently converting HfSe2 into HfO2 via controllable plasma oxidation, an atomically flat vdW interface with a suppressed interface trap density (Dit, HfO2/MoS2: ≈7.1 × 1010 cm−2 eV−1 and HfO2/WSe2: ≈8.4 × 1010 cm−2 eV−1) was achieved. Large-scale ab initio molecular dynamics (AIMD) simulations based on density functional theory (DFT) were performed to clarify the mechanism of the layer-by-layer oxidation in HfSe2 and explain why the HfSe2-to-HfO2 conversion facilitates clean vdW interfaces with MoS2 or WSe2. The HfO2 layer exhibited a high dielectric constant (≈23) and low gate leakage current across various EOT ranges. The universality of this approach was further demonstrated by fabricating MoS2 nFET and WSe2 pFET systems, which exhibited nearly ideal SS values of 61 and 63 mV/dec (over four orders of magnitude of IDS) at room temperature (300 K), along with a high on-off ratio (≈108) and negligible hysteresis (≈3 mV). The consistent results observed in 40 devices further suggest the reproducibility of the proposed vdW interface-integrated FETs. Furthermore, we fabricated a vertically interconnected complementary field-effect transistor (CFET) inverter by sequentially stacking the MoS2 nFET and WSe2 pFET systems, demonstrating a high inverter gain (≈115), noise margin (NML, NMH = 98% of 1/2VDD), and reduced static power consumption (≈19 pW). Subsequently, ring oscillators (ROs) incorporating the proposed CFETs were demonstrated. These ROs achieved a reduced propagation stage delay time (≈1.83 ns), demonstrating their potential for high-performance circuit applications. These findings represent a major step forward in achieving scalable and universal vdW interface engineering, laying the groundwork for the future development of integrated circuits with 3D logic gates for post-Si technology.

Results

Universal high-κ dielectric integration with a vdW interface

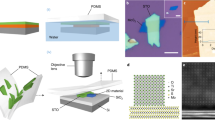

Figure 1a illustrates the integration process for a vdW-interface high-κ dielectric onto 2D semiconductor channels. The HfSe2 layer was transferred onto the channel materials and fully oxidised at an oxidation rate of ≈2.1 nm/min under pre-investigated oxygen plasma conditions (see details in the Methods section and Supplementary Figs. 2–4). In this manner, only HfSe2 was fully converted into the HfO2 dielectric while sustaining the atomically flat vdW interface, thereby preserving the underlying channel properties (Supplementary Figs. 5–9). The detailed mechanism of the vdW interface-terminated oxidation process is discussed in the following section. This universal approach was implemented to fabricate both HfO2/MoS2 and HfO2/WSe2 gate stacks, which exhibited atomically smooth vdW interfaces (Fig. 1b, c). Notably, the pristine vdW gap of the HfSe2/TMD (MoS2, WSe2) heterostructure remained intact after oxidation, maintaining the integrity of the clean vdW interface in the HfO2/TMD (MoS2, WSe2) heterostructures. The high-resolution STEM images in Fig. 1d, e further indicate that HfO2 formation is limited to the vdW gaps above the channels, sustaining the channel crystallinity. The observed interfacial gap (≈0.3 nm) between HfO2/TMD (MoS2, WSe2) is comparable to the physical vdW gap (defined as the chalcogen-to-chalcogen distance) between MoS2 and WSe2 (Fig. 1d, e). Furthermore, uniform coverage with consistently high vdW interface quality was observed in individual samples, and reproducible morphological results were obtained across multiple samples (Supplementary Fig. 10 and 11), demonstrating the robustness of the proposed vdW interface approach and its potential for broad applicability in various 2D semiconductor device platforms. The robust vdW interface maintained throughout thermal cycling further demonstrates its thermal stability (Supplementary Fig. 22). The scalability of this methodology toward wafer-scale integration will be further investigated in our future work through the combination with large-area 2D precursor formation approaches.

a Schematic illustration of the universally applicable HfO2 integration on TMDs, achieving an atomically flat vdW interface via transfer and plasma oxidation. b, c Cross-sectional scanning transmission electron microscopy (STEM) images of fabricated HfO2/MoS2 and HfO2/WSe2 gate stack, retaining the pristine vdW gap as a clean vdW interface after plasma oxidation (upper panels: before HfSe2 oxidation; lower panels: after full conversion of HfSe2 to HfO2). The arrows and boxes in pale pink and pale blue represent the HfO2/MoS2 and HfO2/WSe2 gate stacks, respectively. d, e Higher-resolution STEM images (left panels) showing the atomically flat vdW interface between fully converted HfO2 and TMDs (MoS2, WSe2). The corresponding intensity profiles (right panels) further confirm the presence of a vdW gap (≈0.3 nm) at the HfO2/TMDs (MoS2, WSe2) interface, comparable to the interlayer spacing (≈0.3 nm) of MoS2 and WSe2.

Mechanism of the formation of vdW HfO2/TMD interfaces

To clarify the mechanisms underlying the universal formation of atomically clean HfO2/TMD vdW interfaces via the oxygen plasma oxidation of HfSe2, we performed AIMD simulations within the DFT framework. While extensive AIMD simulations have been performed for the Si oxidation44,45, to our knowledge, the corresponding AIMD simulation study for HfSe2 or is non-existent25,46. Based on extensive testing, we initially established an AIMD protocol that simulates the oxygen plasma HfSe2 oxidation process (Fig. 2a). Briefly, it consists of (1) the introduction of several randomly distributed singlet O (1D) atoms dropping onto the HfSe2 surface with normal-direction velocities assigned according to the Maxwell-Boltzmann distribution, (2) a multiple picosecond (ps) NVE-ensemble oxidation MD run that captures the incorporation of O atoms into HfSe2 and the resulting migration and cluster formation of extracted Se atoms, (3) the removal of free-floating Se atoms or clusters, (4) a 1 ps NVT-ensemble quenching MD run with a Nosé-Hoover thermostat, and (5) the repetitive applications of steps (1)–(4) for the progressively oxidising HfSe2 (HfSexOy) model (Supplementary Figs. 12–14). Throughout MD simulations, reflecting the low-temperature plasma experimental condition, we adopted a temperature of 500 K.

a A sequence of microcanonical (NVE) and canonical ensemble (NVT) dynamics (highlighted by the light green box) is performed to simulate the oxidation of a monolayer HfSe2. Oxygen atoms are inserted at the start of NVE dynamics (red box), followed by NVT dynamics (blue box) after the removal of floating Se atoms. The striped arrow represents repeated application of the NVE–NVT cycle. b A partially oxidised HfSe2 (O36 model)/pristine HfSe2 structure undergoes further oxidation under the same NVE–NVT scheme, resulting in layer-by-layer oxidation and retention of a vdW gap. c A comparative analysis of O36 model/TMD interfaces within a single NVE dynamics step, where oxygen atoms are directed toward the bottom TMD layer. In HfSe2 (top), oxidation proceeds at the bottom layer, while in MoS2 (middle) and WSe2 (bottom), oxygen atoms primarily passivate the bottom surface of the upper oxide layer.

Applying the alternating NVE-NVT AIMD scheme to a HfSe2 monolayer modelled by a (3×4) supercell (Supplementary Fig. 12) and introducing four impinging O atoms, we first analysed the key atomistic features in the HfSe2 oxidation process (Fig. 2a and Supplementary Fig. 14). Next, as shown in Fig. 2b, we continued the AIMD simulations with an interface model prepared by placing a partially oxidised Hf24Se28O36 (O36) on top of a HfSe2 monolayer (Supplementary Fig. 12) and studied the mechanisms of the layer-by-layer HfSe2 oxidation process. Based on DFT-based energetic analyses, we previously showed that the facile HfSe2-to-HfO2 conversion is allowed because O atoms can replace Se atoms on a HfSe2 surface without a substitution energy barrier25. Through AIMD simulations, we could additionally observe that, upon reacting with HfSe2, impinging O atoms release significant heat (≈7 eV per O atom) and, due to thermal vibrations and strong Hf-O interactions, they rapidly (within a few ps) diffuse to Se sites (Supplementary Fig. 13). As the oxidation proceeds and the number of neighbouring O atoms increases in the top HfSexOy layer, Hf atoms that were initially placed planarly began to reconfigure vertically. This results in the formation of voids within the HfSexOy layer, which should act as pathways for the insertion (extraction) of O (Se) atoms into (out of) the deep HfO2/TMD interfacial regions. At the same time, the displaced Se atoms free floated on the HfSexOy surface and upon meeting other Se atoms formed Se clusters. We then observed that these mobile Se atoms remaining at the HfSexOy/HfSe2 interface play an important role in the layer-by-layer oxidation process by preserving the vdW gap until the full HfSexOy-to-HfO2 conversion is completed25.

To examine whether WSe2 and MoS2 behave differently from HfSe2 in forming clean HfO2/TMD vdW interfaces, we next considered a slightly non-ideal O excess condition that will lead to the breakdown of the layer-by-layer oxidation process for HfSe2. Specifically, as shown in Fig. 2c, we prepared the corresponding O36 HfSexOy/MoS2 and HfSexOy/WSe2 interface models (see also Supplementary Fig. 12) and (rather than dropping from the top) introduced four energetic O atoms into the HfSexOy/TMD interfacial region and repeated AIMD simulations. For the HfSexOy/HfSe2 case, we first confirmed that the second bottom HfSe2 layer begins to oxidise in the NVE run as in the first top HfSe2 layer (Fig. 2c top panel). On the other hand, for the HfSexOy/MoS2 and HfSexOy/WSe2 cases, we found that the O atoms cannot oxidise the top surface of MoS2 or WSe2 and continue oxidising the bottom side of HfSexOy (Fig. 2c middle and bottom panel). This difference indicates that compared with HfSe2, which requires precise control of the layer-by-layer process, achieving clean HfO2/TMD vdW interfaces based on plasma oxidation should be easier with MoS2 or WSe2 (Supplementary Figs. 15 and 16). This is in fact consistent with our experimental observations, indirectly validating our AIMD simulations.

Electrical performance of vdW interface-integrated FETs

Figure 3a shows a schematic of the FETs fabricated with the vdW interface-integrated HfO2/MoS2 and HfO2/WSe2 gate stacks, thereby integrating the MoS2 nFET and WSe2 pFET (see the Methods and Supplementary Fig. 1). Optical images and the output characteristics of these devices are shown in Supplementary Fig. 19. The quality of the vdW interfaces between the HfO2 and TMD channels was investigated using multi-frequency C−V measurements (Fig. 3b). The extracted interface trap densities (Dit) for HfO2/MoS2 and HfO2/WSe2 were suppressed to ≈7.1 × 1010 and ≈8.4 × 1010 cm−2 eV−1, respectively, aligning with the structural and theoretical clarifications discussed above (see details of the measurements and analysis in Supplementary Fig. 17). A high dielectric constant (κ = ≈23; see Supplementary Fig. 17) and low gate leakage current were consistently achieved in EOT ranges of 0.5–2.5 nm (Supplementary Fig. 18), indicating high-quality dielectric characteristics. The suppressed leakage current, compared with the crystalline phase, further underscores the intrinsic advantage of maintaining the amorphous phase to ensure low-power device integrity (Supplementary Fig. 19). Notably, the fabricated MoS2 nFET and WSe2 pFET exhibited near-ideal SS values of 61 and 63 mV/dec (over four orders of IDS) at room temperature (300 K), along with a high on-off ratio of ≈108 and low gate leakage current of ≈10-6 A/cm2. (Fig. 3c). This superior device performance was primarily attributed to the seamless formation of HfO2 on the TMD channels with a well-preserved vdW interface, which suppressed defect formation. The reproducibility of the vdW interface-integrated FETs was demonstrated by the consistent results observed in 40 MoS2 and WSe2 FETs, all fabricated using the same process (Fig. 3c and Supplementary Fig. 23). The stability and reliability of the fabricated FETs were further corroborated by time-dependent electrical performance and bias–temperature stress durability (Supplementary Figs. 24 and 25).

a Schematic of the top-gated FETs fabricated with the vdW interface-integrated HfO2/TMD (MoS2, WSe2) gate stack (≈5 nm MoS2 and WSe2, ≈10 nm HfO2; Channel length and width are 3 µm, respectively). b Extracted interface charge trap density (Dit) as a function of frequency using the conduction method from multi-frequency capacitance–voltage measurements. c Cumulative transfer characteristics of 40 MoS2 nFETs and WSe2 pFETs with the median transfer curves highlighted (at VDS = \(\pm\)0.5, respectively). Note that all the devices were measured at gate voltage sweeping speed of 0.025 V/s. Both MoS2 nFET and WSe2 pFET exhibit the near-ideal subthreshold swings (61 mV/dec and 63 mV/dec, respectively, at 300 K) with low gate leakage current of ≈10-13 A. IDS and IGS denote the drain and gate currents, respectively, while VDS and VGS represent the drain-to-source and gate-to-source voltages. SS refers to the subthreshold swing. d–f The full view (d) and enlarged view (e, f) of the dual sweep transfer curves measured at various gate-voltage sweeping speeds, indicating negligible hysteresis of ≈3 mV (Inset: enlarged view of measured hysteresis under gate sweep rate of 0.01 V/s). g–i The full view (g) and enlarged view (h, i) of the dual sweep transfer curves under different gate-voltage sweeping ranges, also exhibiting small hysteresis of ≈3 mV (Inset: enlarged view of measured hysteresis under gate sweep range; −0.5 V to 0.8 V, and 0.5 V to −0.8 V, respectively).

Gate hysteresis is another critical device parameter closely related to the interface quality and defects within the dielectric layer47,48. The hysteresis of the MoS2 nFET and WSe2 pFET was evaluated under varying gate sweeping rates from 0.01 to 0.1 V/s (Fig. 3d). The negligible hysteresis (≈3 mV) indicates that the trap states at the vdW interface and within the HfO2 dielectric were suppressed (Fig. 3e, f). This performance demonstrates an improvement over recently reported vdW interface-integrated high-κ dielectrics on a 2D semiconductor, including GdOCl/MoS2 (≈5 mV), HfO2/MoS2 (≈10 mV), Al2O3/MoS2 (≈10 mV), and Ga2O3/MoS2 (≈60 mV)37,43,49,50. Furthermore, both the MoS2 nFET and WSe2 pFET demonstrated SS values approaching the Boltzmann limit across all sweep rates without degradation over four orders of IDS. Similar results were observed for various gate-sweeping ranges (Fig. 3g–i). Device simulations incorporating various process nodes were also conducted to investigate the SS and on–off ratio variations of the proposed FETs with respect to the different Dit values (Supplementary Table 3 and Supplementary Figs. 26a and 27). These findings confirm that the proposed vdW integration offers a universal and scalable approach for delivering consistent and predictable performances in 2D semiconductor-based electronics, underscoring its potential for the construction of future low-power complementary logic gates.

3D integrated CFET inverter

Recent advancements, including innovative approaches that leverage monolithic 3D integration, have highlighted the feasibility of 2D semiconductor-based vertical CMOS technology51,52,53,54,55,56,57,58. However, the interfacial degradation associated with integrating conventional high-κ dielectrics and 2D semiconductors remains a critical challenge, limiting the performance of future 3D CMOS integrated circuits. In this study, we demonstrate the feasibility of CFETs by sequentially stacking vdW interface-integrated FETs. A schematic of the 3D structure of the proposed CFET, where the top MoS2 nFET and bottom WSe2 pFET are vertically interconnected, is shown in Fig. 4a (see Supplementary Figs. 1, 28 and 29 for details). In this configuration, the MoS2 nFET and WSe2 pFET share a common gate, and the sources are connected to the same metal pad to form a 3D integrated CMOS inverter. The common gate functions as the input voltage (VIN), whereas the connected drains of the nFET and pFET serve as the output voltage (VOUT). Importantly, in the proposed vdW integration system with a high-κ dielectric, the voltage transfer characteristics of the CFET show highly sharp voltage transitions at different supply voltages (VDD) ranging from 0.5 to 2.0 V (Fig. 4b). VOUT is high (logic ‘1’) when VIN is low (logic ‘0’), and VOUT is reduced to a low level (logic ‘0’) when VIN increases (logic ‘1’), demonstrating an ideal logic functionality. The high VOUT near VDD and low VOUT of ≈0.1 mV indicate a well-matched voltage between the two FETs and their low leakage currents, as discussed in the previous section. The voltage gain is boosted with the increase of VDD and reaches a peak value of ≈115 at VDD = 2.0 V (Fig. 4c). In particular, acceptable voltage gains at a scaled VDD of 0.5 V satisfied the minimum requirement for ultralow-power logic applications1,59,60,61,62. Furthermore, the proposed CFET exhibited superior gain and a low-voltage operation capability compared to previously reported CFETs (Fig. 4d). The inverter gain of the fabricated CFET at various supply voltages is among the highest values reported for comparable architectures to date, including conventional Si channels63,64, 2D-Si hybrid channels65,66, and all 2D configurations53,54,67,68,69,70 (also in Supplementary Table 1). The demonstrated voltage gain is essential for signal transmission and logic operations in 3D integrated circuits. Similar results were consistently obtained for 10 CFETs integrated using the same fabrication process (Supplementary Fig. 30). The noise margin is another crucial parameter related to stable inverter operation and desirable circuit performance, and it defines the tolerance of the output signal to the signal interference at the input. The enhanced noise margin derived from the sharp and narrow transition in the voltage transfer characteristics was demonstrated (Fig. 4e). The input voltage is defined as logic high (‘1’) when VIN < VIH and logic low (‘0’) when VIN > VIL, indicating the clear and distinct output logic level in the proposed CFET operation. VOH and VOL represent the ideal logic high and logic low levels of the CFET, respectively. Consequently, the high noise margin (NMH) and low noise margin (NML) were calculated by NMH = VOH - VIH and NML = VIL - VOL, resulting in NMH = 0.975 V (97.5% of 1/2VDD) and NML = 0.985 V (98.5% of 1/2VDD), respectively. Both values approached the ideal noise margin (1/2VDD), indicating the high noise tolerance of the vdW interface-integrated CFET. Moreover, all noise margins exceeded 90% at various supply voltages, further indicating the robustness of the proposed CFETs for multistage operation (Supplementary Fig. 31). The static power consumption of the CFET as a function of VDD is shown in Fig. 4f. Notably, a low peak static power of ≈19 pW at VDD = 0.5 V was demonstrated, which is the most important characteristic of low-power CMOS logic circuits. The proposed CFET demonstrated significantly reduced static power dissipation compared to currently reported CMOS technologies, including both vertical and planar architectures utilising various channel materials (2D channels, 2D/Si hybrid channels, organic channels, and GaN) with enhanced energy efficiency (Fig. 4g and Supplementary Table 1)65,66,67,68,69,70,71,72,73,74. Device simulations based on the proposed structure demonstrated compatibility with current process nodes1, highlighting its potential for energy-efficient, low-power applications in 3D integrated circuits (Supplementary Table 4 and Supplementary Figs. 26b and 32).

a Structural schematic of the CFET. GND, VIN, VDD and VOUT represent ground, input voltage, supply voltage and output voltage for the CFET, respectively. b, c Voltage transfer characteristics and the corresponding voltage gain as a function of VDD. d The voltage gain comparison of the CFETs fabricated with 2D semiconductor/Si hybrid channel, 2D semiconductor channel, and Si channel, including proposed vdW interface-integrated CFET53,54,63,64,65,66,67,68,69,70. e Voltage transfer characteristic and its mirror reflection at VDD = 2.0 V. VOH, VOL, VIL, and VIH represent the minimum high output voltage, maximum low output voltage, maximum low input voltage, and minimum high input voltage, respectively. The noise margin is determined by nesting the largest square (grey shaded area). The dashed lines (black) are auxiliary lines for extracting the value of VOH, VOL, VIL, and VIH. f Static power consumption of the proposed CFET as a function of VDD. IDD denotes the supply current. g Comparison of static power consumption at various VDD with literature reports65,66,67,68,69,70,71,72,73,74.

RO integrated with CFETs

Here, we present CFET-integrated ROs, demonstrating a 3D CMOS architecture incorporating 2D semiconductors with the potential for low-power and high-performance computing. A schematic and the corresponding circuit diagram of the five-stage RO are shown in Fig. 5a. The RO was realised by cascading five CFET inverters in a closed-loop configuration. An additional inverter stage served as a readout buffer to isolate the oscillator operation from the measurement setup, ensuring accurate signal extraction without interference. The same configuration applies to the three-stage RO (see Methods and Supplementary Figs. 1 and 33 for details). Figure 5b shows the output oscillation signals of the three- and five-stage ROs measured at VDD = 2.0 V. Both configurations exhibited stable and periodic oscillation with suppressed signal loss. Furthermore, consistent results were also achieved under various supply voltages varying from 0.5 to 2.0 V (Fig. 5c and Supplementary Fig. 34). This is attributed to high-quality vdW interface-integrated FETs and their seamless extension into vertically interconnected high-performance CFET architectures. The corresponding propagation delay time per stage, defined as τpd = 1/2Nf (where N is the number of RO stages and f is the oscillation frequency) at VDD = 2.0 V was ≈1.83 and ≈1.85 ns for the three- and five-stage ROs, respectively. The similar τpd values of these ROs further indicate their stability and robustness. Moreover, the fabricated ROs demonstrated a competitive advantage with low driving voltages and fast propagation stage delay times compared to previously reported ROs fabricated with various 2D semiconductors, organic materials, CNT, oxides, and Si/GaN channels (Fig. 5d and Supplementary Table 2), outperforming the reported experimental results63,67,73,74,75,76,77,78,79,80,81,82. Further optimisation, including the suppression of parasitic capacitances, reduction of contact resistance, and aggressive gate-length scaling is expected to further enhance the signal delivery and overall performance, achieving levels comparable to those of advanced technology nodes (Supplementary Fig. 35).

a Schematic and the corresponding circuit diagram of the five-stage ring oscillator (RO). b Output signals of three- and five-stage ROs operated at VDD = 2.0 V. c Summarised output frequencies with the corresponding propagation delay times per stage as a function of VDD. The oscillation frequency increases with VDD, exhibiting typical RO behaviour. Maximum/minimum frequencies are 91.5 MHz/52.4 MHz for the three-stage RO, and 53 MHz/32.42 MHz for the five-stage RO, respectively. Both ROs exhibit similar propagation-stage delay times at the same VDD, with the delay time reduced to ≈1.83 ns at VDD = 2.0 V. d Comparison of propagation-stage delay time versus VDD with literature reports (circle three-stage, up-triangle: five-stage, square: seven-stage, pentagon: eleven-stage, diamond: fifteen-stage, hexagon: seventeen-stage)63,67,73,74,75,76,77,78,79,80,81,82.

Discussion

We report universal high-κ dielectric integration with a high-quality vdW interface by converting the transferred HfSe2 on MoS2 and WSe2 into HfO2 via controllable plasma oxidation, preserving the clean vdW interface and channel properties. Atomically flat vdW interfaces of the HfO2/MoS2 and HfO2/WSe2 heterostructures with suppressed Dit values of ≈7.1 × 1010 and ≈8.4 × 1010 cm−2 eV−1 were demonstrated. Consequently, the fabricated MoS2 nFET and WSe2 pFET exhibited near-ideal SS values of 61 and 63 mV/dec, respectively, over four orders of IDS at room temperature (300 K), which is close to the Boltzmann limit, along with a high on–off ratio (≈108) and small hysteresis (≈3 mV).

Based on first-principles molecular dynamics simulations, we provided mechanistic explanations for why the oxygen plasma-induced HfSe2-to-HfO2 conversion serves as a universal strategy for establishing atomically clean vdW HfO2/TMD interfaces and is particularly effective for preparing HfO2/MoS2 and HfO2/WSe2 interfaces.

The vdW interface-integrated CFET, in which the MoS2 nFET and WSe2 pFET were sequentially stacked, demonstrated a high voltage gain (≈115) and low static power dissipation (≈19 pW). Furthermore, the ROs integrated with CFETs demonstrated an enhanced propagation delay time per stage (≈1.83 ns), indicating their potential for high-frequency circuit applications. Our findings provide a pathway toward a broadly applicable framework for integrating high-κ dielectrics with diverse 2D semiconductors through atomically defined vdW interfaces. This approach can be extended to a wide range of material systems and device architectures, offering a versatile platform for future 2D semiconductor-based 3D logic and memory technologies aimed at enhanced scalability and energy-efficient computing.

Methods

Fabrication of the HfO2/TMD heterostructure

The exfoliation and transfer processes were performed in a glove box in a controlled environment to prevent external perturbations (where both the O2 and H2O concentrations were <0.1 ppm). The thickness of the material was first identified using an optical microscope, and then accurately determined using an atomic force microscope. MoS2 and WSe2 were first transferred onto a SiO2/Si substrate, followed by transferring HfSe2. Then, O2 plasma oxidation was performed under fixed conditions (a power of 10 W, flow rate of 5 sccm, and pressure of 470 mTorr) for HfO2 formation as a high-κ gate dielectric with an atomically flat vdW interface. The polymethyl methacrylate (PMMA) layers were spin-coated at 2000 rpm for 5 s and 4000 rpm for 35 s. Each layer was baked at 180 °C for 2 min on a hot plate. Electron-beam lithography (EBL) and electron-beam deposition were used to form source/drain and top-gate electrodes with Au in a high-vacuum chamber (5 × 10−7 Torr).

Fabrication of FET

MoS2 and WSe2 flakes (≈5 nm) were exfoliated using Scotch tape and subsequently dry-transferred onto a SiO2/Si substrate. Source and drain electrodes were defined using standard EBL, followed by the deposition of 10-nm Au metal. After lifting off the metal in acetone, HfSe2 (≈25 nm) was dry-transferred and oxidised for 5 min to form HfO2 layers (≈10 nm) under the given plasma conditions. The top gate was patterned, and a 30-nm Au layer was deposited to serve as the top gate electrode.

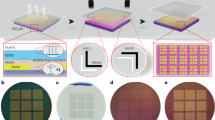

Fabrication of CFET and RO

For the CFET, the bottom WSe2 pFET was fabricated using the same procedure as the FET described above. The fabricated HfO2/MoS2 heterostructure was then transferred onto the top gate of the WSe2 pFET via an advanced transfer method using PMMA-coated PDMS considering adhesion and annealed for 30 min to release the HfO2/MoS2 heterostructure via the full decomposition of the PMMA layer. Au source and drain electrodes were then patterned and deposited. In this configuration, the common gate functions as VIN, whereas the connected drains serve as VOUT. These sources act as VDD and GND, respectively. For the ROs, the single-stage fabrication process was identical to that used for the CFETs in both the three- and five-stage designs. To connect each stage, the VOUT of each stage was connected to the VIN of the next stage, and all VDD and GND systems were linked using the same metal pad. Additionally, to reduce the interference between the closed loop and measurement setup, VOUT was connected to an additional readout buffer stage.

Sample characterisation

OM (Olympus, BX51M) and FE-SEM (JEOL, JSM7500F) were used to observe the sizes and colours of the prepared samples and fabricated devices. Raman spectroscopy at an excitation wavelength of 523 nm was used to characterise MoS2, WSe2, and the fully converted HfO2. The thickness of the flakes was determined using an atomic force microscope (Park Systems Corp., NX-10) in the non-contact mode with PPP-NCHR probe tips (nanosensors). The cross-sections were observed using transmission electron microscopy (TEM, JEOL, TEM2100F) at an accelerating voltage of 200 kV.

Electrical characterisation

All the electrical measurements were performed in a probe station (MSTECH) with a vacuum pressure of 10-6 Torr using a semiconductor analyser (Keithley 4200) and an oscilloscope (Tektronix TBS1154). A Keithley 4200 instrument was used to provide the supply voltage to all the devices in this study. A Tektronix TBS1154 instrument was used to measure the output waveforms of the vdW interface-integrated ROs.

Computational details

DFT calculations were performed using the VASP package with the projected augmented wave method83. Many-electron exchange-correlation interactions were treated within the Perdew-Burke-Ernzerhof form of generalised gradient approximation84. The weak long-range dispersion interactions were described within the Grimme’s DFT-D3 method85. The kinetic energy cut-off for the plane wave basis was set at 500 eV, and the 2×4×1 Monkhorst–Pack k-point samplings were used in the structural relaxation for 2D planar structures of TMDs. The atomic structures were optimised until the total energy and the Hellmann-Feynman forces on each atom reached the 10-4 eV and 0.01 eV/Å levels, respectively. AIMD simulations were performed by iterative NVE-NVT dynamics. NVE ensemble dynamics runs a few ps (less than 5 ps) until local configuration of oxygen does not change and NVT ensemble dynamics runs for 1 ps with a Nosé–Hoover thermostat to quench the system to 500 K. Throughout the AIMD procedure, a time step of 1 fs was used, and Brillouin zone sampling was restricted to the Γ-point.

TCAD simulations

Device analysis was performed using Synopsys Sentaurus (Synopsys Inc., Mountain View, CA, USA), a 3D technology computer-aided design (TCAD) software package.

Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

References

More Moore table. (page 13, Table MM9) International Roadmap for Devices and Systems IRDS 2022 More Moore (ieee.org) (2022).

Cao, W. et al. The future transistors. Nature 620, 501–515 (2023).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Wang, S. et al. Two-dimensional devices and integration towards the silicon lines. Nat. Mater. 21, 1225–1239 (2022).

Pal, A. et al. Three-dimensional transistors with two-dimensional semiconductors for future CMOS scaling. Nat. Electron. 7, 1147–1157 (2024).

Jayachandran, D. et al. 3D integration of 2D electronics. Nat. Rev. Electr. Eng. 1, 300–316 (2024).

Kim, K. S. et al. The future of two-dimensional semiconductors beyond Moore’s law. Nat. Nanotechnol. 19, 895–906 (2024).

Akinwande, D. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat. Electron. 2, 372–381 (2019).

Wang, Y. et al. Critical challenges in the development of electronics based on two-dimensional transition metal dichalcogenides. Nat. Electron. 7, 638–645 (2024).

Yang, S. et al. Gate dielectrics integration for two-dimensional electronics: challenges, advances and outlook. Adv. Mater. 35, 2207901 (2023).

Park, J. et al. Area-selective atomic layer deposition on 2D monolayer lateral superlattices. Nat. Commun. 15, 2345 (2024).

Huang, B. et al. Atomic layer deposition of high-quality Al₂O₃ thin films on MoS₂ with water plasma treatment. ACS Appl. Mater. Interfaces 11, 35438–35443 (2019).

Schwartzberg, A. M. & Olynick, D. Complex materials by atomic layer deposition. Adv. Mater. 27, 5778–5784 (2015).

Azcatl, A. et al. MoS2 functionalization for ultra-thin atomic layer deposited dielectrics. Appl. Phys. Lett. 104, 111601 (2014).

Cheng, L. et al. Atomic layer deposition of a high-κ dielectric on MoS2 using trimethylaluminum and ozone. ACS Appl. Mater. Interfaces 6, 11834–11838 (2014).

McDonnell, S. J. & Wallace, R. M. UV-ozone functionalization of 2D materials. JOM 71, 224–237 (2019).

Xiao, M. et al. Atomic-layer-deposition growth of an ultrathin HfO2 film on graphene. ACS Appl. Mater. Interfaces 9, 34050–34056 (2017).

Choi, M. S. et al. Chemical dopant-free doping by annealing and electron beam irradiation on 2D materials. Adv. Electron. Mater. 7, 2100449 (2021).

Zhang, F. et al. Dielectric integrations and advanced interface engineering for 2D field-effect transistors. Small Methods 8, 2402187 (2024).

Leonhardt, A. et al. Material-selective doping of 2D TMDC through AlxOy encapsulation. ACS Appl. Mater. Interfaces 11, 42697–42707 (2019).

White, M. H. & Cricchi, J. R. Characterization of thin-oxide MNOS memory transistors. IEEE Trans. Electron Devices 19, 1280–1288 (1972).

Rzepa, G. et al. A compact-physics framework for unified modeling of BTI. Microelectron. Reliab. 85, 49–65 (2018).

Xu, Y. et al. Scalable integration of hybrid high-κ dielectric materials on two-dimensional semiconductors. Nat. Mater. 22, 1078–1084 (2023).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Kang, T. et al. High-κ dielectric (HfO2)/2D semiconductor (HfSe2) gate stack for low-power steep-switching computing devices. Adv. Mater. 36, 2312747 (2024).

Zhang, Y. et al. A single-crystalline native dielectric for two-dimensional semiconductors with an equivalent oxide thickness below 0.5 nm. Nat. Electron. 5, 643–649 (2022).

Tan, C. et al. 2D fin field-effect transistors integrated with epitaxial high-κ gate oxide. Nature 616, 66–72 (2023).

Yu, M. et al. Integrated 2D multi-fin field-effect transistors. Nat. Commun. 15, 3622 (2024).

Liu, C. et al. Controllable van der Waals gaps by water adsorption. Nat. Nanotechnol. 19, 448–454 (2024).

Satterthwaite, P. F. et al. Van der Waals device integration beyond the limits of van der Waals forces using adhesive matrix transfer. Nat. Electron. 7, 17–28 (2024).

Zhang, Y. et al. Van der Waals-interface-dominated all-2D electronics. Adv. Mater. 34, 2207966 (2022).

Rasool, H. I. et al. A comprehensive review on recent advances in two-dimensional (2D) hexagonal boron nitride. ACS Appl. Electron. Mater. 3, 3975–4004 (2021).

Wang, Y. et al. Ultraflat single-crystal hexagonal boron nitride for wafer-scale integration of a 2D-compatible high-κ metal gate. Nat. Mater. 23, 1495–1501 (2024).

Zhang, C. et al. Single-crystalline van der Waals layered dielectric with high dielectric constant. Nat. Mater. 22, 1078–1084 (2023).

Zeng, D. et al. Single-crystalline metal-oxide dielectrics for top-gate 2D transistors. Nature 632, 788–794 (2024).

Yao, Z. et al. Transferrable, wet-chemistry-derived high-κ amorphous metal oxide dielectrics for two-dimensional electronic devices. Nat. Commun. 16, 1482 (2025).

Lu, Z. et al. Wafer-scale high-κ dielectrics for two-dimensional circuits via van der Waals integration. Nat. Commun. 14, 2340 (2023).

Wang, L. et al. A general one-step plug-and-probe approach to top-gated transistors for rapidly probing delicate electronic materials. Nat. Nanotechnol. 17, 1206–1213 (2022).

Venkatakrishnarao, D. et al. Liquid metal oxide-assisted integration of high-κ dielectrics and metal contacts for two-dimensional electronics. ACS Nano 18, 26911–26919 (2024).

Yan, Y. et al. CMOS-compatible fabrication of 2D semiconductor-based CFETs via high-κ dielectric van der Waals encapsulation. Nano Lett. 25, 6125–6133 (2025).

Sebek, M. et al. Van der Waals enabled formation and integration of ultrathin high-κ dielectrics on 2D semiconductors. npj 2. D. Mater. Appl. 8, 9 (2024).

Zhang, M. et al. Integration of ultrathin hafnium oxide with a clean van der Waals interface for two-dimensional sandwich heterostructure electronics. Nano Lett. 24, 1234–1240 (2024).

Luo, P. et al. Molybdenum disulfide transistors with enlarged van der Waals gaps at their dielectric interface via oxygen accumulation. Nat. Electron. 5, 849–858 (2022).

Cvitkovich, L. et al. Dynamic modeling of Si(100) thermal oxidation: oxidation mechanisms and realistic amorphous interface generation. Appl. Surf. Sci. 610, 155378 (2023).

Jech, M. et al. Ab initio treatment of silicon–hydrogen bond rupture at Si/SiO2 interfaces. Phys. Rev. B 100, 195302 (2019).

Lai, S. et al. HfO2/HfS2 hybrid heterostructure fabricated via controllable chemical conversion of two-dimensional HfS2. Nanoscale 10, 18758–18766 (2018).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Illarionov, Y. Y. et al. Energetic mapping of oxide traps in MoS2 field-effect transistors. 2D Mater. 4, 025108 (2017).

Xu, W. et al. Single-crystalline high-κ GdOCl dielectric for two-dimensional field-effect transistors. Nat. Commun. 15, 9469 (2024).

Yi, K. et al. Integration of high-κ native oxides of gallium for two-dimensional transistors. Nat. Electron. 7, 1126–1136 (2024).

Kim, K. S. et al. Growth-based monolithic 3D integration of single-crystal 2D semiconductors. Nature 636, 615–621 (2024).

Lu, D. et al. Monolithic three-dimensional tier-by-tier integration via van der Waals lamination. Nature 630, 340–345 (2024).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Pendurthi, R. et al. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. Nat. Nanotechnol. 19, 742–749 (2024).

Ghosh, S. et al. Monolithic and heterogeneous three-dimensional integration of two-dimensional materials with high-density vias. Nat. Electron. 7, 768–776 (2024).

Kang, J.-H. et al. Monolithic 3D integration of 2D materials-based electronics towards ultimate edge computing solutions. Nat. Mater. 22, 1470–1477 (2023).

Xie, M. et al. Monolithic 3D integration of 2D transistors and vertical RRAMs in 1T–4R structure for high-density memory. Nat. Commun. 14, 5952 (2023).

Ran, Y. et al. Monolithic 3D logic gates based on p-Te and n-Bi2S3 complementary thin-film transistors. Adv. Electron. Mater. 11, 2400786 (2025).

International Technology Roadmap for Semiconductors (ITRS). ITRS 2.0 Executive Report (Semiconductor Industry Association, 2015).

Alioto, M. Ultra-low power VLSI circuit design demystified and explained: a tutorial. IEEE Trans. Circuits Syst. I 59, 3–29 (2012).

Roy, K. et al. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 91, 305–327 (2003).

Manfredini, G. et al. Ultra-low-voltage inverter-based amplifier with novel common-mode stabilization loop. Electronics 9, 1019 (2020).

Chang, S.-W. et al. First demonstration of CMOS inverter and 6T-SRAM based on GAA CFETs structure for 3D-IC applications. In Proc. IEEE Int. Electron Devices Meeting (IEDM) (IEEE, 2019).

Chang, S.-W. et al. First demonstration of heterogeneous IGZO/Si CFET monolithic 3D integration with dual work function gate for ultralow-power SRAM and RF applications. In Proc. IEEE Int. Electron Devices Meeting (IEDM) (IEEE, 2022).

Tong, L. et al. Heterogeneous complementary field-effect transistors based on silicon and molybdenum disulfide. Nat. Electron. 6, 37–44 (2023).

Guan, S.-X. et al. Monolithic 3D integration of back-end compatible 2D material FET on Si FinFET. npj 2D Mater. Appl. 7, 9 (2023).

Xiong, X. et al. Top-gate CVD WSe2 pFETs with record-high Id ~594 uA/um, Gm~244 uS/um and WSe2/MoS2 CFET-based half-adder circuit using monolithic 3D integration. In Proc. IEEE Int. Electron Devices Meeting (IEDM) (IEEE, 2022).

Jia, X. et al. High-performance CMOS inverter array with monolithic 3D architecture based on CVD-grown n-MoS2 and p-MoTe2. Small 19, 2207927 (2023).

Ran, Y. et al. Large-scale vertically interconnected complementary field-effect transistors based on thermal evaporation. Small 20, 2309953 (2024).

Guo, Y. et al. Van der Waals polarity-engineered 3D integration of 2D complementary logic. Nature 630, 340–345 (2024).

Pezeshki, A. et al. Static and dynamic performance of complementary inverters based on nanosheet α-MoTe2 p-channel and MoS2 n-channel transistors. ACS Nano 10, 1118–1125 (2016).

Lim, J. Y. et al. Homogeneous 2D MoTe2 p–n junctions and CMOS inverters formed by atomic-layer-deposition-induced doping. Adv. Mater. 29, 1701798 (2017).

Guo, E. et al. Integrated complementary inverters and ring oscillators based on vertical-channel dual-base organic thin-film transistors. Nat. Electron. 4, 588–594 (2021).

Zheng, Z. et al. Gallium nitride-based complementary logic integrated circuits. Nat. Electron. 4, 595–604 (2021).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Tang, J. et al. Low power flexible monolayer MoS2 integrated circuits. Nat. Commun. 14, 3633 (2023).

Li, N. et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 3, 711–717 (2020).

Lei, T. et al. Low-voltage high-performance flexible digital and analog circuits based on ultrahigh-purity semiconducting carbon nanotubes. Nat. Commun. 10, 2161 (2019).

Zhong, D. et al. Gigahertz integrated circuits based on carbon nanotube films. Nat. Electron. 1, 40–45 (2018).

Borchert, J. W. et al. Flexible low-voltage high-frequency organic thin-film transistors. Sci. Adv. 6, eaaz5156 (2020).

Kim, Y.-H. et al. Flexible metal-oxide devices made by room-temperature photochemical activation of sol–gel films. Nature 489, 128–132 (2012).

Mourey, D. A. et al. Self-aligned-gate ZnO TFT circuits. In Proc. IEEE Int. Electron Devices Meeting (IEDM) (IEEE, 2010).

Kresse, G. & Furthmüller, J. Efficient iterative schemes for ab initio total-energy calculations using a plane-wave basis set. Phys. Rev. B 54, 11169–11186 (1996).

Perdew, J. P. et al. Generalized gradient approximation made simple. Phys. Rev. Lett. 77, 3865–3868 (1996).

Grimme, S. et al. Effect of the damping function in dispersion corrected density functional theory. J. Comput. Chem. 32, 1456–1465 (2011).

Acknowledgements

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea and was funded by the Korean Government (MSIP) (Grant Nos. RS-2023-00281048, 2022R1A2C3003068, RS-2023-NR077013). This work was supported by Samsung Research Funding & Incubation Center of Samsung Electronics under Project Number SRFC-MA2501-01. This study was supported by Samsung Electronics Co. Ltd. This work was also supported by the National Supercomputing Center with supercomputing resources including technical support (KSC-2024-CRE-0536).

Author information

Authors and Affiliations

Contributions

T.K. conceived the experimental design, prepared the materials, and performed most of the device fabrication and characterisation, with assistance from S.-Y.L. Y.-H.K. and J.P. performed the ab initio molecular dynamics simulations and contributed to the mechanistic interpretation of the oxidation process. J.J. and H.J. carried out the device simulations and assisted in analysing the electrical characteristics. T.K. and S.L. wrote the manuscript with input and discussion from all authors. All authors reviewed and commented on the manuscript. S.L. supervised the overall project.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Communications thanks Donglin Lu, Laiyuan Wang, and the other, anonymous, reviewerfor their contribution to the peer review of this work. A peer review file is available.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Kang, T., Park, J., Lee, S.Y. et al. High-κ dielectric van der Waals integration on 2D semiconductors for three-dimensional complementary logic systems. Nat Commun 16, 11648 (2025). https://doi.org/10.1038/s41467-025-66770-0

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41467-025-66770-0