Abstract

In recent years, DC microgrids supplying constant power loads (CPLs) have attracted significant attention due to their impact on overall system stability, which is attributed to their electrical characteristics that exhibit negative incremental impedance. This paper examines a secondary control strategy aimed at ensuring accurate power sharing and voltage restoration within an islanded DC microgrid supplying a constant power load. The droop control function is typically used in the primary control layer to facilitate power sharing among distributed generators (DGs). However, differing load profiles may cause the DC bus voltage to deviate from its nominal value. To restore the DC bus voltage to its nominal value while maintaining accurate power sharing, a primary and secondary control scheme is proposed. This scheme employs an integrated control strategy combining sliding mode control for the primary control level and H-infinity control for secondary control. The approach is based on a two-time-scale stability analysis, i.e., the settling time of the primary control must be faster than that of the secondary control. Additionally, compared to most existing methods, the proposed approach requires no global information and depends exclusively on DC bus voltage feedback, eliminating the need for passive loads in parallel with the CPL. A test system of an islanded DC microgrid feeding a CPL is created using Matlab and PSIM software to assess the proposed method. An experimental prototype comprising two DGs and a tightly voltage-controlled boost converter emulating a CPL is developed to demonstrate the proposed approach and confirm the theoretical results.

Similar content being viewed by others

Introduction

The growing demand for efficient, reliable, and sustainable energy systems has driven significant interest in innovative power generation and distribution methods. The integration of renewable energy sources, combined with advancements in power electronics and digital controllers, has accelerated the adoption of distributed generation and microgrid (MG) technologies. This shift not only supports a diversified energy mix but also enables localized energy production, enhancing system reliability and reducing transmission losses, making MGs a key component in the development of modern energy infrastructure. MGs integrate distributed generation units (DGs), energy storage systems, and local loads, forming a flexible and resilient power structure. This design enhances energy management and improves system stability, particularly when integrating variable renewable sources such as solar and wind power1,2.

MGs are categorized based on the type of coupling bus: alternating current (AC) MGs, direct current (DC) MGs, and hybrid AC/DC MGs. Each configuration is suited to specific applications and operational requirements, providing flexibility that enables MGs to play a critical role in advancing renewable integration and enhancing grid reliability within modern power systems3,4.

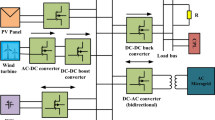

This paper primarily focuses on DC MGs, particularly those supplying constant power loads (CPLs). These systems typically operate in an islanded mode, as shown in Fig. 1. DC MGs are especially well-suited for applications where precise load control and stability are crucial, offering a practical and efficient solution for integrating renewable energy while maintaining system reliability5,6,7.

Typical DC microgrid with CPLs.

In islanded DC MGs, droop control is commonly used within the local controllers of DGs to achieve balanced power sharing. This decentralized approach allows each DG to produce an equal current output, effectively distributing the load across the system without requiring inter-unit communication. However, the implementation of droop control introduces a trade-off between power-sharing accuracy and voltage regulation. While it improves load sharing, droop control often compromises voltage regulation, causing the DC bus voltage to deviate significantly from its desired reference value. External disturbances and the influence of CPLs exacerbate voltage deviations, making it challenging to maintain the stability of the DC bus at its desired level8,9,10.

To address these limitations, a secondary control strategy is introduced for DC MGs supplying CPLs. This strategy includes a secondary voltage compensation controller specifically designed to enhance voltage regulation and ensure system stability. In this approach, the voltage deviation error is detected and processed by an appropriate controller, which then sends a corrective control signal to all DGs to maintain the desired voltage11,12,13,14.

Despite these advancements, certain challenges remain. A suitable model must be developed to effectively design the controller and mitigate the destabilizing effects of CPLs, which are known to be a source of instability in DC MGs when the controller is insufficient. In particular, CPLs are nonlinear loads that exhibit incremental negative impedance (INI) characteristics, meaning that a decrease in output voltage leads to an increase in output current, and an increase in voltage causes a reduction in current. This nonlinear behavior complicates control efforts, as it requires a specific strategy to stabilize the common DC bus of the DC MG15. CPLs are prevalent in applications such as aircraft, electric vehicles, ships, and telecommunications, highlighting the need for robust control to manage their effects and ensure stability in DC MGs16,17.

The presence of CPLs in DC MGs produces instability, irised by the INI effect, destabilizing the system and causing issues with voltage stabilization and power sharing among DGs. The complex dynamics of hierarchical control and CPLs complicate stability analysis, requiring advanced control strategies to maintain stable operation and ensure balanced power distribution. Various solutions have been proposed to address these challenges, and the following literature review investigates these strategies and their effectiveness in enhancing stability and power sharing in DC MGs. In18, a comprehensive review of hierarchical control strategies for DC MGs is presented, emphasizing the importance of secondary control in maintaining voltage stability and power balance under varying load conditions. The authors in19 propose a secondary control method for standalone DC MGs that enhances voltage regulation, load sharing, and reduces line losses, thereby improving overall system performance. In20, the challenges posed by CPLs in droop-controlled DC MGs are addressed, suggesting methods to mitigate instability and ensure robust operation. In21, the authors introduce a cooperative decentralized tertiary control approach for DC MGs with renewable distributed generation, focusing on coordinated voltage regulation and power sharing among multiple energy sources. In22, the authors analyze CPLs in droop-controlled MGs for more electric aircraft applications, highlighting the need for robust control strategies to maintain system stability.

A novel secondary optimal control is developed in23 for multiple battery energy storage systems in a DC MG, aiming to improve voltage stability and efficient power management. A distributed secondary control method is proposed in24, using averaging virtual current derivatives to improve voltage regulation and system resilience against disturbances. An enhanced droop control method, presented in25, ensures accurate load sharing and voltage regulation in islanded and interconnected DC MGs, addressing issues related to proportional load distribution. The authors in26 utilize neural networks to achieve voltage recovery and current sharing in DC MGs with uncertain CPLs, demonstrating the potential of artificial intelligence in MG control. In27, a review of power sharing, voltage restoration, and stabilization techniques in hierarchical controlled DC MGs is provided, offering insights into various control methodologies and their effectiveness.

In28, the authors conduct control and stability analysis of DC MGs with CPLs and source disturbances, proposing strategies to enhance system robustness. The authors in29 assess the performance of reverse droop control for multi-DER cooperative DC MGs, offering solutions for improved voltage regulation and load sharing. A finite-time synergetic controller is proposed in30 for DC MGs with CPLs, achieving rapid system stabilization and improved dynamic response. An adaptive damping control is introduced in31 for load-side converters to mitigate instability in DC MGs caused by CPLs, enhancing system reliability. The authors in32 focus on the detection and mitigation of false data in cooperative DC MGs with unknown CPLs, ensuring data integrity and reliable operation. In33, the authors develop a stable and robust DC power system for more electric aircraft, addressing challenges unique to aviation applications. In34, the dynamic response of dual-active-bridge converters with CPLs under extended-phase-shift control is improved, enhancing performance under varying load conditions. In35, a deep learning controller is proposed for DC–DC buck–boost converters in wireless power transfer systems feeding CPLs, showcasing the integration of machine learning in power electronics control.

An improved droop control strategy is proposed in36 for accurate current sharing and DC-bus voltage compensation in DC MGs, addressing common issues in conventional droop control methods. In37,38, the authors focus on modeling and control of single-phase dual-active-bridge-based medium-voltage DC shipboard power systems, contributing to the development of reliable maritime MGs. A distributed control method is proposed in39 to ensure proportional load sharing and improve voltage regulation in low-voltage DC MGs, highlighting the benefits of decentralized control architectures. In40, voltage and frequency control of inverter-based weak low-voltage network MGs is explored, providing solutions for maintaining stability in such systems.

A decentralized control method is proposed in41 for low-voltage DC MGs, facilitating scalable and flexible MG operation. In42, the authors offer practical design considerations for current sharing control in parallel voltage regulator module applications, relevant to MG power distribution. A control strategy for islanded MGs with DC-link voltage control is presented in43, ensuring stable operation under islanded conditions. The authors in44 provide a general approach toward standardization in hierarchical control of droop-controlled AC and DC MGs, contributing to the harmonization of control strategies.

In45, the authors analyze the stability of DC MGs with CPLs under distributed control methods, offering insights into maintaining stability in the presence of CPLs. Distributed control and optimization in DC MGs are discussed in46, presenting methods to achieve optimal performance through decentralized control. A secondary control method for MGs based on distributed cooperative control of multi-agent systems is proposed in47, facilitating coordinated control actions among distributed energy resources. In48, the authors conduct a small-signal analysis of MG secondary control, considering communication time delays and addressing challenges related to information exchange in control systems. In49, a novel decentralized primary and distributed secondary control strategy for DC MGs with CPLs is proposed, providing a comprehensive approach to improving system resilience under the influence of CPLs. However, the stability of DC MGs feeding CPLs under multi-level distributed control remains insufficiently studied due to the complex interactions between hierarchical control systems and CPLs. This challenge leaves the detailed stability analysis of such systems an open problem for further research.

This paper investigates the stability of parallel buck converters in a DC MG supplying local CPLs, addressing their nonlinear behavior under hierarchical control for voltage stabilization and precise power sharing. A decentralized primary droop control is implemented, guided by a sliding mode controller (SMC) with an adjusted droop expression50,51. The secondary control employs an H-infinity controller to enhance power sharing and restore voltage52,53. A two-time-scale analysis is conducted to evaluate system stability, considering the dynamics of the converters, CPLs, and the controller. The proposed method is validated through simulations and experimental tests, confirming its effectiveness. The key contributions of this study are outlined as follows:

-

1.

Development of a decentralized primary control based on SMC.

-

2.

Design of a secondary H-infinity controller for precise power sharing and voltage stabilization in the DC MG.

-

3.

A two-time-scale stability analysis, considering converter dynamics, CPL behavior, and hierarchical control effects.

-

4.

Validation through simulations and experimental results.

The paper is organized as follows: in “Discussion and analysis of DC MG feeding a CPL” section examines a DC MG supplying a CPL. In “Primary control design for a DC microgrid with a CPL” section details the design of a primary SMC-based controller aimed at achieving power sharing between DGs. In “Secondary control strategy for a DC microgrid feeding a constant power load” section discusses the use of hybrid sliding mode H-infinity control to enhance system stability. Simulation results are presented in “Simulation results” section, with experimental findings in “Experimental validation” section. In “Conclusion” section concludes the paper.

Discussion and analysis of DC MG feeding a CPL

The dynamic interaction between the CPL and the DC MG can lead to large-signal oscillations, compromising system stability. Addressing this instability is crucial to ensure reliable and robust operation of the DC MG in the presence of a CPL. In continuous conduction mode (CCM), the input impedance behaves as a negative resistance when the frequency is below the voltage loop cut-off frequency of the DC MG. However, when the frequency exceeds the cut-off frequency, the input impedance transitions to behave like an inductance15.

The consumed power for a CPL is constant throughout the controller bandwidth, and its relationship is provided by:

where Pcpl is the power absorbed by the CPL, vdc_Bus is the input voltage and idc_Bus stands for the consumed current.

Deriving the current of the CPL with respect to its voltage and inverting the result yields to the expression of the incremental negative impedance of a CPL, as follows:

Thus

The INI characteristic of the CPL, highlighted in Eq. (3) and depicted in Fig. 2, introduces a − 180° phase lag in the Bode diagram, as shown in Fig. 3. From a control systems perspective, this phase lag causes instability when the output impedance of the source DC MG intersects with the input impedance of the CPL, especially when the cut-off frequency of the source DC MG is lower than that of the CPL. This instability impacts overall system performance and degrades power quality15.

Incremental negative-impedance behavior of a CPL.

Bode diagram behaviour of a DC MG feeding a CPL (vin_1,2 = 28 V, C1,2 = 1000 µF, Lo1 = 6 mH, Lo2 = 2.7 mH, Pcpl = 10:10:100 W, d = 0.5, RLine_1 = 1 Ω, RLine_2 = 2 Ω).

External variations, such as changes in power load demand and input voltage, can significantly impact system performance, particularly settling time and overshoot. To analyse these effects, a Bode analysis is performed on an open-loop DC MG feeding a CPL, where the power load demand is changed 10 times, incrementally increasing from 10 to 100 W. The results show that such variations reduce the system’s cut-off frequency and quality factor, leading to increased overshoot and a slower transient response. Based on this example analysis, a more comprehensive control strategy is required to manage power sharing and voltage regulation effectively in a DC MG with CPLs.

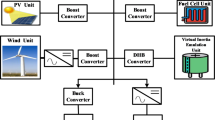

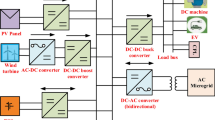

To manage power sharing and voltage regulation in a DC MG with CPLs, a two-level control strategy is employed. The primary control, often using droop control, balances power distribution among DG units but may lead to voltage deviations. To address these deviations, a secondary control level is added to enhance stability and performance, as shown in Fig. 4. The proposed approach is based on a two-time-scale stability analysis, where the settling time of the primary control is designed to be faster than that of the secondary control. This hierarchical structure ensures that the primary control layer is responsible for fast stabilization, local regulation of voltage and current, and balancing power among the DGs. Once the primary control achieves stability, the secondary control, operating on a slower time scale, performs higher-level tasks such as restoring the nominal DC bus voltage, achieving system-wide balance, and ensuring proper power sharing. This separation of time scales minimizes dynamic interactions between the control layers, enhancing the overall stability and robustness of the DC MG.

Parallel configuration of DC–DC converters supplying CPLs.

This coordinated control approach is particularly crucial for addressing the challenges posed by CPLs. The behavior of CPLs introduces instability-induced INI, which destabilizes the system by causing oscillations in the LC filters.

Traditional controllers designed for resistive loads struggle with the complexities introduced by CPLs, necessitating advanced control techniques. To address this, control loops (current and voltage) using an SMC are implemented for dynamic power sharing and voltage regulation in each DC–DC converter forming the MG. A secondary controller, featuring a PI controller enhanced by an H-infinity controller, is then developed to efficiently correct voltage deviations caused by the primary control and improve system stability50,51,52,53,54,55.

Primary control design for a DC microgrid with a CPL

Design of the inner loops (current–voltage) based on SMC

This section introduces a nonlinear control strategy to address instability and enhance the performance of the inner loops in each DC–DC converter forming the MG. To achieve this, a robust SMC is applied to the inner current–voltage control loops. Figure 5 illustrates the setup, featuring a DC MG supplying a CPL.

Primary control using SMC in a DC MG feeding a CPL.

The state-space model for a DG unit powering a CPL is derived and represented as:

where \(v_{in\_i}\) is the input voltage of the DG unit; \(v_{o\_i}\) represents the output voltage of the DG unit; \(L_{i} ,C_{i}\) are the parameters value of the LC filter of the DG unit; \(i_{L\_i}\) represents the inductor current of the DG unit; \(P_{cpl}\) is the CPL value.

A transformation method is used to reduce the number of state variables by selecting the output voltage and its derivative as the state variables x1_i and x2_i for each DG unit.

Substituting x1_i and x2_i into Eq. (4) provides an updated expression for each DG unit supplying a CPL. This transformation simplifies the control process, enhancing model clarity and control efficiency, as shown below:

where \(x_{1\_i}\) represents \(v_{o\_i}\), and \(x_{2\_i}\) represents \(\dot{v}_{o\_i}\).

In typical DC MG systems, the primary control level employs voltage and current controllers based on PI control. This section proposes an alternative approach that combines inner current–voltage loops into a unified control framework using SMC.

The SMC ensures that the output voltage of each DG unit in the DC MG accurately tracks the reference value, maintaining stable operation when connected to a CPL and improving robustness against disturbances50,51,55. Additionally, this method offers simplicity and ease of implementation, making it well-suited for control applications.

Therefore, we define the nonlinear switching surface function \(S_{i}\) as

where \(\lambda_{i}\) is a positive constant weight coefficient to adjust the convergence speed; \(\tilde{x}_{i}\) is the tracking error of each DG units representing the DC MG. nth-order \(S_{i}\) function.

By setting n = 1 and based on the dynamic model Eq. (5), the tracking error is defined as:

where \(x_{1\_i}\) and \(x_{2\_i}\) represent the output voltage of each DG unit of the DC MG, and its derivative, respectively.

By substituting Eqs. (4) and (7) into Eq. (6), it can be expressed as:

To derive the control law u(t) for the SMC, the switching control law is expressed as:

where \(k_{i}\) and \(q_{i}\) are positive constant coefficients.

Let us suppose the candidate Lyapunov function as:

Thus, based on Eqs. (9), (10), and (5), the derivative of the Lyapunov function must be negative when \(S \ne 0\).

The time derivative of \(V_{i}\) is given as:

To validate Eq. (9), the time derivative of Eq. (6) for each DG unit is given as:

By using Eq. (5), Eq. (12) becomes as follows:

To ensure stability, Eq. (11) is satisfied using Eqs. (5) and (9), verified by substituting Eq. (9) into Eq. (13). Therefore, two conditions are obtained as:

-

1.

If \(S_{i} > 0\) should be \(S_{i} < 0\). Then, the control law equal to 1, which can be written as

$$\dot{S}_{i} = \frac{{v_{in\_i} }}{{C_{i} L_{i} }}d_{i} - \frac{{x_{1\_i} }}{{C_{i} L_{i} }} - \frac{{P_{cpl} x_{2\_i} }}{{C_{i} x_{1\_i}^{2} }} - \ddot{v}_{ref\_i} + \lambda_{i} x_{2\_i} - \lambda_{i} \dot{v}_{ref\_i} < 0$$(14) -

2.

If \(S_{i} < 0\) should be \(S_{i} > 0\). Then, the control law equal to 0, which can be written as

$$\dot{S}_{i} = \frac{{v_{in\_i} }}{{C_{i} L_{i} }}d_{i} - \frac{{x_{1\_i} }}{{C_{i} L_{i} }} - \frac{{P_{cpl} x_{2\_i} }}{{C_{i} x_{1\_i}^{2} }} - \ddot{v}_{ref\_i} + \lambda_{i} x_{2\_i} - \lambda_{i} \dot{v}_{ref\_i} > 0$$(15)

To validate Eq. (11), the initial derivative of the Lyapunov candidate function for each DG unit in the DC MG is computed as:

In DC–DC converters forming the DC MG, the control variable is the duty cycle. Thus, based on Eqs. (9) and (13), the control input d (i.e., u = d) is given as:

The equivalent control law is given by:

The discontinued control law is defined as:

Substituting Eq. (17) into Eq. (16) yields:

This denotes

Thus, the mathematical results confirm that the Lyapunov condition has been satisfied.

Report of conventional droop control

In DC MGs, droop control is a primary strategy for distributing loads among parallel DC–DC converters. It manages current circulation and ensures dynamic power sharing, especially in islanded MG setups44,54. This method autonomously balances power distribution among DC–DC converters by using virtual resistive impedance, eliminating the need for data exchange between DG units.

Figure 5 illustrates the conventional droop control method with two parallel DC–DC converters, detailing the configuration as follows:

where \(v_{o\_(i,j)}\) represents the output voltage of each converter; \(v_{o\_(i,j)}^{*}\) is voltage reference value of the DC bus for the DC MG; \(R_{D\_(i,j)}\) indicates the droop coefficient value of each converter; \(R_{line\_(i,j)}\) represents the value of resistive line for each converter.

The output current of each DC–DC converter is determined by its virtual resistive value, as explained below:

where \(\eta_{i,j}\) is the ratio of the rated capacity between the i-th converter and the j-th converter.

From Eq. (23), Eq. (22) can be expressed as:

Assuming that \(\xi_{v\_i}\) is the maximum allowed voltage deviation, \(R_{D\_i}\) and \(v_{o\_i}^{*}\) must be designed as follows:

The droop control method causes voltage deviations at both the output of each DC–DC converter and the DC bus, which require correction according to the following expression:

The novel secondary control corrects voltage deviations and improves current sharing, enhancing the efficiency and reliability of the DC MG.

Secondary control strategy for a DC microgrid feeding a constant power load

This section proposes an H-infinity-based control method to enhance the secondary control of a DC MG supplying a CPL. The primary objectives are to correct DC bus voltage deviations caused by the primary control, develop a new model for the DC MG with a CPL, and ensure system stability despite disturbances from the CPL load and input voltage52,53. The secondary control mechanism is shown in Fig. 6. The main contributions of this section are as follows:

-

1.

Development of a robust H-infinity secondary control to correct voltage deviations from the primary control.

-

2.

Introduction of a new DC MG model incorporating a CPL for effective secondary control application.

-

3.

Assurance of system stability in the presence of CPL loads and external disturbances.

Secondary control diagram for a DC MG with a CPL. Where \(G_{SMC} (s)\) is a robust sliding mode controller intended for the inner loops (current, voltage) of the primary control. \(PI_{\infty } (s)\) is a robust H infinity controller intended for secondary control. \(G_{PWM} (s)\) is a PWM transfer function.

The derivative of the error reported for \(PI_{\infty } (s)\) is written as:

where

and

The diagonal matrix gains \(f\) and \(\beta\) are carefully chosen to ensure that the matrix Z satisfies the Hurwitz condition; \(Z_{Line}\) is a line impedance diagonal matrix; \(R_{D}\) is a diagonal droop resistance gain matrix; \(L\) denotes a Laplacian matrix; \(R_{cpl}\) denotes INI characteristic of the CPL.

System modeling

To begin, the relationship between the output voltage of the DG unit and the DC bus voltage must be defined. This relationship is critical for constructing the DC MG model at the primary control level. Figure 7 illustrates a representative circuit of a DC MG supplying a CPL, with multiple DC sources operating simultaneously.

Electrical interconnection of parallel-connected DGs supplying a CPL.

The DC bus voltage \(v_{b}\) for a DC MG supplying a CPL is expressed as:

The generated current of each DG unit is stated below using the superposition theorem:

where \(1 \le i \le n\), \(1 \le j \le n\); n is the number of DG units used to make the DC MG. \(I_{DGi}\) denotes the current supplied by the ith DG unit.

According to Eq. (37), \(I_{DGi}\) and \(I_{DGj}\) are given as follows:

Assume the DG units have the same line impedance, it follows that \(Z_{Line(1)} = \cdots = Z_{Line(i)} =\) \(Z_{Line(j)} = \cdots = Z_{Line(n)} = Z_{Line} = \frac{1}{Y}\). In the primary control of a DC MG supplying a CPL, it is assumed that \(v_{o\_1} = v_{o\_i} = v_{o\_j} = \cdots = v_{o\_n}\).

Based on the previous assumptions, substituting Eq. (37) into Eq. (36) yields the DC bus voltage. vb as follows:

As a result, using Fig. 6, the output voltage of each DC converter forming the DC MG can be expressed as:

where

\(v_{o\_i}^{*}\) represents the nominal output voltage of the DC converter.

By substituting Eq. (41) into Eq. (40), the DC bus voltage can be rewritten as:

Substituting Eq. (17) into Eq. (5), the inner loop \(G_{SMC\_i}\) of the ith DG unit can be expressed as:

The system in Eq. (41) is linearized using the Jacobian matrix to approximate its behavior near a specific operating point. This linearization simplifies the nonlinear dynamics of Eq. (41), enabling easier analysis and control design for the secondary control. It allows the use of linear control techniques to assess stability, analyze disturbance responses, and achieve desired performance, such as voltage stabilization and power sharing in the DC MG.

where \(X\) represents the vector \(\left[ {x_{1} \left. {x_{2} } \right]^{T} } \right.\); \(\dot{X}\) denotes the vector \(\left[ {\dot{x}_{1} \left. {\dot{x}_{2} } \right]^{T} } \right.\), and \(u = v_{ref}\).

The matrices A and B are derived from Eq. (44) using the Jacobian approach, as shown below:

Using matrices from Eqs. (46) and (47), the transfer function of the system can be derived as:

The DC bus voltage transfer function can be expressed by substituting Eq. (48) into Eq. (43), resulting in:

where \(\theta\) defined as \(\left( {n - 1} \right)Y + \frac{1}{{\left| {R_{cpl} } \right|}}\).

The uniform mathematical formulation of secondary control across all DG units indicates a consistent control strategy throughout the system. Variations in line impedance among DG units introduce uncertainties, which can affect the performance and stability of the system. This uncertainty in the values of \(Z_{Line}\) and \(Y\) can lead to variations in power sharing and voltage stabilization in the DC MG. It is essential to account for these variations in the control strategy to ensure the system remains stable and responsive to external disturbances. By modeling and representing this uncertainty, more robust control techniques can be designed to minimize its impact and ensure reliable operation of the DC MG, even under varying conditions.

By substituting Eqs. (50) and (51) into Eq. (43) and performing the required mathematical operations, the expression for the DC bus voltage vb can be derived as:

where

\(w_{b}\) represents the parameter that accounts for disturbances caused by transmission impedance uncertainty, and it is expressed as:

where

Secondary control level control design process for a DC MG feeding a CPL

This study focuses on designing the secondary control process using an H-infinity approach based on a Nonsmooth Optimization Algorithm (NOA), as referenced in52. The methodology incorporates an augmented system that captures the mathematical relationships between the signals to be mitigated and the target signals, such as the control variable and error. This augmented system also includes weight functions, which play a crucial role in formulating the secondary control by defining the desired performance criteria. The secondary control block diagram in Fig. 8 illustrates the developed system and highlights the significance of weight functions in the design phase. The weight functions \(W_{S1} (s)\), \(W_{S2} (s)\) and \(W_{S3} (s)\) are used to create the secondary controller of the DC MG feeding a CPL (see Fig. 9).

Robust secondary control in a closed-loop system.

Robust secondary control using weight functions.

The augmented plant \(P(s)\) required for the design process, as depicted in Fig. 9, is represented by the following expression:

During steady-state operation, all decentralized secondary controllers generate identical compensation voltage signals, such that \(\left( {s_{1} = s_{2} , \ldots ,s_{i} , \ldots ,s_{n} } \right)\).

Therefore, \(s_{i}\) can be approximately expressed as:

The linear fractional transformation (LFT) of the system is defined as follows:

where

where \(y\) and \(y_{in}\) are written as follows: \(y_{in} = \left( {\begin{array}{*{20}c} {V^{*} } \\ {W^{*} } \\ \end{array} } \right),y = \left( {\begin{array}{*{20}c} {e_{1} } \\ {e_{2} } \\ \end{array} } \right)\).

The sensitivity functions, denoted as \(S_{S} (s)\) and \(\varpi_{s}\), can be expressed as follows:

To ensure that the designed controller \(PI_{\infty } (s)\) meets the control objectives, it must satisfy the following condition:

The design must meet Eq. (63) and select suitable weight functions for stability. To validate this condition, it is recommended to examine the norm of the H_infinty of the gains within the transfer matrix \(\left\| {F_{L} (P(s),PI_{\infty } (s))} \right\|_{\infty }\), ensuring these values remain below a specified boundary \(\gamma\). This approach ensures a robust design, confirming the effectiveness and reliability of the introducing controller in achieving the optimal control objectives. This leads to:

The mathematical expressions of these weight functions are expressed as:

where

and

In addition, \(K_{2}^{\prime}\) have to be chosen less then \(\varepsilon\).

The parameter \(w_{cs}\) represents the cutoff frequency, which plays a crucial role in shaping the dynamic response of the secondary control system. Since the primary control typically responds faster than the secondary control, \(w_{cs}\) must be selected to operate at a lower frequency than the primary control. This ensures that the secondary control system can effectively complement and stabilize the primary control response, reducing the risk of instabilities or oscillations in the overall control framework.

The parameters \(w_{cs}\) and \(\Delta G\) are key metrics for evaluating system performance, with \(w_{cs}\) representing the steady-state error and \(\Delta G\) indicating the gain margin. The next section provides a detailed overview of the NOA and explains how the NOA process is applied.

Secondary control for DC microgrid using nonsmooth optimization algorithm

The NOA is used to address a specific optimization problem in secondary control design. Its main goal is to find a structured controller configuration that minimizes the H∞ norm of \(F_{L} (P(s),PI_{\infty } (s))\). This optimization aims to reduce the impact of disturbances, especially those represented by \(y_{in}\), and stabilize \(P(s)\) within the system. By minimizing the H∞ norm, the NOA enhances the system’s ability to attenuate disturbances and maintain stability, leading to better performance and reliability in practical applications52. This optimization problem is formulated as follows:

The variable w denotes the frequency and is defined within the real interval \({\mathbb{R}}\); The controller \(PI_{\infty } (s)\) is designed with a fixed structure similar to that of a PI control configuration.

The NOA relies on the derivative of the Clarke subdifferentiable function, which is defined as follows:

Definition 1

(Clarke subdifferentiable function). Let consider two functions \(f(x)\) and \(G(x)\), where \(f(x)\) is equal to the H∞ norm of \(G(x)\). \(f(x)\) can be written as follows:

The Clarke subdifferentiable function derived from \(f(x) = \left\| {G(x)} \right\|_{\infty }\) is written as follows:

where \(\wp (x)\) is the smooth operator, mapping \(R^{n}\) on the space H∞ of the \(G(x)\), \(\wp^{\prime} (x)\) is the adjoint of \(\wp (x)\) and \(\phi \left( {\wp (x)} \right)\) is the subgradient \(\wp (x)\) of at \(G(x)\).

Definition 2

(Smooth operator). Let consider a function \(G(x)\) that links the outputs vector y to the inputs vector u. This mathematical relationship between u and y is expressed as follows:

where u and y can be written as:

\(G(x)\) can be divided into smooth operators, where each operator is a subfunction derived from \(G(x)\). Linking a single input to a single output, as expressed by the following equation:

\(G_{{u_{j} \to y_{j} }} (x)\) denotes the smooth operator.

Definition 3

(Smooth operator subgradient). Let’s consider a function \(G(x)\), and \(G_{{u_{i} \to y_{i} }} (x)\) is a smooth operator derived from \(G(x)\). The subgradient of \(\, G_{{u_{i} \to y_{i} }} (x)\) at \(G(x)\) is given as

Based on Definition 2, the smooth operators derived from \(F_{L} (P(s),PI_{\infty } (s))\) are given as follows:

As per Definition 3, subgradients can be determined using the smooth operators at \(F_{L} (P(s),PI_{\infty } (s))\) outlined in Eqs. (76), (77), (78), and (79). These equations can be expressed as follows after rewriting them accordingly.

According to Definition 1, Clarke subdifferentiable functions derived from Eqs. (80), (81), (82), and (83) can be expressed as follows:

The data of the controller \(PI_{\infty } (s)\), represented by x, can be expressed as follows:

The NOA operates using subgradients and Clarke subdifferentiable functions. The NOA process involves the following steps.

-

Step 1 start the variable x with a large initial value, denoted as \(x = x^{ + }\)

-

Step 2 Minimize Eqs. (80) to (83) as part of solving a convex optimization problem.

-

Step 3 Insert the minimal values from Eqs. (80) to (83) into Eqs. (84) to (87). If all results are non-zero, decrease x by \(\Delta x\left( {x = x^{ + } - \Delta x} \right)\) (where \(\Delta x = ( {\Delta k_{p} } \;\, {\frac{{\Delta k_{p} }}{\left\| d \right\|}} )\)). Choose \(\Delta k_{p}\) as small as possible, and let d should be the subgradients vector from Eqs. (84) to (87). Update \(x^{ + }\) with the new x and go back to Step 2. If any Equation equals zero, check the condition in Eq. (64). If satisfied, stop and use the controller as the solution from Eq. (68). If the condition is met, go to Step 4 to calculate \(\gamma\).

-

Step 4 Update the weight functions and restart at Step 1. The process concludes when the weight functions have effectively optimized the controller.

The steps of the NOA Algorithm are illustrated in the flowchart shown in Fig. 10.

Nonsmooth optimization algorithm flowchart.

Stability analysis

The stability analysis of the system under investigation necessitates the verification of the condition in Eq. (64) for varying system parameters, including DC bus voltage thresholds of \(v_{b} - 40\% < v_{b} < v_{b} + 40\%\), using the singular value plot. In this context, the singular value evolutions of the sensitivity and complementary sensitivity functions are presented in Fig. 11. The system parameters employed for the stability study are provided in Table 1.

Frequency response analysis based on the evolution of Eq. (64).

Where the controller that have been used for the secondary controller is defined as follows:

According to the generated algorithm, the weight functions applied to the secondary controller are specified as follows:

\(\gamma\) is given as follows:

\(f_{i}\) and \(\beta_{i}\) are selected for each DC–DC buck converter as follows:

As shown in Fig. 11, the condition specified in Eq. (64) is verified, indicating that the stability criteria for the proposed H∞ control design are met. This confirms the ability of the proposed control strategy to effectively attenuate all disturbances in the DC bus. The performance of the PI∞(s) control scheme is further demonstrated as follows:

Based on Fig. 9 and neglecting the influence of the weight functions in the proposed control loop, the error y \(\left( {y = V^{*} - v_{b} } \right)\) and the voltage compensation signal si can be expressed as follows:

Based on the obtained singular plots, the magnitude of all expressions in Eq. (64) is less than 1, where \(\left( {\left| {S_{S} (s)G_{SMC} (s)} \right| \ll 1,\left| {S_{S} (s)G_{SMC} (s)} \right| \ll 1,\left| {\varpi_{S} (s) \ll 1} \right|,\left| {S_{S} (s)G_{SMC} (s)B_{1} (s)} \right| \ll 1} \right)\).

This implies that the influence of the disturbance variables \(V^{*}\) and \(W^{*}\) on the \(y\) and \(s_{i}\) is neglected. Therefore, based on Eq. (58), y depends exclusively on si.

Simulation results

A simulation using PSIM software was conducted to test the developed controller, modeling a DC MG as illustrated in Fig. 4, and operating under the proposed approach. This MG consists of two parallel-connected buck converters supplying a CPL. These two DC–DC converters have differing LC filter parameters. The input voltage for the converters is supplied by DC sources, serving as an equivalent model of RESs. Various scenarios were tested throughout the simulation. Due to an external disturbance in the MG, fluctuations in the load and input voltage are taken into account in this simulation. The parameters of the DC–DC buck converters are given in Table 1.

Figure 12 illustrates the performance of the DC MG with the proposed secondary controller, highlighting quick settling times (0.2 s), minimal overshoot, and accurate tracking of the output voltages, achieving a stable zero steady-state error. Furthermore, proportional load current sharing is achieved among the DGs, ensuring the restoration and stability of the DC bus voltage.

Closed-loop response of the DC MG with the proposed secondary controller: (a) vo1, (b) vo2, (c) output currents, (d) DC bus voltage.

Case 1: activated of the proposed controller test

Initially, the stability of the DC MG with the proposed secondary controller is evaluated. Prior to t = 1.5 s, the two DGs operate in parallel, each regulating its respective output voltage. The terminal voltage is maintained at a reference value of 16 V (see to Fig. 13). Due to variations in load, the output currents of the DGs differ (see Fig. 13b). At t = 3.5 s, DG-1 and DG-2 are synchronized using primary controllers (see Fig. 13c), with the virtual impedance in the droop controls set to 5 Ω. Subsequently, the secondary controller is activated at t = 3.5 s to correct the voltage deviation caused by the primary control, which draws 10 W.

Response to secondary control activation: (a) output currents, (b) output voltages, (c) DC bus voltage.

As illustrated in Fig. 13b, proportional load current sharing is achieved by automatically adjusting the DG voltages (see Fig. 13a) to their nominal values using the proposed secondary controller.

Case 2: power demand variation test

The simulation results validate the effectiveness of the proposed controller in stabilizing the DC MG system under dynamic and challenging conditions. Specifically, the controller successfully mitigates fluctuations caused by abrupt changes in the power demand of a CPL, as shown in Fig. 14. Initially, the system operates at a steady state with a power demand of 10 W. Between t = 1 s and t = 3.5 s, the CPL power demand increases rapidly to 25 W. Despite this significant demand increase, the controller ensures system stability, effectively preventing oscillations or sudden transient disturbances. A further increase in power demand to 35 W between t = 3.5 s and t = 4.5 s, with the controller once again demonstrating its robustness by promptly adjusting to the new load while maintaining stable operation. Finally, an additional sudden increase of 15 W is applied from t = 4.5 s to the end of the simulation, further complicating the power demand profile. The controller continues to stabilize the system, as evidenced by the absence of fluctuations in Fig. 14.

System response to changing CPL power demand: (a) output currents, (b) output voltages, (c) DC bus voltage.

These simulation results show that the controller is strong and flexible in handling sudden large changes in power demand from the load of the DC MG. Its ability to reduce quick fluctuations and prevent instability makes it valuable for keeping DC MG systems reliable, especially in environments were power needs change randomly. This capability is vital for applications with fluctuating power demands, as it allows for consistent performance and reliable operation under a variety of scenarios.

Case 3: input voltage variation test

To thoroughly evaluate the robustness and effectiveness of the proposed secondary controller under challenging conditions, a set of tests was conducted simulating significant input voltage fluctuations. These tests involved voltage drops of up to 45%, as illustrated in Fig. 15, where the input voltage initially decreased from 32 to 17 V before returning to the nominal level. The simulation results indicate that the controller successfully maintained the output voltages of both DGs and the DC bus close to their reference values, despite the large variations in input voltage. This performance demonstrates the fast response capabilities of the controller, as it minimized the risk of overshoot or instability, a common issue during abrupt voltage changes.

System response under input voltage fluctuations: (a) input voltage variation test, (b) output voltages, (c) output currents, (d) DC bus voltage.

Additionally, the secondary controller effectively balanced current sharing among the DGs, which is essential for stable and efficient MG operation. The ability to keep inductor current variations low further indicates that the controller can stabilize internal currents under non-ideal input conditions. This balanced current distribution not only helps protect the DGs from overloading but also extends their durability by ensuring a more even load distribution. Such robust control over fluctuating input voltages is crucial in practical applications where voltage conditions are not always stable, highlighting the value of the controller for reliable and consistent DC MG operation in real-world settings.

Case 4: DC bus reference variation test

This test aims to evaluate the stability and robustness of the system by introducing a step change in the DC bus reference voltage within the DC MG, as illustrated in Fig. 16. Initially, the DC bus voltage stabilizes at 16 V, reflecting a rapid response to the set reference. At t = 1.5 s, the reference voltage is increased to 19 V, and at t = 3.5 s, it reverts to the original value (see Fig. 16a). During these transitions, the system effectively adapts by adjusting the output currents of both DC–DC converters, ensuring stable power-sharing and mitigating instability (see Fig. 16b). The test results reveal that the DC bus voltage tracks the target profile accurately, showing minimal settling time, no overshoot, and a high degree of stability, even with significant step variations in the reference value. Furthermore, the proposed secondary compensation control ensures the DC bus voltage adjusts closely to the desired reference value, highlighting its effectiveness in high-performance applications (see Fig. 16d). This control approach enhances system stability, demonstrating robustness against voltage variations while maintaining balanced load sharing across the DC–DC converters. Consequently, the developed control technique proves to be robust, showing that the system can manage sudden changes in the DC bus voltage reference without compromising power distribution or operational stability.

System response under reference DC bus voltage changes: (a) reference DC bus voltage variation test; (b) output voltages; (c) output currents; (d) DC bus voltage.

Case 5: DG plug-and-play

This study investigates the plug-and-play capabilities of the suggested secondary control for DG units in a DC MG, as shown in Fig. 17. The setup involves DG-2, initially integrated with the DC bus and operating under the primary and secondary controllers, which ensure a stable output voltage of 16 V. At t = 1.5 s, DG-2 is intentionally unplugged from the DC bus, creating a test scenario for the response of the suggested controller. Following the disconnection, the DC bus voltage remains steady at 16 V, suggesting the capacity of the system to maintain voltage levels in the absence of DG-2. The unplugged period continues until t = 3 s, after which DG-2 is restored to the DC bus. This reconnection promptly restores stability across the DC bus, illustrating the capability of the controller to seamlessly reintegrate DG units without causing transient disturbances. This response highlights the effectiveness of the controller in maintaining system stability and managing dynamic changes in network configuration.

Response to plug and play: (a) output currents; (b) output voltages; (c) DC bus voltage.

The results, as illustrated in the accompanying Fig. 17, highlight the effectiveness of the proposed controller in regulating voltage and ensuring system stability despite the plug-and-play behavior of DG units. By eliminating voltage deviation and maintaining a steady-state condition, the controller proves to be a robust solution for ensuring power quality within dynamic and flexible distributed energy systems. This functionality is essential for MGs, where the intermittent nature of DG units and varying load demands necessitate a control strategy capable of rapid adaptation. Consequently, this study affirms the suitability of the secondary controller for applications requiring high levels of reliability and resilience, thereby supporting the integration of distributed generation in sustainable and efficient power networks.

Comparative performance assessment:

This subsection presents a comparative performance analysis of the proposed hybrid sliding mode H∞ control for primary and secondary control, compared to well-known existing methods in the literature, as shown in Table 2. From Table 2, it can be inferred that the proposed control outperforms all other algorithms, making it an effective solution for handling power sharing and voltage regulation, even under external disturbances such as input voltage variation, power load demand fluctuations, plug-and-play scenarios, and uncertainties.

Experimental validation

A scaled-down laboratory prototype of a DC MG with two DGs was implemented to experimentally validate the proposed controller. The experimental setup was carried out based on the generated C code from PSIM software. In this experiment, a voltage-controlled boost converter, acting as a CPL, was supplied by two parallel buck converters, forming the DC MG. To simulate line impedance effects, resistors were placed between each output of the converters and the main DC bus, replicating real MG conditions.

The experimental setup, depicted in Fig. 18, models each DG as an ideal voltage source (VDC = 36 V) paired with a buck converter, representing the power generation units in the DC MG. The setup was built using a voltage sensor (LA25-NP, 717087) and a current sensor (LV25-P, 714227). Control algorithms for the system were implemented on a DSP28335 microcontroller, which generates pulse-width modulation (PWM) signals for both buck converters and the boost converter acting as the CPL. Data acquisition and PWM frequencies were both set at 25 kHz for synchronized control.

Experiment setup.

The effectiveness of the proposed controller was tested under four scenarios:

-

Test 1: Secondary control activation.

-

Test 2: Power load demand variation.

-

Test 3: DC bus voltage reference variation.

-

Test 4: Plug and play.

This experimental setup allowed for testing voltage regulation, stability, and the robustness of the secondary control approach under dynamic conditions. It is worth noting that, despite the parameters listed in Table 1 not being identical to those used in the implementation, all experimental results demonstrated excellent tracking performance and disturbance rejection in all scenarios.

Figures 19, 20, 21, 22, 23, 24, 25, 26 and 27 illustrate the experimental results. Detailed configuration parameters, including component values and system settings, are provided in Table 3.

Experimental results: time evolution of DG output voltages during secondary control activation.

Experimental result: time evolution of the output currents of each DG under secondary control activation.

Experimental result: time evolution of the DC bus voltage under secondary control activation.

Experimental results: time evolution of the output voltages of each DG under CPL variation.

Experimental results: time evolution of DG output currents during CPL variation.

Experimental result: time evolution of the DC bus voltage under CPL variation.

Experimental result: time evolution of the DC bus voltage response to reference value changes.

Experimental results: time evolution of DG output currents during plug-and-play scenario.

Experimental result: time evolution of the DC bus voltage under the scenario of plug-and-play.

The parameters of the boost converter are: \(v_{in\_boost} = 18\,{\text{V}}\), \(v_{o\_boost} = 22\,{\text{V}}\), \(C_{o\_boost} = 470\,\upmu {\text{F}}\), \(L_{o\_boost}\) = 0.52 mH, \(R_{L\_boost} = 33\,\Omega ,\;f_{sw\_boost} = 25\,{\text{kHz}}\).

Experimental results with the secondary control activation

In this sub-section, the proposed secondary control technique is evaluated under a scenario that includes secondary control activation. The experimental results in real time, presented in Figs. 19, 20, and 21, show the systems behavior before and after control activation. Initially, neither primary nor secondary control is active, resulting in output voltage drops for vo1 and vo2 to 16.5 V and 17 V, respectively, and a DC bus voltage of 17.2 V. This deviation from the reference voltage vb = 18 V is attributed to the issue of current circulation within the system.

Upon activation of the primary control, output voltages vo1 and vo2 further drop to 13.4 V and 13.5 V, with the DC bus voltage decreasing to 13.4 V, creating a substantial deviation from the required reference values. However, under primary control, a balanced power-sharing ratio is achieved between DGs with a fast-settling time around of 0.2 s, although overshot is not observed. These observations emphasize the need for secondary control to maintain stable output and bus voltages while ensuring accurate power-sharing.

Upon activation of the proposed secondary control, the DC bus voltage is restored to the desired reference value with a fast response within 0.75 s, and no overshoot is noted. The control strategy effectively stabilizes voltage and maintains a consistent power-sharing ratio among the distributed generators, ensuring balanced load distribution.

The experimental evaluation demonstrates that the proposed secondary control strategy effectively stabilizes the DC bus voltage at the desired reference value and maintains a balanced power-sharing ratio between the DGs. Without any control activation, voltage deviations occur due to current circulation, leading to significant drops in both output voltages and DC bus voltage. While primary control achieves power-sharing, it does not adequately address voltage stability. The activation of secondary control successfully resolves these issues, highlighting its essential role in achieving both voltage regulation and balanced current-sharing distribution within the DC MG.

Experimental results with constant power load fluctuation

In this sub-section, we evaluate the proposed controller under conditions where the CPL fluctuates. To test the response of the system, the CPL power is varied from 10 to 20 W before returning to its nominal value. The experimental results, displayed in Figs. 22, 23, and 24, indicate that despite these fluctuations, whether the power load demand steps up or down, the DC bus voltage remains stable at vb = 18 V.

The two DGs exhibit effective current-sharing, producing nearly equal output while maintaining stable output voltages unaffected by fluctuations. The performance conforms to the droop control method and the functionality of local controllers, demonstrating the robustness of the proposed control strategy.

The proposed control maintains DC bus voltage stability at the reference value of vb = 18 V, rejecting all fluctuations with a good response time of around 0.7 s and negligible overshoot. The experimental results confirm that the DC bus voltage remains stable despite variations in the CPL, while the DGs efficiently share the current output and maintain stable voltages across the buck converters. This finding, consistent with the droop control design, highlights the effectiveness of the control strategy in achieving reliable voltage regulation and balanced load distribution within the system, even under dynamic operating conditions.

These results highlight the system ability to maintain voltage stability and ensure balanced load distribution among DGs, even under fluctuations in the CPL.

Experimental results with DC bus voltage reference variation

This sub-section evaluates the performance of the proposed controller under varying DC bus voltage reference conditions. The DC bus reference voltage is adjusted from 18 to 20 V and then returned to its nominal value. This scenario was used to assess the response of the DC bus under the proposed secondary control strategy with a variable reference voltage. The experimental results show that the DC bus voltage tracks the reference value with a fast-settling time of approximately 0.8 s, even when the reference voltage fluctuates.

Experimental results, displayed in Fig. 25, demonstrate that the DC bus voltage remains stable regardless of fluctuations in the reference, whether it increases or decreases.

Experimental results with plug-and-play

This sub-section examines the systems performance during the plug-and-play integration of DG-2 into the DC MG. DG-2 is sequentially disconnected and reconnected to the DC bus to assess the systems response. The experimental results, shown in Figs. 26 and 27, demonstrate that the proposed secondary control method effectively rejects fluctuations, maintaining the DC bus voltage at the reference value throughout the operation. Additionally, DG-1 adjusts its current output, nearly doubling it, to share the load almost equally in response to DG-2s disconnection.

The results confirm that the control strategy maintains DC bus voltage stability during DG-2s plug-and-play operation. Despite DG-2s disconnection and reconnection, the control method eliminates fluctuations, ensuring the DC bus voltage remains at the reference value with a fast response time of approximately 0.4 s. Furthermore, DG-1 increases its current output, ensuring balanced load sharing when DG-2 is disconnected. These findings underscore the robustness of the secondary control in enhancing voltage stability and adaptive load distribution in a plug-and-play scenario.

Comparison between simulation and experimental results

To validate the proposed control strategy, this subsection presents a comparison of key performance metrics obtained from simulation and experimental results, as shown in Table 4. This table includes overshoot, efficiency, and time response, providing insights into the practical applicability of the control approach under real-time conditions. The comparison shows strong agreement between simulation and experimental results, with minor discrepancies attributed to hardware limitations and unmodeled parasitic effects. These findings confirm the robustness and practical feasibility of the proposed method.

Conclusion

In this paper, a hybrid sliding mode and H-infinity control strategy is proposed for enhanced primary and secondary regulation in a DC microgrid feeding a tightly voltage-regulated boost converter that acts as a constant power load (CPL). CPLs are characterized as loads that behave like negative impedances, which introduce stability challenges to the microgrid. To adapt this nonlinear control technique to this specific case, the circulating current problem, a key limitation of the primary control, is first addressed by suggesting a sliding mode controller (SMC). This approach effectively achieves voltage regulation and ensures balanced power distribution.

The system model for each DC–DC converter in the microgrid, including the CPL, was transformed to adapt to the sliding mode controller design. This method successfully eliminates the need for passive loads with CPLs, which are commonly used in previous works. In the second step, voltage deviation, a primary control issue, is addressed through a secondary control strategy using H-infinity control. This approach combines inner SMC loops, droop control, and the CPL of each DC–DC buck converter, with model linearization achieved through the Jacobian technique.

The effectiveness of the proposed controller has been validated through simulations and experiments, involving five case studies. These tests included secondary control activation, responses to CPL fluctuations, input voltage variations, reference value changes, and sudden plug-and-play scenarios—typical situations in DC or AC microgrids. As a result, the system demonstrated effective performance in tracking, power sharing, voltage restoration, and disturbance rejection. The experimental results also validated these capabilities of the proposed controller. As a future perspective, the authors plan to extend the proposed method to handle diverse load types including motor drives. Furthermore, integrating hybrid AC–DC MGs represents a promising avenue for further investigation. These efforts aim to enhance the method’s robustness and scalability in complex and diverse MG configurations.

Data availability

The datasets used and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Li, Z., Hu, J., Leng, B., Xiong, L. & Fu, Z. An integrated of decision making and motion planning framework for enhanced oscillation-free capability. IEEE Trans. Intell. Transp. Syst. 25(6), 5718–5732 (2024).

Zhang, R. et al. An asymmetric hybrid phase-leg modular multilevel converter with small volume, low cost, and DC fault-blocking capability. IEEE Trans. Power Electron. 40, 1–15 (2024).

Tan, J., Zhang, K., Li, B. & Wu, A. Event-triggered sliding mode control for spacecraft reorientation with multiple attitude constraints. IEEE Trans. Aerosp. Electron. Syst. 59(5), 6031–6043 (2023).

Gu, Y., Li, W. & He, X. Frequency-coordinating virtual impedance for autonomous power management of DC microgrid. IEEE Trans. Power Electron. 30(4), 2328–2337. https://doi.org/10.1109/TPEL.2014.2325856 (2015).

Rong, Q. et al. Virtual external perturbance-based impedance measurement of grid-connected converter. IEEE Trans. Ind. Electron. https://doi.org/10.1109/TIE.2024.3436629 (2024).

Zhou, Z. et al. Vehicle lateral dynamics-inspired hybrid model using neural network for parameter identification and error characterization. IEEE Trans. Veh. Technol. 73(11), 16173–16186 (2024).

Guerrero, J. M., Vasquez, J. C., Matas, J., De Vicuña, L. G. & Castilla, M. Hierarchical control of droop-controlled AC and DC microgrids—A general approach toward standardization. IEEE Trans. Ind. Electron. 58(1), 158–172 (2011).

Hamad, A. A., Azzouz, M. A. & El-Saadany, E. F. Multi agent supervisory control for power management in DC microgrids. IEEE Trans. Smart Grid 7(2), 1057–1068 (2016).

Li, Y. et al. Load profile inpainting for missing load data restoration and baseline estimation. IEEE Trans. Smart Grid 15(2), 2251–2260 (2024).

Zhang, H. et al. Homomorphic encryption-based resilient distributed energy management under cyber-attack of micro-grid with event-triggered mechanism. IEEE Trans. Smart Grid 15(5), 5115–5126 (2024).

Zhang, H., Yue, D., Dou, C. & Hancke, G. P. PBI based multi-objective optimization via deep reinforcement elite learning strategy for micro-grid dispatch with frequency dynamics. IEEE Trans. Power Syst. 38(1), 488–498 (2023).

Liang, J., Yang, K., Tan, C., Wang, J. & Yin, G. Enhancing high-speed cruising performance of autonomous vehicles through integrated deep reinforcement learning framework. IEEE Trans. Intell. Transp. Syst. 26(1), 835–848 (2025).

Zeng, H., Zhu, Z., Peng, T., Wang, W. & Zhang, X. Robust tracking control design for a class of nonlinear networked control systems considering bounded package dropouts and external disturbance. IEEE Trans. Fuzzy Syst. 32(6), 3608–3617 (2024).

Gao, S., Chen, Y., Song, Y., Yu, Z. & Wang, Y. An efficient half-bridge MMC model for EMTP-type simulation based on hybrid numerical integration. IEEE Trans. Power Syst. 39(1), 1162–1177 (2024).

Shirkhani, M. et al. A review on microgrid decentralized energy/voltage control structures and methods. Energy Rep. 10, 368–380 (2023).

Rong, Q. et al. Asymmetric sampling disturbance-based universal impedance measurement method for converters. IEEE Trans. Power Electron. 39(12), 15457–15461 (2024).

Emadi, A., Khaligh, A., Rivetta, C. H. & Williamson, G. A. Constant power loads and negative impedance instability in automotive systems: Definition, modeling, stability, and control of power electronic converters and motor drives. IEEE Trans. Veh. Technol. 55(4), 1112–1125. https://doi.org/10.1109/TVT.2006.877483 (2006).

Abhishek, A. et al. Review of hierarchical control strategies for DC microgrid. IET Renew. Power Gener. 14, 1631–1640. https://doi.org/10.1049/iet-rpg.2019.1136 (2020).

Yadav, R. K., De, S., Sahoo, S. R. & Chakrabarti, S. Secondary control method for standalone DC Microgrid with improved voltage regulation, load sharing, and line loss. In 2020 IEEE Power and Energy Society General Meeting (PESGM), Montreal, QC, Canada, 1–5. https://doi.org/10.1109/PESGM41954.2020.9282164 (2020).

Ghanbari, N. & Bhattacharya, S. Constant power load challenges in droop controlled DC microgrids. In IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 3871–3876. https://doi.org/10.1109/IECON.2019.8926842 (2019).

Elhassaneen, H. A. E. & Tsuji, T. Cooperative decentralized tertiary based control of DC microgrid with renewable distributed generation. In 2019 IEEE Third International Conference on DC Microgrids (ICDCM), Matsue, Japan, 1–6. https://doi.org/10.1109/ICDCM45535.2019.9232871 (2019).

Li, N. et al. An improved modulation strategy for single-phase three-level neutral-point-clamped converter in critical conduction mode. J. Mod. Power Syst. Clean Energy 12(3), 981–990 (2024).

Zhou, J. et al. A novel secondary optimal control for multiple battery energy storages in a DC microgrid. IEEE Trans. Smart Grid 11(5), 3716–3725. https://doi.org/10.1109/TSG.2020.2979983 (2020).

Xing, L., Cai, J., Liu, X., Fang, J. & Tian, Y.-C. Distributed secondary control of DC microgrid via the averaging of virtual current derivatives. IEEE Trans. Ind. Electron. 71(3), 2914–2923. https://doi.org/10.1109/TIE.2023.3269470 (2024).

Tah, A. & Das, D. An enhanced droop control method for accurate load sharing and voltage improvement of isolated and interconnected DC microgrids. IEEE Trans. Sustain. Energy 7(3), 1194–1204. https://doi.org/10.1109/TSTE.2016.2535264 (2016).

Wang, W., Xie, R. & Ding, L. Stability analysis of load frequency control systems with electric vehicle considering time-varying delay. IEEE Access 13, 3562–3571 (2025).

Han, Y., Ning, X., Yang, P. & Xu, L. Review of power sharing, voltage restoration and stabilization techniques in hierarchical controlled DC microgrids. IEEE Access 7, 149202–149223. https://doi.org/10.1109/ACCESS.2019.2946706 (2019).

Ensermu, G. & Bhattacharya, A. Control and stability analysis of DC micro-grids with constant power loads and source disturbances. In 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Chennai, India, 1–6. https://doi.org/10.1109/PEDES.2018.8707605 (2018).

Duan, Y., Zhao, Y. & Hu, J. An initialization-free distributed algorithm for dynamic economic dispatch problems in microgrid: Modeling, optimization and analysis. Sustain. Energy Grids Netw. 34, 101004 (2023).

Ahmadi, F., Batmani, Y., Bevrani, H., Yang, T. & Cui, C. Finite-time synergetic controller design for DC microgrids with constant power loads. IEEE Trans. Smart Grid 14(5), 3352–3361. https://doi.org/10.1109/TSG.2023.3237360 (2023).

Rastogi, R. K. & Tripathy, M. A new adaptive damping control for load-side converters to mitigate instability in DC microgrids for constant power loads. In IECON 2022—48th Annual Conference of the IEEE Industrial Electronics Society, Brussels, Belgium, 1–6. https://doi.org/10.1109/IECON49645.2022.9968619 (2022).

Cecilia, A., Sahoo, S., Dragičević, T., Costa-Castelló, R. & Blaabjerg, F. Detection and mitigation of false data in cooperative DC microgrids with unknown constant power loads. IEEE Trans. Power Electron. 36(8), 9565–9577. https://doi.org/10.1109/TPEL.2021.3053845 (2021).

Mirzaeva, G., Miller, D., Goodwin, G. & Wheeler, P. A stable and robust DC power system for more electric aircraft. In 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 5196–5201. https://doi.org/10.1109/ECCE47101.2021.9595813 (2021).

Zheng, M., Wen, H., Bu, Q. & Shi, H. Dynamic response improvement for DAB converter with constant power load under extended-phase-shift control based on trajectory control. In 2020 IEEE 9th International Power Electronics and Motion Control Conference (IPEMC2020-ECCE Asia), Nanjing, China, 840–845. https://doi.org/10.1109/IPEMC-ECCEAsia48364.2020.9368095 (2020).

Gheisarnejad, M., Farsizadeh, H., Tavana, M.-R. & Khooban, M. H. A novel deep learning controller for DC–DC buck-boost converters in wireless power transfer feeding CPLs. IEEE Trans. Ind. Electron. 68(7), 6379–6384. https://doi.org/10.1109/TIE.2020.2994866 (2021).

Tian, X., Wang, Y., Wang, F., Guo, Z. & Dong, Y. An improved droop control strategy for accurate current sharing and DC-BUS voltage compensation in DC microgrid. In The 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online Conference, 1466–1473. https://doi.org/10.1049/icp.2020.0285 (2020).

Cupelli, M., Gurumurthy, S. K. & Monti, A. Modelling and control of single phase DAB based MVDC shipboard power system. In IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 6813–6819. https://doi.org/10.1109/IECON.2017.8217190 (2017).

Gurumurthy, S. K., Cupelli, M. & Monti, A. State space modelling and control of triple phase shift modulated single phase DAB for shipboard power system. In IECON 2017—43rd Annual Conference of the IEEE Industrial Electronics Society, Beijing, China, 6826–6832. https://doi.org/10.1109/IECON.2017.8217192 (2017).

Anand, S., Fernandes, B. G. & Guerrero, J. M. Distributed control to ensure proportional load sharing and improve voltage regulation in low-voltage DC microgrids. IEEE Trans. Power Electron. 28(4), 1900–1913 (2013).

Laaksonen, H. Voltage and frequency control of inverter based weak LV network microgrid. In Proceedings of the EEE FPS, 1–6 (2005).

Khorsandi, A., Ashourloo, M. & Mokhtari, H. A decentralized control method for a low-voltage DC microgrid. IEEE Trans. Energy Convers. 29(4), 793–801 (2014).

Qiu, W. & Liang, Z. Practical design considerations of current sharing control for parallel VRM applications. In Proceedings of IEEE APEC, 281–286 (2005).

Vandoorn, T. L., Member, S. & Meersman, B. A control strategy for islanded microgrids with DC-link voltage control. IEEE Trans. Power Deliv. 26(2), 703–713 (2011).

Muchande, S. & Thale, S. Design and implementation of autonomous low voltage DC microgrid with hierarchical control. In 2020 IEEE First International Conference on Smart Technologies for Power, Energy and Control (STPEC), Nagpur, India, 1–6. https://doi.org/10.1109/STPEC49749.2020.929774. (2020).

Liu, Z. et al. Stability analysis of DC microgrids with constant power load under distributed control methods. Automatica 90, 62–72 (2018).

Zhao, J. & Dörfler, F. Distributed control and optimization in DC microgrids. Automatica 61, 18–26 (2015).

Bidram, A., Davoudi, A., Lewis, F. L. & Qu, Z. Secondary control of microgrids based on distributed cooperative control of multi-agent systems. IET Gener. Transm. Distrib. 7(8), 822–831. https://doi.org/10.1049/iet-gtd.2012.0576 (2013).

Coelho, E. A. et al. Small-signal analysis of the microgrid secondary control considering a communication time delay. IEEE Tran. Ind. Electron. 63(10), 6257–6269. https://doi.org/10.1109/TIE.2016.2581155 (2016).

Braitor, A.-C., Konstantopoulos, G. & Kadirkamanathan, V. Stability analysis of DC micro-grids with CPLs under novel decentralized primary and distributed secondary control. Automatica 139, 110187. https://doi.org/10.1016/j.automatica.2022.110187 (2022).

Singh, S., Fulwani, D. & Kumar, V. Robust sliding-mode control of DC/DC boost converter feeding a constant power load. IET Power Electron. 8(7), 1230–1237 (2015).

Louassaa, K., Chouder, A., Boukerdja, M., Cherifi, A. & Aillane, A. Sliding mode control for a DC–DC buck converter feeding a constant power load: A practical implementation. In 2022 International Conference of Advanced Technology in Electronic and Electrical Engineering (ICATEEE), M'sila, Algeria, 1–5. https://doi.org/10.1109/ICATEEE57445.2022.10093728 (2022)

Apkarian, P. & Noll, D. Nonsmooth optimization for multidisk H∞ synthesis. Eur. J. Control 12(3), 229–244 (2006).

Boukerdja, M. et al. H∞ based control of a DC/DC buck converter feeding a constant power load in uncertain DC microgrid system. ISA Transactions 105, 278–295 (2020).

Louassaa, K., Chouder, A., Boukerdja, M., Cherifi, A. & Aillane, A. An enhanced primary control level for a DC microgrid systems. In 2022 19th International Multi-conference on Systems, Signals and Devices (SSD), Sétif, Algeria, 1180–1185. https://doi.org/10.1109/SSD54932.2022.9955650 (2022).

Louassaa, K., Chouder, A. & Rus-Casas, C. Robust nonsingular terminal sliding mode control of a buck converter feeding a constant power load. Electronics 12(3), 728. https://doi.org/10.3390/electronics12030728 (2023).

Author information

Authors and Affiliations

Contributions

K.L., J.M.G., M.B., A.C., B.K., A.C. and M.Z.Y. wrote the main manuscript text. K.L., J.M.G., M.B., A.C., B.K., A.C. and M.Z.Y. prepared figures. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Louassaa, K., Guerrero, J.M., Boukerdja, M. et al. A novel hierarchical control strategy for enhancing stability of a DC microgrid feeding a constant power load. Sci Rep 15, 7061 (2025). https://doi.org/10.1038/s41598-025-89318-0

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-89318-0

Keywords

This article is cited by

-

A frequency restoration control scheme of series-parallel-type microgrids with local low bandwidth communication

Scientific Reports (2026)

-

Enhanced power sharing and voltage regulation for islanded nano-satellite DC microgrids in spinning flight scenarios

Scientific Reports (2025)

-

Decentralized active fault tolerant control of direct current microgrids under actuator and source disturbances using proportional integral unknown input observer

Scientific Reports (2025)

-

Adaptive control of DC-DC power converter: design and experimental investigation with constant power load

Scientific Reports (2025)