Abstract

The vast interconnection between digital logic blocks is the main challenge faced in chip designing, which leads to increased area overheads and average power consumption. One possible solution to overcome this challenge is to make use of multi-valued logic. However, for implementing multi-valued logic, new design techniques that deliver low-power and high-speed performance need to be explored. In this paper, carbon nanotube field effect transistor (CNTFET) based standard quaternary logic gates have been designed using pass transistor logic and voltage divider circuit techniques. The simulation results for the standard quaternary logic gates have been obtained using HSPICE with standard 32 nm CNTFET Stanford model. The results for the standard quaternary inverter circuit at a supply voltage of 0.9 V show average power consumption, delay, power delay product (PDP), energy delay product (EDP), and area of 31.446 nW, 7.948 ps, 0.249 aJ, 1.986 × 10-30 Js, and 13,287 λ2, respectively. Similarly, the performance metrics, i.e., PDP and EDP are 0.597 aJ and 6.535 × 10-30 Js for standard quaternary NAND circuit and 0.099 aJ and 1.046 × 10-30 Js for standard quaternary NOR circuit, respectively. The proposed designs are superior in power consumption, PDP, and EDP in contrast to existing designs. The area occupancy and robustness of proposed standard quaternary inverter is also investigated by implementing layouts and performing Monte Carlo simulations. Further, the functionality of proposed quaternary logic gates is verified by using quaternary multiplier (QMUL) and quaternary half adder (QHA) as application examples. The proposed QMUL and QHA show PDP of 97.60 aJ and 95.937 aJ, respectively, which are quite encouraging when compared with literature. The new methodology for designing quaternary circuits reported in this work is expected to improve the performance of computing devices.

Similar content being viewed by others

Introduction

Over the years, the demand for energy-efficient and high-speed computing devices has significantly increased1,2,3. These computing devices require high-density integration for processing large amount of information at enhanced data rates. The conventional binary logic-based digital systems (with two distinct levels) are unfit for such modern computing devices, owing to interconnect issues associated with these systems4. The interconnections in integrated circuit designing using binary logic systems lead to energy consumption and propagation delay as the size of transistors is decreased5,6,7. As information density and processing speed increase, continuing with binary logic designs becomes increasingly challenging8.

The limitations of binary logic are well compensated by non-binary logic. Non-binary logic is often called multi-valued logic (MVL), for example, ternary logic and quaternary logic9. With the help of the MVL, more information can be transferred over a set of wires. Also, every register can hold a greater number of bits because interconnect complexity and chip area decrease10. It has been proved that among all radices, the ternary logic (radix 3) is the most efficient radix in terms of its hardware implementation11. However, using quaternary logic (radix 4) offers all the benefits of MVL systems, such as area reduction due to its fewer interconnects, and the important advantage of being easily interfaced with traditional binary logic circuits12.

Si-MOSFET technology has been used for designing MVL circuits for the last few years. However, in the era of nanoelectronics, as the technology goes beyond 32 nm, the Si-MOSFET technology failed to provide satisfactory results to design MVL-based circuits due to short channel effects (SCEs) and high leakage currents13,14,15. CNTFETs are highly suited for MVL systems due to their outstanding properties, such as high carrier mobility, scalability, and the ability to modify their threshold voltage by altering nanotube dimensions16. These features make CNTFETs efficient at supporting the accurate voltage levels required for multi-valued logic operations. Furthermore, CNTFETs exhibit better switching speed performance than traditional Si-MOSFET technology, making them a promising contender for next-generation logic designs17. Integrating MVL logic with CNTFETs could facilitate compact circuit layouts, reduce transistor counts, and improve computational throughput, addressing critical issues in advanced semiconductor technology18. Additionally, CNTFET-based MVL circuits hold capability for relevance in data storage and communication systems, where efficient encoding and processing of large-scale data are essential. Designing these circuits supports pursuing advanced computing concepts that fulfil the increasing demands of high-speed and low-power integrated systems. Examples of CNTFET-based ternary logic circuits include ternary logic gates19, ternary multipliers20,21, ternary half adders22, ternary flip-flops23, ternary full adders24, and ternary SRAM25. Examples of CNTFET-based quaternary logic circuits include quaternary logic gates9,26,27,28,29,30,31, quaternary decoders26,27,32, quaternary multiplexers33,34, quaternary half adders18,26,27,30, quaternary full adders17,33,34,35, quaternary multipliers26,30,36, quaternary successor and predecessor18,33.

The fundamental building blocks of MVL circuits are ternary and quaternary logic gates. The ternary and quaternary logic gates are used to design various ternary and quaternary arithmetic circuits, respectively37,38. For instance, if the power and delay of standard quaternary gates, namely standard quaternary inverter (SQI), standard quaternary NAND (SQNAND), and standard quaternary NOR (SQNOR), are reduced, it will result in an overall power-delay-product (PDP) and energy-delay-product (EDP) improvement of the circuit in which they are deployed. Shams ul Haq et al.38 and A. Paul et al.31 have proposed standard quaternary gates in the recent past. These standard quaternary gates have been used in the implementation of half adder, multiplier38, and asynchronous up/down counter39 circuits. The logic gates proposed by A. Paul et al.31 are more efficient than other designs in terms of power, energy, and fabrication cost. However, on the other hand, the logic gates proposed by Shams ul Haq38 are designed with the integration of resistive random-access memory (RRAM) and CNTFET technologies to have the advantages of low-power dissipation, improved delay, and low PDP, while achieving non-volatility. The application of hybrid CNTFET-RRAM technology exhibits potential for implementing desired logic, although the integration of these two technologies encounters specific device limitations. Reliability concerns become especially evident when scaling RRAM below 25 nm. A considerable issue emerges from the endurance limitations in CNTFET-RRAM technology.

Studies of literature pertaining to standard quaternary gates9,26,40 and their use in quaternary logic circuits reveal that there is dire demand for novel techniques based on quaternary gates and circuits that can deliver low-power and high-speed performance of systems in which they are deployed30,41.

QMUL is a fundamental arithmetic block in digital circuits, which is widely utilized in arithmetic logic units (ALUs), address calculation modules, floating-point units, and cache memories42. In26, the authors have presented a QMUL using quaternary transmission gates (QTGs). The main disadvantage of the designs is the excessive use of QTGs, which increases the number of transistors and power consumption. The utilization of QTGs is unnecessary when a fixed voltage is meant to be transferred. Their excessive usage has led to a high transistor count. In addition to this, three power supplies have been used in this design, which increases the number of connections thereby increasing cost of design and production43. In32, the authors have presented a single-VDD QMUL circuit using multiplexers. This design consists of two parts. The first part makes intermediate products through quaternary decoders and quaternary multiplexers. In the second part, the results obtained from the first stage are converted to quaternary values through an encoder. The voltage division occurs by constantly switched on transistors, which provide less resistance and cause far more static power dissipation than diode-connected transistors used in44. In41, QMUL has been designed using three supply voltages and standard quaternary NAND and NOR designs. The use of three power supplies leads to the elimination of voltage divisions but increases the complexity of connections undesirably and also causes increased static current, which contributes to power overheads40. To tackle the above-said challenges faced by the researchers, we have introduced energy-efficient quaternary logic circuits. The key features of proposed quaternary circuits are as follows:

-

i.

The proposed circuits deploy PTL and voltage divider approaches for enhancing power efficiency.

-

ii.

Besides this, the proposed circuits rely on a single supply, which can reduce the cost of design and production owing to fewer connections.

-

iii.

Effective chiral vector optimization has been performed in this work for various quaternary logic circuits so as to improve upon various performance parameters.

-

iv.

The proposed circuits showcase improvement not only in power consumption but also in the performance metrics, i.e., PDP and EDP, using 32 nm CNTFET technology. Further, comparative analysis has been established in terms of layout for SQI circuits and in terms of figure of merit (FOM) for quaternary multiplier and half adder circuits for highlighting the outstanding performance of proposed circuits.

This paper is organized into seven sections. Introduction introduces the motivation for designing the CNTFET-based quaternary logic circuits, research issues in designing quaternary circuits, and the advantages of CNTFET technology over Si-MOSFET technology. Multi-valued logic system explains quaternary logic systems. Carbon nanotube field effect transistor (CNTFET) explains the description of CNTFETs. Design evolution: from existing to proposed circuits briefly elaborates on existing CNTFET-based quaternary logic circuits and describes the proposed quaternary circuits. Result and discussion discussed the results of the proposed quaternary gates. The proposed quaternary multiplier and quaternary half adder are discussed and compared with existing designs in Application circuits using proposed designs. The paper is summarized in Conclusion.

Multi-valued logic system

Modern very large-scale integration (VLSI) technology requires faster data transmission using fewer interconnections. CNTFET-based quaternary logic circuits can be used to fulfil this requirement. A quaternary logic system uses four states to represent the functionality of a circuit45. The logic levels of a quaternary logic system with the corresponding voltage level have been represented in Table 1.

The quaternary inverter, quaternary NAND (QNAND), and quaternary NOR (QNOR) are commonly used quaternary logic gates. The quaternary logic gates design various quaternary logic circuits, such as quaternary decoders, quaternary comparators, quaternary multiplexers, quaternary adders, and quaternary multipliers. The quaternary inverter circuits can be further classified into four categories: positive quaternary inverter (PQI), intermediate quaternary inverter (IQI), negative quaternary inverter (NQI), and standard quaternary inverter (SQI). The functionality of the quaternary inverters can be expressed mathematically using the Eqs. (1)-(4)27.

The QNAND logic gate can be further categorized into four categories: positive quaternary NAND (PQNAND), intermediate quaternary NAND (IQNAND), negative quaternary NAND (NQNAND), and standard quaternary NAND (SQNAND). The functions of various QNAND gates are expressed using the following Eqs. (5)-(8):

Similarly, the QNOR logic gate can be classified into four categories: positive quaternary NOR (PQNOR), intermediate quaternary NOR (IQNOR), negative quaternary NOR (NQNOR), and standard quaternary NOR (SQNOR). The functionality of various QNOR logic gates can be represented using Eqs. (9)-(12):

The quaternary logic gates are essential building blocks in digital circuits. Designing a quaternary logic-based circuit requires nano transistors with multi-threshold voltage (multi-Vth) properties. Therefore, CNTFETs are the most suitable for designing quaternary logic circuits. The overview of CNTFET has been elaborated in the next section.

Carbon nanotube field effect transistor (CNTFET)

This section is subdivided into two subsections. “Structure of CNTFET” and “Characteristics of CNTFET” describe the structure and characteristics of the CNTFET device, respectively.

Structure of CNTFET

A CNTFET comprises carbon nanotubes (CNTs) that are prepared by rolling a graphene sheet into a cylindrical structure46. In a CNT, the direction of rolling a graphene sheet is called a chirality vector, represented using a pair (m, n) known as a chiral number47,48. The electrical and physical properties of CNT can be determined by chiral number. A CNTFET exhibits semiconductor property if the difference between m and n is neither a multiple of 3 (m-n ≠ 3) nor zero (m-n ≠ 0)49. In other cases, CNT would behave as metallic50. The diameter of CNT (DCNT) is determined by the chiral vector as defined in Eq. (13)51. The structure of the CNTFET with the conducting channel replaced by CNT is shown in Fig. 1. The key process parameters of the CNTFET include gate length (Lg), gate height (Hg), oxide thickness (Tox), CNT width (Wg), DCNT and CNT pitch (P). The relationship governing the dependence of Wg on P, DCNT, and the number of CNT (N) is presented in Eq. (13).

Where, a0 is the interatomic distance between each carbon atom and its neighbor, and Wmin is the minimum Wg established during the lithographic process.

In CNTFET technology, the threshold voltage (Vth) adjustment is easy and precise in comparison with Si-MOSFET technology. Hence, the quaternary logic circuits can be designed efficiently using CNTFET. The Vth of a CNTFET can be represented mathematically according to Eq. (15)52:

Where, a is the carbon-to-carbon atom distance. Equation (15) illustrates that an increase in DCNT (chiral vector) leads to decreases in Vth. This approach motivates the design of MVL circuits using MOSFET-like CNTFETs.

Characteristics of CNTFET

Figure 2(a) shows ID versus VDS curves for various VGS values. The plot shows that higher VGS values result in higher ID. Figure 2(b) shows the ID versus VGS plots of the CNTFET device. The plot infers that increasing chirality vector leads to higher ID. In Fig. 2(c), the Vth is analyzed against chiral values. It is evident that Vth decreases as chiral value increases. This analysis reveals the behaviour of the CNTFET device in different operating conditions, in particular demonstrating VGS and VDS influence on ID and Vth.

Design evolution: from existing to proposed circuits

This section is subdivided into two sections. Section 4.1 provides the comprehensive review of existing approaches used in designing SQI circuits. While Sect. 4.2 outlines the methodological details of the proposed SQI, SQNAND, and SQNOR circuits.

Existing circuits

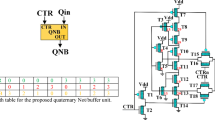

In SQI-127, the voltage division concept has been used to generate all quaternary voltage levels, as shown in Fig. 3(a). Voltage division refers to the distribution of high voltage levels into relatively lower voltage values. SQI-1 uses dedicated paths to generate four different logic levels at the output. Also, this design has diode-connected CNTFETs (T2, T3, T6, and T7) having a chiral value (19,0) in series between pull-up and pull-down CNTFETs in the middle part of the circuit. The diode-connected CNTFET behaves as a diode and allows the flow of current in one direction due to the inherent characteristics of the CNTFET structure.

The design of SQI-240 is depicted in Fig. 3(b) using 14 CNTFETs, including NQI, PQI, and IQI. Various paths have been used in this circuit to generate all four logic levels at the output. Logic ‘0’ and ‘3’ appear at the output through transistors T5 and T1, respectively. In this design, two independent paths are used to generate logic ‘1’ and logic ‘2’ levels. Therefore, there are more degrees of freedom to adjust the diameters of the nanotube at the cost of area.

The SQI-353 has been implemented using 10 CNTFETs, as displayed in Fig. 3(c). The design shows higher power consumption, as four out of ten CNTFETs in SQI are always turned ON. The design of SQI-430 used diode-connected CNTFETs to produce the quaternary voltage levels at the output as depicted in Fig. 3(d). This design utilized various paths to generate four logic levels at the output. The SQI-4 benefits from the advantages of diode-connected CNTFETs, which reduces the power consumption in static mode. SQI-531 is designed using a voltage divider and PTL concept as displayed in Fig. 3(e). The SQI-5 used only three different chirality, i.e., (8,0), (13,0), and (29,0). Other designs utilize at least four to six types of chirality in CNTFETs.

Proposed methodology

Having understood about the various SQI design approaches reported by the researchers in the recent past, this section describes the details of the proposed SQI (refer “Proposed SQI circuit”), SQNAND, and SQNOR circuits (refer “Proposed SQNAND and SQNOR circuits”).

Proposed SQI circuit

Figure 4 illustrates the proposed SQI circuit designed using 15 CNTFETs. The proposed SQI circuit has been implemented using a voltage divider and PTL configuration, wherein the intermediate branch of SQI-5 has been altered to generate voltage logic levels ‘1’ and ‘2’ with an improved critical path. It is important to note here that PTL configurations suffer from voltage degradation and reduced logic swing. However, these limitations of PTL are substantially mitigated through the utilization of CNTFET with a chiral vector of (29,0), exhibiting a low threshold voltage of approximately 0.19 V. CNTFETs inherently exhibit very low threshold voltages, which facilitates efficient carrier transport and significantly reduces voltage drop during signal transmission. Further, this characteristic ensures full swing output and preserves signal integrity, making the proposed quaternary logic gates suitable for complex multi-valued logic systems.

The voltage divider generates two voltage levels: V1 (0.3 V) and V2 (0.6 V) for logic ‘1’ and logic ‘2’, respectively, eliminating the need for additional power supplies. A voltage divider circuit31 has been constructed using three N-type CNTFETs with chiral value (13,0). The circuit is designed using four distinct paths for each logic level. Additionally, other inverter circuits, including PQI, NQI, and IQI27, have been utilized in the proposed SQI. The turning points of the proposed SQI circuit are displayed in Table 2.

When input is connected to logic ‘0’, the output of NQI is logic ‘3’, and T6 is turned ON, therefore, logic ‘3’ (0.9 V) is transferred to the output. When the input is connected at logic ‘1’, the output for PQI and IQI is logic ‘3’, whereas the output of NQI is logic ‘0’. Therefore, T7 and T8 are turned ON, producing logic ‘2’ as output. When input is connected to logic ‘2’, the output of PQI is logic ‘3’, and the output of NQI and IQI is logic ‘0’. So T13 and T14 are turned ON, and logic ‘1’ is sent to the output. When input = ‘3’, the output of PQI is logic ‘0’, and T15 is ON, so logic ‘0’ (0 V) is passed to the output. The transient response of the proposed SQI design is depicted in Fig. 5, which validates the functionality from Table 2.

Proposed SQNAND and SQNOR circuits

The proposed designs of SQNAND and SQNOR circuits are depicted in Figs. 6(a) and 6(b), using the same design methodology as the proposed SQI. The proposed SQNAND circuit has been designed using conventional PQNAND, IQNAND, and NQNAND circuits40. Similarly, the proposed SQNOR circuit utilized components of the conventional PQNOR, IQNOR, and NQNOR designs40. The proposed designs use a voltage divider circuit with chiral values (13,0) to produce intermediate logic levels. The proposed SQNAND and SQNOR designs use the following chiral values: (8,0), (13,0), and (29,0).

Furthermore, six transistors (3 P-type and 3 N-type CNTFETs) have been configured as pass transistors to transfer values from the input to the output paths. Tables 3 and 4 demonstrate the turning points of the proposed SQNAND and SQNOR circuits, respectively.

If either input A or B is at logic level ‘0’, the PQNAND, IQNAND, and NQNAND circuits each produce an output of logic ‘3’. Consequently, the output of the proposed SQNAND will also be logic ‘3’. When one input is at logic ‘1’ and the other is at logic ‘1’ or a higher level, both PQNAND and IQNAND generate an output of logic ‘3’, while the NQNAND produces logic ‘0’. As a result, the output of the SQNAND is logic ‘2’. If one input is at logic ‘2’ and the other is at logic ‘2’ or higher, the PQNAND gate outputs logic ‘3’, whereas both the IQNAND and NQNAND gates output logic ‘0’. Therefore, the output of the SQNAND gate is logic ‘1’. Finally, when both inputs are at logic level ‘3’, all three circuits, PQNAND, IQNAND, and NQNAND output logic ‘0’. Thus, the output of the SQNAND gate is logic ‘0’. The turning points of the proposed SQNAND and SQNOR circuits are tabulated in Tables 3 and 4, respectively. The proposed SQNOR gate operates similarly to the SQNAND gate, generating multi-level logic utilizing outputs from PQNOR, IQNOR, and NQNOR. Depending on the input combinations, the SQNOR gate produces outputs ranging from logic ‘0’ to ‘3’.

SQNAND and SQNOR are essential components for quaternary logic design. Transient response has been demonstrated to evaluate their functionality, as shown in Fig. 7. The input patterns include two inputs that transition simultaneously, and the output curves demonstrate proper functionality, as observed in Tables 3 and 4.

Result and discussion

For fair comparison, the proposed designs and earlier reported designs have been simulated in HSPICE at room temperature using the 32 nm Stanford University CNTFET model54. This section is organized into five subsections. The performance of proposed and earlier reported gates is compared in “Variation in supply voltage and process parameter” for variations in supply voltage (VDD). “Noise margin calculation” compares the noise margin (NM) performance of proposed and existing SQI, SQNAND, and SQNOR gates. The effect of process variations such as temperature, pitch, and number of CNTs is investigated in “Effect of process variations”. Monte Carlo (MC) simulation of the proposed SQI circuit is conducted for Pavg, Tpd, and NM in “Monte Carlo analysis”. The performance evaluation of various quaternary logic gates for different performance matrices is described in “Performance evaluation”. The CNTFET model parameter values considered for simulations are depicted in Table 5.

To evaluate the driving ability of designs, a load capacitor of 0.1 fF with a typical VDD of 0.9 V is considered for simulations. In the realistic environment the logic circuits (the quaternary logic gates, arithmetic circuits, etc.) will be used before digital signal processing stage for performing both arithmetic and logic functions55. The input capacitance of digital signal processing stage will be acting as a load to the quaternary logic gates as well as QMUL and QHA, which hover in the range from 0.1 fF to 5 fF. This is the reason for using 0.1 fF for simulation of gates as well as QMUL/QHA. Moreover, we have taken 0.1 fF as load capacitor in light of previously published articles. For instance, the existing QHA/QMUL circuits reported by various researchers have also adopted a range of capacitance values from 0.1 fF to 5 fF as a load26,32,41,56,57.

The layouts of various SQI circuits have been presented in Fig. 8. The layouts are designed using MOCMOS-CN library of Electric software. The SQI-1 can be considered as highly area efficient, as it consumes lowest area (6438 λ2) among considered SQI designs. On the other hand, SQI-5 consumes largest chip area (14250 λ2\(\:)\). The area of the proposed SQI is 13287 λ2, which is comparable with other SQI designs. The areas occupied by the voltage divider and PTL sections in the layout of the proposed SQI are 1957 λ2 and 11330 λ2, respectively.

Variation in supply voltage and process parameter

The impact of VDD variations on the proposed circuits is analyzed through simulations at 0.8 V, 0.9 V (typical), and 1 V, with results construed in “Variation in VDD for SQI circuits”, “Variation in VDD for SQNAND circuits”, and “Variation in VDD for SQNOR circuits” for SQI, SQNAND, and SQNOR circuits, respectively.

Variation in VDD for SQI circuits

Performance comparisons between the proposed SQI design and existing implementations are displayed in Fig. 9, highlighting four key parameters. The design of SQI-127 consumes maximum power among all SQI designs, as depicted in Fig. 9(a). The average power (Pavg) consumption for the proposed SQI design and SQI-531 is minimum among other SQI designs.

The impact of variations in VDD on the propagation delay (Tpd) of all the considered SQI designs is displayed in Fig. 9(b). The SQI-1 design27 shows lowest Tpd among all SQI designs but at the cost of higher power consumption. Further, two important FOM, i.e., PDP and EDP, are considered in this work for a fair comparison of different SQI circuits. The PDP and EDP versus VDD plots for various SQI designs are shown in Figs. 9(c, d), respectively. It is clear from Figs. 9(c, d) that the proposed SQI design outperforms other SQI designs in terms of PDP and EDP.

Variation in VDD for SQNAND circuits

Figure 10 depicts the impact of VDD variations on performance parameters, namely, Pavg, Tpd, PDP, and EDP, respectively. The Pavg, PDP, and EDP values increase while the Tpd values decrease with an increase in VDD. The proposed SQNAND shows the lowest values of Pavg as depicted in Fig. 10(a), while the SQNAND-127 infers lowest values of Tpd (refer to Fig. 10(b)). The proposed SQNAND and SQNAND-431 show the lowest PDP values (refer Fig. 10(c)). As far as EDP is concerned, the proposed SQNAND shows lowest values at 0.9 V and 1 V. At VDD=0.8 V, the EDP performance is lowest for SQNAND-431. The EDP values for the proposed SQNAND are high at VDD=0.8 V (refer to Fig. 10(d)) owing to a minute increase in Tpd at this voltage level (refer to Fig. 10(b)).

Variation in VDD for SQNOR circuits

The Pavg and Tpd versus VDD plots for various SQNOR designs considered in this work are depicted in Figs. 11(a, b), respectively. The Pavg for the proposed SQNOR design is remarkably low in contrast to other SQNOR designs depicted in Fig. 11(a). The Tpd for SQNOR-127 design is minimum, as depicted in Fig. 11(b). Similarly, PDP and EDP for all SQNOR designs at different VDD values are depicted in Figs. 11(c, d), respectively. From Figs. 11(c, d), it is evident that the proposed SQNOR design shows lowest values of PDP and EDP in contrast to other designs and is best suited to design energy-efficient circuits.

Noise margin calculation

This section describes the simulation methodology adopted for calculating noise margin (NM) and the corresponding results obtained for circuits considered in present research work. The voltage transfer characteristics (VTC) of the quaternary inverter and a visual representation of the quaternary NM are displayed in Fig. 12. According to the definition of quaternary NM, the output voltage levels are VO3, VO2, VO1, and VO0, while the input voltage levels are VI0, VIL1, VIH1, VIL2, VIH2, and VI3. The critical voltages are characterised by the slope (dVout/dVin) at -1, which determines the noise margin. For various SQI, SQNAND, and SQNOR logic gates, the NM at various logic levels is calculated using Eqs. (16–21), and the obtained results are depicted in Tables 6 and 7, and 8, respectively. The proposed design has the improved NM value.

The VTC curves for proposed designs of SQI, SQNAND, and SQNOR are depicted in Fig. 13. The SNM for proposed designs of SQI, SQNAND, and SQNOR are 124.20 mV, 91.69 mV, and 95.53 mV, respectively.

Effect of process variations

It is important to investigate the impact of process variations on digital circuits to validate their functionality. Therefore, the effect of variation in temperature, pitch, and number of CNT for proposed quaternary logic gates has been investigated in this section. The proposed quaternary logic gates have been analyzed at various temperature values ranging from 20 °C to 100 °C as displayed in Figs. 14(a, b). As the temperature increases, the Pavg and PDP also increase due to higher intrinsic carrier concentration and enhanced thermal energy.

The effect of pitch variation has been analyzed for proposed quaternary logic gates for values varying from 18 nm to 22 nm with a step size of 1 nm (refer Figs. 15(a, b)). With the increase in pitch variations, the Pavg and PDP values for all proposed quaternary logic gates slightly increases.

Number of CNT have also been varied for analysing their impact on the performance of proposed standard quaternary gates. As the number of CNTs increases, the drive current also increases, owing to which Pavg and PDP values also rises. Figure 16 illustrates the increase in power dissipation and PDP as the number of CNTs increases.

Monte Carlo analysis

Monte Carlo (MC) simulation has been performed to validate the reliability of the proposed SQI circuit. The reliability of the proposed SQI design is examined by random variation in the process parameters of CNTFET technology such as number of CNTs, oxide thickness, pitch, and channel length. MC simulation has been conducted for 100 iterations. The above-mentioned process parameters have an individual normal Gaussian distribution with ± 3σ = ±15%. Figure 17 shows the MC simulation results for the proposed SQI design at VDD of 0.9 V. The mean values for Pavg and Tpd for the proposed SQI are 29.049 nW and 7.20 ps, respectively which are very close to nominal values observed at typical process corner. The coefficient of variance calculated for Pavg and Tpd of SQI is 0.268 and 0.026 respectively. The low values of coefficient of variance for Pavg and Tpd confirms the robustness of the proposed SQI design.

The process variation for NM has been investigated to check the reliability of the proposed quaternary logic gates. Figure 18 depicts the NM analysis for various proposed quaternary logic gates with the variation in VDD.

Performance evaluation

The performance evaluation of various quaternary gates is presented in Tables 9 and 10 for different metrics such as Pavg, Tpd, PDP, EDP, and NM at a supply voltage of 0.9 V. The Pavg of the proposed SQI is 16.25, 10.03, 3.11, 5.72, and 1.14 times lower than SQI-1, SQI-2, SQI-3, SQI-4, and SQI-5, respectively. The proposed SQI demonstrates 10.03, 10.41, 3.11, 5.57, and 1.35 times lower PDP compared to SQI-1, SQI-2, SQI-3, SQI-4, and SQI-5, respectively. Further, the proposed SQI has an EDP 6.15, 10.73, 3.55, 5.38, and 1.59 times lower than SQI-1, SQI-2, SQI-3, SQI-4, and SQI-5, respectively. Similarly, the proposed SQNAND displays 3.76, 4.41, 4.68, and 3.29 times lower PDP than SQNAND-1, SQNAND-2, SQNAND-3, and SQNAND-4, respectively. Compared to SQNAND-1, SQNAND-2, SQNAND-3, and SQNAND-4, the EDP of the proposed SQNAND is 1.79, 3.20, 3.29, and 5.07 times lower, respectively. The proposed SQNOR exhibits 5.22, 9.37, 5.75, and 1.17 times lower PDP than SQNOR-1, SQNOR-2, SQNOR-3, and SQNOR-4, respectively. The EDP for the proposed SQNOR is 15.19, 60.68, 24.15, and 9.84 times lower than SQNOR-1, SQNOR-2, SQNOR-3, and SQNOR-4, respectively. The NM of the proposed SQI and27 is better than all other considered SQI designs. Besides this, the NM of the proposed SQNAND and SQNOR is better than designs reported in27] and [30.

Application circuits using proposed designs

Arithmetic circuits are essential digital systems that enable various mathematical operations such as addition, subtraction, multiplication, and division. These circuits must enhance the speed and efficiency of systems such as calculators, microprocessors, and digital signal processors.

Proposed multiplier circuit

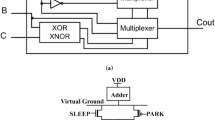

The QMUL circuit, as depicted in Fig. 19, has been designed and analyzed using the proposed SQNAND circuit. There are four building blocks for the QMUL circuit, namely, voltage divider, quaternary to binary decoder, product circuit, and carry circuit. Two voltage levels, V1 (0.3 V) and V2 (0.6 V), are generated through the voltage divider circuit as displayed in Fig. 4. The structure of QMUL utilizes these voltage levels to replace multiple power supplies with a single supply.

A quaternary to binary decoder35 has been used to decode a quaternary input into a binary output as displayed in Fig. 19(a). When the input value of A is 0, 1, 2, and 3, then the respective binary signals A0, A1, A2, and A3 are high. Similarly, when the value of input B is 0, 1, 2, and 3, then the binary signals B0, B1, B2, and B3 are high, respectively.

The design structure used in41 has been used to design product and carry circuits for the proposed QMUL as displayed in Figs. 19(b, c). “B” and “Q” symbols indicate binary and quaternary gates, respectively. The outputs generated from the quaternary to binary decoder have been forwarded as inputs to product and carry circuit. The product of two quaternary numbers is generated using the product circuit (QMUL) from Fig. 19(b), and carry is produced at the output (QCarry) through carry circuit from Fig. 19(c). The K-map for product and carry circuits of the proposed quaternary multiplier is depicted in Fig. 20.

The logic expressions for product and carry circuits of the quaternary multiplier obtained from Fig. 20 are expressed using Eqs. (23)-(24).

The transient response of the proposed quaternary multiplier has been depicted in Fig. 21 with all possible combinations. The output of the proposed quaternary multiplier is consistent with its performance for inputs A and B.

The performance parameters for the various quaternary multiplier circuits are shown in Table 11. A comparison has been made with literature. The FOM (PDP*No. of CNTFETs) has been adopted for a fair comparison of the proposed quaternary multiplier with earlier reported quaternary multipliers. The proposed multiplier circuit outperforms other multipliers in terms of Pavg and PDP. Besides this, FOM of the proposed multiplier and26 are better than other existing designs. This is evident that the proposed quaternary multiplier is a power efficient circuit. Table 12 demonstrates the number of devices and transistor count used to design the proposed quaternary multiplier.

Proposed half adder circuit

Another arithmetic circuit, the quaternary half adder (QHA) circuit, has been designed using the proposed SQNAND and SQNOR circuits as depicted in Figs. 22(a)-22(b). The building blocks for the proposed QHA circuit are namely a voltage divider, quaternary to binary decoder, a sum circuit (refer to Fig. 22(a)), and a carry generator circuit (refer to Fig. 22(b)).

The structure utilized in41 was employed to design sum and carry generating circuits for the proposed QHA. The outputs of the quaternary to binary decoder were used as inputs in the sum and carry generator circuit. The sum of two quaternary numbers is computed using the sum circuit, and the carry is produced at the output via the carry circuit. Figure 23 depicts the K-map for the sum and carry generating circuits of the proposed QHA.

The logic expression for sum and carry circuits of quaternary half adder obtained from Fig. 23 are expressed using Eqs. (25)-(26).

The transient response for the proposed QHA has been depicted in Fig. 24, which validates the working operation for inputs A and B. The performance parameters for the various QHA circuits are shown in Table 13, which shows the improvement of the proposed QHA. Existing circuits require several power supplies, whereas the proposed circuits are designed using one power supply. Though the single supply voltage approach uses more number of voltage levels to achieve output logic levels, it offers numerous advantages over multiple supply voltage approach. First, it offers fewer number of interconnections, thereby reducing complexity and cost of production of the design. Second, it has only one source of short circuit dynamic power (occurring at logic level equal to half of VDD) in contrast to multiple sources in case of multiple supply voltage approach58. The FOM (PDP* No. of CNTFETs) has been used to compare the proposed QHA to previously reported circuits. The proposed QHA circuit performs better in terms of Pavg and PDP. Aside from that, the FOM of the suggested half adder and56 outperforms previous designs. It is clear that the proposed QHA is a power-efficient circuit. Table 14 shows the number of devices and transistors utilized to design the proposed QHA. The transistor counts for QMUL and QHA are 241 and 218 respectively. The proposed QMUL/QHA circuits can be used to design quaternary full adder (QFA) and quantum multiplier–accumulator (QMAC) as well as higher order adder and multiplier circuits as the manufacturing methodology using CNTFET devices has grown in recent years. One of the finest examples for the same is the work reported in59, wherein a 16-bit microprocessor comprising more than 14,000 CNTFETs has been fabricated using industry-standard design flows and processes.

Conclusion

In this paper, novel designs of quaternary logic gates, viz., SQI, SQNAND, and SQNOR using CNTFET technology have been proposed. The proposed designs outperformed existing circuits in terms of average power consumption, PDP, and EDP. The proposed SQI exhibits 10.03, 10.41, 3.11, 5.57, and 1.35 times lower PDP than SQI-1, SQI-2, SQI-3, SQI-4, and SQI-5, respectively. Also, the EDP for the proposed SQI is 6.15, 10.73, 3.55, 5.38, and 1.59 times lower than SQI-1, SQI-2, SQI-3, SQI-4, and SQI-5, respectively. Similarly, the proposed designs of SQNAND and SQNOR gates performed better than existing designs in terms of PDP and EDP. Besides this, two combinational circuits, namely quaternary multiplier and quaternary half adder, have been designed using proposed designs of SQNAND and SQNOR. The proposed quaternary multiplier and quaternary half adder provide superior performance in terms of average power consumption and PDP. The quaternary logic circuits proposed in this work are anticipated to improve the performance of computing devices.

Data availability

All data generated or analyzed during this study are included within this article.

References

Deng, J. & Wong, H. S. P. A compact SPICE model for Carbon-Nanotube Field-Effect transistors including nonidealities and its Application—Part I: model of the intrinsic channel region. IEEE Trans. Electron. Devices. 54 (12), 3186–3194. https://doi.org/10.1109/TED.2007.909030 (2007).

Deng, J. & Wong, H. S. P. A compact SPICE model for Carbon-Nanotube Field-Effect transistors including nonidealities and its Application—Part II: full device model and circuit performance benchmarking. IEEE Trans. Electron. Devices. 54 (12), 3195–3205. https://doi.org/10.1109/TED.2007.909043 (2007).

Patil, N., Deng, J., Mitra, S. & Wong, H. S. P. Circuit-level performance benchmarking and scalability analysis of carbon nanotube transistor circuits. IEEE Trans. Nanotechnol. 8 (1), 37–45. https://doi.org/10.1109/TNANO.2008.2006903 (2009).

Sandhie, Z. T., Patel, J. A., Ahmed, F. U. & Chowdhury, M. H. Investigation of multiple-valued logic technologies for beyond-binary era. ACM Comput. Surv. 54(1) (online) (2021). https://www.scopus.com/inward/record.uri?eid=2-s2.0-85105383347&partnerID=40&md5=ec6b7444581babb9968647d1b979da18.

Moaiyeri, M. H., Hajmohammadi, Z., Khezeli, M. R. & Jalali, A. Effective reduction in crosstalk effects in quaternary integrated circuits using mixed carbon nanotube bundle interconnects. ECS J. Solid State Sci. Technol. 7 (5), M69–M. https://doi.org/10.1149/2.0111805jss (2018).

Shrivastava, Y. & Gupta, T. K. Efficient noise immune robust ternary subtractor designs. In Proceedings of Second International Conference on Computational Electronics for Wireless Communications. 397–409. (2023).

Kulkarni, M. & Chen, T. A sensitivity based approach to analyzing signal delay uncertainty of coupled interconnects. In International Symposium on Signals, Circuits and Systems. Proceedings, SCS 2003. (Cat. No.03EX720). 331–336 (2004). https://doi.org/10.1109/ISQED.2004.1283696

Jaber, R. A., Kassem, A., El-Hajj, A. M., El-Nimri, L. A. & Haidar, A. M. High-Performance and Energy-Efficient CNFET-Based designs for ternary logic circuits. IEEE Access. 7, 93871–93886. https://doi.org/10.1109/ACCESS.2019.2928251 (2019).

Moaiyeri, M. H., Mirzaee, R. F., Doostaregan, A., Navi, K. & Hashemipour, O. A universal method for designing low-power carbon nanotube FET-based multiple-valued logic circuits. IET Comput. Digit. Tech. 7 (4), 167–181. https://doi.org/10.1049/iet-cdt.2013.0023 (2013).

Tabrizchi, S., Sharifi, H., Sharifi, F. & Navi, K. A novel design approach for ternary compressor cells based on CNTFETs. Circuits Syst. Signal. Process. 35 (9), 3310–3322. https://doi.org/10.1007/s00034-015-0197-z (2016).

Hurst, S. L. Multiple-Valued Logic Its Status and Its Future (1984).

Datla, S. R. P. R. & Thornton, M. A. Quaternary voltage-mode logic cells and fixed-point multiplication circuits. Proc. Int. Symp. Mult. Log.. 128–133 (2010). https://doi.org/10.1109/ISMVL.2010.32

Sharma, A., Sohal, H. & Sharma, K. Area and power analysis of adiabatic 2×1 multiplexer design on 65 nm CMOS technology. In 5th International Conference on Wireless Networks and Embedded Systems (WECON). 1–6 (2016). https://doi.org/10.1109/WECON.2016.7993489.

Haq, S., Abbasian, E., Khurshid, T. & Basha, S. J. Design analysis of a low-power, high-speed 8 T SRAM cell using dual-threshold CNTFETs. Phys. Scr. 99. https://doi.org/10.1088/1402-4896/ad61ca (2024).

Sharma, K., Thakur, S., Elangovan, M. & Sachdeva, A. Low-power FinFET based boost converter design using dynamic threshold body biasing technique. Int. J. Numer. Model. Electron. Netw. Dev. Fields. 37 (2), e3165. https://doi.org/10.1002/jnm.3165 (2024).

Sharifi, F., Moaiyeri, M. H., Sharifi, H., Navi, K. & Thapliyal, H. On the design of quaternary arithmetic logic unit based on CNTFETs. Int. J. Electron. Lett. 7 (1), 1–13. https://doi.org/10.1080/21681724.2017.1409804 (2019).

Lakshmanachari, S. et al. Design and analysis of a novel compact quaternary adder. Int. J. Syst. Assur. Eng. Manag. 15 (7), 3076–3087. https://doi.org/10.1007/s13198-024-02316-9 (2024).

Pendashteh, Y. & Hosseini, S. A. A low complexity Multi-Valued logic successor and predecessor in nanoelectronics. Majlesi J. Electr. Eng. 18 (1), 335–347. https://doi.org/10.30486/mjee.2024.1996028.1254 (2024).

Lin, S., Kim, Y. B. & Lombardi, F. CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10 (2), 217–225. https://doi.org/10.1109/TNANO.2009.2036845 (2011).

Aljaam, J. M., Jaber, R. A. & Al-Maadeed, S. A. Novel ternary adder and multiplier designs without using decoders or encoders. IEEE Access. 9, 56726–56735. https://doi.org/10.1109/ACCESS.2021.3072567 (2021).

Abbasian, E., Nayeri, M., High-Speed, A. & Low-Energy One-Trit ternary multiplier circuit design in CNTFET technology. ECS J. Solid State Sci. Technol. 12 (2), 021004. https://doi.org/10.1149/2162-8777/acb8d9 (2023).

Vidhyadharan, S. & Dan, S. S. An efficient Ultra-Low-Power and superior performance design of ternary half adder using CNFET and Gate-Overlap TFET devices. IEEE Trans. Nanotechnol. 20, 365–376. https://doi.org/10.1109/TNANO.2020.3049087 (2021).

Moaiyeri, M. H., Jooq, M. K. Q., Al-Shidaifat, A. & Song, H. Breaking the limits in ternary logic: an Ultra-Efficient Auto-Backup/Restore nonvolatile ternary Flip-Flop using negative capacitance CNTFET technology. IEEE Access. 9, 132641–132651. https://doi.org/10.1109/ACCESS.2021.3114408 (2021).

Bastani, N. H., Moaiyeri, M. H. & Navi, K. An Energy- and Area-Efficient approximate ternary adder based on CNTFET switching logic. Circuits Syst. Signal. Process. 37 (5), 1863–1883. https://doi.org/10.1007/s00034-017-0627-1 (2018).

Khurshid, T. & Singh, V. Design of unbalanced 9:2 ternary encoder and 2:9 ternary decoder circuits in resistive random access memory and carbon nanotube field effect transistor technology. Int. J. Circuit Theory Appl. 52 (10), 5403–5426. https://doi.org/10.1002/cta.4022 (2024).

Moaiyeri, M. H., Navi, K. & Hashemipour, O. Design and evaluation of CNFET-based quaternary circuits. Circuits Syst. Signal. Process. 31 (5), 1631–1652. https://doi.org/10.1007/s00034-012-9413-2 (2012).

Ebrahimi, S. A., Reshadinezhad, M. R., Bohlooli, A. & Shahsavari, M. Efficient CNTFET-based design of quaternary logic gates and arithmetic circuits. Microelectron. J. 53, 156–166. https://doi.org/10.1016/j.mejo.2016.04.016 (2016).

Sharifi, F., Moaiyeri, M. H., Navi, K. & Bagherzadeh, N. Robust and energy-efficient carbon nanotube FET-based MVL gates: A novel design approach. Microelectron. J. 46 (12), 1333–1342. https://doi.org/10.1016/j.mejo.2015.09.018 (2015).

Doostaregan, A. & Abrishamifar, A. Evaluating a methodology for designing CNFET-Based ternary circuits. Circuits Syst. Signal. Process. 39 (10), 5039–5058. https://doi.org/10.1007/s00034-020-01400-2 (2020).

Doostaregan, A. & Abrishamifar, A. On the design of robust, low power with high noise immunity quaternary circuits. Microelectron. J. 102. https://doi.org/10.1016/j.mejo.2020.104774 (2020).

Paul, A. & Pradhan, B. Novel design of power-efficient quaternary logic gates using CNTFET. Int. J. Electron. https://doi.org/10.1080/00207217.2023.2210300 (2023).

Davari Shalamzari, Z., Dabbaghi Zarandi, A. & Reshadinezhad, M. R. Newly multiplexer-based quaternary half-adder and multiplier using CNTFETs. AEU - Int. J. Electron. Commun. 117. https://doi.org/10.1016/j.aeue.2020.153128 (2020).

Roosta, E. & Hosseini, S. A. A Novel multiplexer-based quaternary full adder in nanoelectronics. Circuits Syst. Signal Process. 38(9), 4056–4078 (2019). https://doi.org/10.1007/s00034-019-01039-8.

Hosseini, S. A. & Roosta, E. A novel low complexity and energy-efficient method to implement quaternary logic function in nanoelectronics. Microelectron. J. 102. https://doi.org/10.1016/j.mejo.2020.104821 (2020).

Fakhari, S., Hajizadeh Bastani, N. & Moaiyeri, M. H. A low-power and area-efficient quaternary adder based on CNTFET switching logic. Analog Integr. Circuits Signal. Process. 98 (1), 221–232. https://doi.org/10.1007/s10470-018-1367-2 (2019).

Rahmati, S., Farshidi, E. & Ganji, J. Low energy and area efficient quaternary multiplier with carbon nanotube field effect transistors. ETRI J. 43(4), 717–727 (2021). https://doi.org/10.4218/etrij.2020-0045

Chauhan, K. & Bansal, D. Noise tolerant and power optimized ternary combinational circuits for arithmetic logic unit. e-Prime - Adv. Electr. Eng. Electron. Energy 11, 100912 (2024). https://doi.org/10.1016/j.prime.2025.100912

ul Haq, S., Abbasian, E., Khurshid, T. & Sharma, V. K. Energy-efficient design of quaternary logic gates and arithmetic circuits using hybrid CNTFET-RRAM technology. Phys. Scr. 99 (8), 85119. https://doi.org/10.1088/1402-4896/ad6194 (2024).

Paul, A. & Pradhan, B. Design of ternary and quaternary asynchronous up/down counter using CNTFET. AEU - Int. J. Electron. Commun. 179, 155323. https://doi.org/10.1016/j.aeue.2024.155323 (2024).

Daraei, A. & Hosseini, S. A. Novel energy-efficient and high-noise margin quaternary circuits in nanoelectronics. AEU - Int. J. Electron. Commun. 105, 145–162. https://doi.org/10.1016/j.aeue.2019.04.012 (2019).

Sharifi, F., Moaiyeri, M. H., Navi, K. & Bagherzadeh, N. Ultra-low-power carbon nanotube FET-based quaternary logic gates. Int. J. Electron. 103 (9), 1524–1537. https://doi.org/10.1080/21681724.2016.1138506 (2016).

Haq, S. U., Orouji, M., Khurshid, T. & Abbasian, E. An efficient design methodology for a tri-state multiplier circuit in carbon nanotube technology. Phys. Scr. 100 (1), 15008. https://doi.org/10.1088/1402-4896/ad9646 (2025).

Jafari, M., Sayedsalehi, S., Mirzaee, R. F. & Farazkish, R. Design of new low-power and high-speed quaternary flip-flops based on CNTFETs, Comput. Electr. Eng. 117, 109235 (2023). https://doi.org/10.1016/j.compeleceng.2024.109235.

Ebrahimi, S. A., Reshadinezhad, M. R., Bohlooli, A. & Shahsavari, M. Efficient CNTFET-based design of quaternary logic gates and arithmetic circuits. Microelectron. J. 53, 156–166. https://doi.org/10.1016/j.mejo.2016.04.016 (2016).

Fakhari, S., Bastani, N. H. & Moaiyeri, M. H. A low-power and area-efficient quaternary adder based on CNTFET switching logic. Analog Integr. Circuits Signal. Process. 98 (1), 221–232. https://doi.org/10.1007/s10470-018-1367-2 (2019).

Elangovan, M., Sharma, K., Sachdeva, A. & Gupta, L. Read Improved and Low Leakage Power CNTFET Based Hybrid 10t SRAM Cell for Low Power Applications. Vol. 43 (Springer, 2024). https://doi.org/10.1007/s00034-023-02529-6.

Sachdeva, A., Gupta, L., Sharma, K. & Elangovan, M. Based Bit-Line powered stable SRAM design for low power applications. ECS J. Solid State Sci. Technol. 12 (4), 041006. https://doi.org/10.1149/2162-8777/accb67 (2023).

Singh, A., Khosla, M. & Raj, B. Design and analysis of electrostatic doped Schottky barrier CNTFET based low power SRAM. AEU - Int. J. Electron. Commun. 80, 67–72. https://doi.org/10.1016/j.aeue.2017.06.030 (2017).

Sachdeva, A., Sharma, K., Bhargava, A. & Abbasian, E. A CNTFET based stable, single-ended 7T SRAM cell with improved write operation. Phys. Scr. 99 (3), 35011. https://doi.org/10.1088/1402-4896/ad24a8 (2024).

Haq, S., Abbasian, E., Orouji, M., Loan, S. A. & Khurshid, T. Synthesis of a CNTFET-based ternary full adder using a carry-less ternary half adder. IEEE Trans. Comput. Des. Integr. Circuits Syst. 1. https://doi.org/10.1109/TCAD.2025.3569764 (2025).

Ul Haq, S., Abbasian, E., Sharma, V. K., Khurshid, T. & Fathi, H. Energy-efficient high-speed dynamic logic-based one-trit multiplier in CNTFET technology. AEU - Int. J. Electron. Commun. 175, 155088 (2023). https://doi.org/10.1016/j.aeue.2023.155088

Raychowdhury, A., Member, S. & Roy, K. Carbon-nanotube-based voltage-mode multiple-valued logic design. In IEEE Transactions on Nanotechnology. 4(2), 168–179 (2005).

Daraei, A. & Hosseini, S. A. Alternative design techniques of quaternary latch, flip-flops and counters in nanoelectronics. Int. J. Electron. 109 (4), 669–698. https://doi.org/10.1080/00207217.2021.1941286 (2022).

Deng, G. W. J. & Lin, A. Stanford CNFET model - HSPICE. In Stanford Nanoelectronics Lab (2019). https://nano.stanford.edu/stanford-cnfet-model-hspice.

Vijeyakumar, K. N., Sumathy, V. & Elango, S. VLSI implementation of Area-Efficient truncated modified booth multiplier for signal processing applications. Arab. J. Sci. Eng. 39 (11), 7795–7806. https://doi.org/10.1007/s13369-014-1329-7 (2014).

Jafari, M., Sayedsalehi, S., Faghih, R. & Razieh, M. Design of high – performance quaternary half adder, full adder, and multiplier. Analog Integr. Circuits Signal. Process. 122 (2), 1–14. https://doi.org/10.1007/s10470-025-02317-z (2025).

Sharifi, F., Moaiyeri, M. H. & Navi, K. A novel quaternary full adder cell based on nanotechnology. Int. J. Mod. Educ. Comput. Sci. 7 (3), 19–25. https://doi.org/10.5815/ijmecs.2015.03.03 (2015).

Haq, S. U. & Sharma, V. K. Ternary encoder and decoder designs in RRAM and CNTFET technologies. e-Prime - Adv. Electr. Eng. Electron. Energy. 7. https://doi.org/10.1016/j.prime.2023.100397 (2024).

Hills, G. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 572(7771), 595–602 (2019). https://doi.org/10.1038/s41586-019-1493-8

Acknowledgements

Authors are thankful to Manipal University Jaipur, Jaipur for their lab. support.

Funding

Open access funding provided by Manipal University Jaipur.

Author information

Authors and Affiliations

Contributions

Ajay Rupani: Methodology, Analysis and Writing-Original draft. Deepika Bansal: Supervision, Formal Verification, and Writing Reviewing. Kulbhushan Sharma: Supervision, Writing Reviewing. All authors have declared and agreed to publish this research article.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Rupani, A., Bansal, D. & Sharma, K. Energy-efficient design of CNTFET-based quaternary arithmetic circuits. Sci Rep 15, 31533 (2025). https://doi.org/10.1038/s41598-025-16335-4

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-16335-4