Abstract

Power electronic converters are widely used in various fields of electrical equipment. Due to their fast dynamics and non-linear nature, controlling them requires dealing with various complexities. Therefore, having a well-designed, high-speed, and robust controller is critical to ensure the effective operation of these devices. In a DC-DC converter, steady-state performance with minimum error and fast dynamic response relies on controller design. This paper presents the design of a multi-stage PID controller with an N-filter combined with a one plus proportional derivative (1+PD) controller. This controller illustrates fast tracking reference voltage; additionally, it shows incredible results when the DC-DC converter operates in different modes. The parameters of the proposed controller are effectively determined using the golden eagle optimization (GEO) algorithm. Furthermore, a comprehensive comparison between the proposed controller, proportional–integral–derivative (PID), and fractional order PID (FOPID) controllers, as well as different metaheuristic optimization methods in various conditions, has been conducted to demonstrate the effectiveness of the proposed controller. The behavior of the closed-loop system under different conditions has been thoroughly investigated. The superior time and frequency domain characteristics of the closed-loop system with the PIDn(1+PD) controller highlight its superiority over other controllers. The demonstrated enhancements in settling time, voltage regulation accuracy, and transient response emphasize the potential applicability of the proposed control strategy in real-world power electronics systems, particularly in scenarios requiring high efficiency, stability, and dynamic performance.

Similar content being viewed by others

Introduction

Power electronic converters, such as DC-DC converters, are integral components in a wide array of electrical equipment, ranging from consumer electronics to industrial machinery1,2. Buck converters are utilized in renewable energy systems (RES) and DC microgrids3,4, electrical vehicles (EVs)5,6, electrical motors7,8, fast and wireless charging equipment’s5,9,10,11, electronics and internet of things (IoTs) applications12,13,14. These converters play a critical role in regulating voltage levels, ensuring efficient power transfer, and maintaining the stability of electrical systems. However, the fast dynamics and non-linear nature of DC-DC converters pose significant challenges for control design15,16. To achieve optimal performance, it is essential to develop controllers that not only respond swiftly to dynamic changes but also maintain robust performance across various operating conditions17.

The design and performance of controllers in DC-DC buck converters have been extensively studied, with various controllers proposed to enhance performance18. Traditional PID controllers are commonly used due to their simplicity and effectiveness19,20. However, more advanced controllers like the FOPID and tilt integral derivative (TID) controllers have been introduced to improve performance further21,22. In recent studies, PID, FOPID, TID and self-adaptive Fuzzy-PID controllers have been utilized to control buck converters and power quality enhancement23,24,25,26, demonstrating different advantages. The FOPID controller, for instance, has shown superior performance in handling the non-linear behavior of converters and electrical machines27,28, while the TID controller offers robust stability and improved dynamic response29. This sets the stage for the exploration of optimization algorithms to further enhance these controllers’ effectiveness.

To optimize the parameters of these controllers, various metaheuristic optimization algorithms have been employed. Algorithms such as the aquila optimizer (AO)30,31, African vultures optimization algorithm (AVOA)32,33, hunger games search (HGS)34, and fitness-distance balance based Runge-Kutta (FDBRUN)35 have been used to fine-tune controller coefficients, resulting in enhanced performance metrics like integral absolute error (IAE), integral square error (ISE), integral time absolute error (ITAE), and integral time squared error (ITSE)36,37,38. The integration of metaheuristic algorithms like grey wolf optimization (GWO) has shown promising results in improving the stability and disturbance rejection behavior of controllers for power converters23,39,40. Additionally, hybrid approaches41,42,43, such as the artificial ecosystem-based optimization integrated with the Nelder-Mead method (AEONM), have been proposed to combine global search capabilities with local optimization for more precise tuning42. These optimization techniques have been critical in improving the steady-state and dynamic responses of buck converters, making them more robust and efficient44. However, despite these advancements, there remains a need for controllers that can provide even faster tracking and better performance across various modes of operation.

Hekimoğlu and Ekinci21 employs a novel approach for tuning PID controller parameters in a DC-DC buck converter. The study introduces the WOASAT algorithm, a hybrid of the whale optimization algorithm and simulated annealing, enhanced with a tournament selection mechanism. Sangeetha, et al.45 proposes an improved golden jackal optimization (IGJO) algorithm to optimally tune a FOPID controller for a DC-DC buck converter. Based on this, the IGJO algorithm combines the golden jackal optimization algorithm with the capuchin search algorithm to enhance its ability to explore and exploit for finding the best FOPID parameters. In another study, Shayeghi et al.46 proposed a multi-stage PD(1 + PI) controller for a DC-DC buck converter. This controller cascades a proportional-derivative (PD) stage with a one-plus-proportional-integral (1 + PI) stage. The parameters of the PD(1 + PI) controller are optimized using the mayfly optimization algorithm (MOA) to minimize the ITAE. Similarly, Isen35, utilizes a novel approach for optimizing the parameters of PID, FOPID, and TID controllers for DC-DC buck converters using a hybrid metaheuristic algorithm called FDBRUN. The proposed FDBRUN algorithm effectively optimizes the parameters of FOPID controllers, leading to improved transient response, robustness, and overall performance enhancement for DC-DC buck converter systems compared to traditional tuning methods.

Izci et al.42 introduced a new hybrid optimization algorithm called AEONM, which combines the artificial ecosystem optimization (AEO) algorithm with the Nelder-Mead (NM) method. This AEONM algorithm showed improved optimization capabilities and effectiveness in designing PID controllers for buck converter systems. Fong et al.47 explores the application of the Archimedes optimization algorithm (AOA) for tuning PID controllers in DC-DC buck converters. The AOA is a metaheuristic method inspired by Archimedes’ principle, which has shown superior performance in various benchmark tests compared to other optimization algorithms like particle swarm optimizer (PSO), genetic algorithm (GA), sine cosine algorithm (SCA), and equilibrium optimizer (EO). Ersali and Hekimoğlu48 introduced a new hybrid metaheuristic algorithm called opposition-based cooperation search algorithm with Nelder-Mead (OCSANM) to tune the parameters of a FOPID controller for a DC-DC buck converter system. This controller provides a fast, high-performance solution by combining proportional, derivative, and integral actions in a multi-stage architecture optimized by the MOA. Nanyan et al.49 introduced the improved sine cosine algorithm (ISCA), an upgraded version of the SCA, to optimize PID controller parameters for a DC-DC buck converter. The ISCA-PID controller demonstrated superior performance in terms of transient response, frequency response, integral error metrics, disturbance rejection, and robustness to parameter variations. Table 1 summarizes the key features and optimization methods used in these studies for tuning DC-DC buck converter controllers.

In the field of power electronics, DC-DC buck converters are crucial for regulating voltage in various applications. Despite progress in controller design, achieving fast and accurate voltage tracking remains a challenge, especially during changing conditions. This study aims to tackle this issue by proposing a new controller, PIDn(1+PD), optimized with the GEO algorithm. Existing research highlights the need for better converter performance across different modes, requiring new control methods. By combining advanced control techniques with optimization algorithms, this research aims to improve transient response and frequency characteristics. Through experiments, we aim to show how the PIDn(1+PD) controller surpasses traditional ones like PID and FOPID. Ultimately, this work seeks to advance power electronics by introducing a new control approach that enhances converter performance and paves the way for future developments.

The primary contributions of this paper are as follows:

-

(a)

Innovative controller design: This paper introduces a novel multi-stage controller. The advanced design enables fast tracking of reference voltages, delivering robust performance across different operational modes. By integrating the N-filter and the (1+PD) component, the proposed controller minimizes overshoot and enhances stability, setting a new benchmark in control design.

-

(b)

Optimization method: The proposed controller employs the GEO algorithm for precise tuning of its parameters. The GEO algorithm’s ability to explore a broad solution space and converge on optimal settings enhances the controller’s performance significantly. This optimization ensures that the controller maintains high efficiency and reliability, even in complex and dynamic environments.

-

(c)

Comprehensive comparison: This paper conducts extensive comparative analyses between the proposed PIDn(1+PD) controller and conventional PID and FOPID controllers. By evaluating a range of performance metrics, such as rise time, settling time, overshoot, and steady-state error, under different operating conditions, the paper demonstrates the superior performance and versatility of the proposed controller.

-

(d)

Performance evaluation: A detailed evaluation of the closed-loop system’s behavior is conducted in both time and frequency domains. The results showcase the proposed controller’s ability to achieve minimal steady-state error, rapid dynamic response, and robust performance. This comprehensive analysis confirms the controller’s effectiveness in maintaining high performance under a wide range of operations.

-

(e)

Robustness and stability: The robustness and stability of the proposed controller are rigorously tested against various disturbances and parameter variations. The results highlight the controller’s capacity to maintain performance integrity, proving it to be a reliable choice for practical applications in power electronics. The design’s ability to adapt to changing conditions without compromising stability underscores its potential for widespread industrial adoption.

The paper is organized as follows: section “Mathematical model of DC-DC buck converter” covers the mathematical model of the DC-DC buck converter. Section “Motivation to use the proposed controller and optimization method” discusses the motivation to use the proposed controller and optimization method and describe the multi-stage PIDn(1+PD) controller. Section “Buck converter with proposed controller” details the placement and operation of the controller in the DC-DC buck converter, along with the optimization method. Section “Simulation and discussion” includes the simulation and analysis. Lastly, section “Conclusions and future research directions” concludes the paper.

Mathematical model of DC-DC buck converter

Buck converters, commonly employed across various electrical sectors such as computing power supplies, mobile devices, electric vehicles, and televisions, perform the task of reducing higher magnitudes of direct current (DC) voltage to lower levels. This conversion is achieved through pulse-width modulation (PWM) control, regulating the output voltage. A typical buck converter, shown in Fig. 1, consists of at least one FET power switch (MOSFET, S), a diode (D), an inductor (L), a capacitor (C), and a resistor (R) as a load. In this configuration, the inductor serves the purpose of energy storage, while the capacitor is integrated into the output to reduce voltage ripple.

In a complete switching cycle with a period \({T_{s~}}\), where \({T_{on~}}\)represents the time the switch S is on/closed and \({T_{off}}\) represents the time it is off/open, the duty cycle (D) is set by the control loop. Equations (1) and (2) shows relation between \({T_{s~}}\), \({T_{on~}}\), \({T_{off~}}\)and duty cycle respectively.

The state equations of the buck converter are determined based on Kirchhoff’s circuit laws, which are expressed through the following relations depending on the open or closed state of the S switch:

-

Close mode switch.

-

Open mode switch.

In most power supply applications, the output voltage is controlled by adjusting the duty cycle. Therefore, in converter control studies, understanding the transfer function from diode (the Laplace transform of the duty cycle) to output voltage \(({V_o})\) is crucial. Small-signal alternating Current (AC) transfer functions can be derived using either the switching flow-graph (SFG) method or the classical method of determining the averaged state-space model. It’s important to note that both methods yield the same results. Buck converter waveforms are shown in Fig. 2. By applying Laplace transform to the averaged equations of (3) and (4), the average state-space equation of the buck converter can be expressed as follows:

Given the initial conditions are assumed to be zero, the transfer function of the buck converter from diode to \({V_o}\) can be calculated as follows:

Buck converter small-signal (dynamic) model is depicted in Fig. 3. The parameters for the buck converter under study, utilized for simulation purposes, are detailed in Table 2.

By using the values from the provided Table 2, we can generate an open-loop step response for the buck converter shown in Fig. 4. This response reflects a change in the duty cycle ratio, resulting in a 12 V shift in the output voltage. As shown in Fig. 4, the open-loop response of the buck converter displays a high overshoot and a lengthy settling time. To improve these aspects, we can employ a proposed controller, which is a straightforward and efficient solution. Details about this controller are discussed in the following subsection.

Motivation to use the proposed controller and optimization method

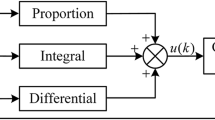

Proposed multi-stage controller PIDn(1+PD)

This controller amalgamates a PID controller with an N-filter for enhanced performance, effectively curbing oscillations and overshoot while swiftly adapting to dynamic process changes. Additionally, integrating the PD controller ensures rapid stabilization and robust control, empowering the system to achieve optimal setpoint tracking and disturbance rejection, even in intricate, nonlinear systems.

Compared to traditional PID controllers, the PIDn(1+PD) configuration boasts several key advantages. Firstly, the inclusion of the N-filter results in smoother response characteristics, minimizing oscillations and overshoot that commonly plague conventional PID control. This translates to enhanced system stability and better transient response, ultimately leading to tighter regulation of process variables. Furthermore, the PD component augments the PIDn module by providing anticipatory control action, enabling preemptive correction of deviations from setpoints. This feature proves invaluable in scenarios requiring swift responses to disturbances or changing operating conditions. Moreover, when compared to FOPID controllers, the PIDn(1+PD) design demonstrates superior robustness and simplicity in tuning, thanks to its intuitive structure and clearly defined parameters. Leveraging the strengths of both PIDn and PD control elements, this innovative controller emerges as a versatile solution capable of tackling the intricate control challenges encountered in various sectors.

Finally, the multi-stage PIDn(1+PD) control method is used in the DC-DC buck converter because it effectively addresses the dynamic challenges found in power electronics systems. While traditional PID controllers work efficiently in many applications, they often have difficulty handling the disturbances and fast changes required by modern power converters. The innovative multi-stage PIDn(1+PD) controller combines the advantages of a high-order PIDn with a proportional-derivative (PD) component, creating a more robust control strategy that enhances performance in several important methods.

The PIDn element offers improved tuning capabilities to manage the system’s complex dynamics and increase precision in voltage regulation. This higher-order approach allows for finer adjustments, leading to reduced steady-state errors and improved system stability. Moreover, the PD component provides predictive control, which enhances the converter’s transient response by quickly reacting to rapid changes in load conditions. By integrating these components, the multi-stage PIDn(1+PD) controller effectively reduces overshoot and settling time, which are crucial for maintaining output quality and efficiency in various operating modes. Block diagram of proposed controller is demonstrated Fig. 5.

The choice of the (1+PD) structure over the conventional PD controller is driven by several factors that enhance both performance and robustness, particularly in the context of DC-DC Buck Converters. The inclusion of the unity term (1) serves to improve the low-frequency behavior of the controller. In systems such as DC-DC converters, maintaining accurate control at lower frequencies or in steady-state conditions is essential. A pure PD controller may not sufficiently address steady-state error, which can persist under low-frequency conditions or disturbances. By incorporating the unity term, the controller ensures a continuous correction even at low frequencies, effectively reducing the steady-state error. Furthermore, the unity term contributes to enhancing the stability and robustness of the control system, providing an additional degree of control in both transient and steady-state phases. It helps mitigate the sensitivity to parameter variations and external disturbances, common in real-world power electronics applications. The inclusion of this term also complements the optimization capabilities of the GEO algorithm, allowing for more flexible tuning and better optimization results. This combination enables the (1+PD) controller to provide smoother multi-stage control, better transient response, and enhanced accuracy, making it a superior choice for the application at hand.

The open-loop transfer function of the first stage controller is shown as Eq. (11):

The second stage provide stability and fine-tuned control for DC-DC buck converter. The open-loop transfer function of the second stage controller is shown as Eq. (12):

The open-loop representation of the proposed controller can be depicted by Eq. (13).

While the additional zero in the proposed controller results in a + 20 dB/dec slope in the Bode plot, which could amplify high-frequency noise, practical measures are implemented to mitigate this. Specifically, a low-pass filter is applied at the output of the controller to prevent the amplification of high-frequency switching noise, commonly found in power electronics circuits. This filter is tuned to have a cutoff frequency just above the system’s desired bandwidth, ensuring that the controller’s performance within the operating frequency range remains intact while high-frequency noise is effectively attenuated. Additionally, the term (\({K_D}Ns/s+N\)) in the transfer function introduces a pole that limits the high-frequency gain, functioning as a derivative filter. By carefully tuning the parameter ‘N,’ the controller further minimizes the impact of high-frequency noise. These combined strategies—low-pass filtering and derivative filtering—ensure that the benefits of the additional zero are retained without sacrificing the controller’s practical applicability in power electronics systems. In real-world applications, additional signal conditioning techniques such as proper grounding, shielding, and input signal filtering can be employed to further minimize high-frequency interference. Finally, Eq. (14) illustrates the closed-loop system.

Selection of optimization method

The selection of the GEO algorithm for estimating the parameters of the PIDn(1+PD) controller in the DC-DC buck converter is motivated by GEO’s exceptional capability to navigate complex optimization landscapes with high precision and efficiency. GEO is a new and efficient optimization algorithm, and its efficiency has comparatively been shown through benchmark functions and engineering optimization problems. The GEO algorithm is inspired by the intelligent hunting and migration strategies of golden eagles, which allows it to balance exploration and exploitation effectively. This balance is crucial for optimizing the control parameters in proposed model, where the system’s performance can be sensitive to parameter variations and require a finely tuned solution to achieve optimal results. The GEO algorithm’s adaptive search mechanism enables it to efficiently explore the search space for the best parameter set, minimizing the risk of getting trapped in local optima, a common challenge in optimization problems. By employing the GEO algorithm, the PIDn(1+PD) controller can achieve superior performance metrics, such as reduced steady-state error, faster transient response, and improved robustness against disturbances. Additionally, GEO’s relatively simple implementation and fast convergence make it an attractive choice for DC-DC buck converter.

Buck converter with proposed controller

Figure 6 depicts the block diagram of the buck converter system incorporating a PIDn(1+PD) controller. In this diagram, \({V_{ref}}\left( s \right)\), \(E\left( s \right)\), and \({V_o}\left( s \right)\), represent the reference voltage, error voltage, and output voltage, respectively. Utilizing the parameters listed in Tables 2 and 3, we derive the unity feedback closed-loop transfer function of the buck converter as Eq. (15).

The purpose of the controller design is to enhance the dynamic characteristics of the system while eliminating the steady-state error in the converter response. This involves minimizing the integral of the system response deviation from the desired value, denoted as \(\:e\left(t\right)\). With semiconductor technologies driving high-speed dynamics in converter switches, it’s crucial to maintain or even improve the response speed of the closed-loop system. Therefore, alongside minimizing the integral of the system response deviation, we must also consider the speed or time taken to clear the error. To address these requirements effectively, the ITAE is selected as the optimization cost function (CF), defined as Eq. (16):

The CF is restricted by the range of controller coefficients, defining the search space for the optimization problem as presented in Table 4. Also, Table 3 demonstrates the optimal gain obtaiend with proposed controller and GEO algorithm. The GEO optimization algorithm was iteratively executed in five distinct rounds. Using 50 iterations and participation of 10 particles, the GEO algorithm effectively identifies the optimal controller coefficient values. The duration of the simulation is \(t=6 \times {10^{ - 6}}~s\). Similar to the other metaheuristic approaches, there are parameters that affect the efficiency of the GEO algorithm apart from population size and maximum number of iterations. The studies in the literature employ the two parameters of the GEO by setting them as follows: Propensity to attack (\({P_a}=\left[ {0.5,~2} \right]\)) and propensity to cruise (\({P_c}=\left[ {1,~0.5} \right]\)). In this regard, we have adopted similar parameters for the optimization of DC-DC Buck converter system.

Table 5 illustrates the highest, lowest, and mean CF values attained across various controllers. Figure 7 depicts the detailed flowchart showcasing the proposed controller and the GEO algorithm, utilized to improve the performance of the DC-DC buck converter’s voltage control system. Figure 8 offers a comparative examination through boxplots of five distinct algorithms: GEO, hippopotamus optimization algorithm (HO), pelican optimization algorithm (POA), PSO and GA. evaluating their effectiveness in minimizing the objective function. Notably, the boxplot in Fig. 8 demonstrates that the poorest result achieved by the GEO algorithm significantly outperforms the best results obtained by fourth the HO, POA, PSO and GA algorithms. This underscores the pronounced superiority of the proposed GEO algorithm in terms of performance. Also Fig. 9 shows CF values of different algorithms with proposed controller. Figure 7 includes the Golden Eagle image, which is sourced from Vitalentum.net.

Transient response analysis

In the evaluation of controllers within the time domain, certain fundamental measurements such as rise time (\({T_r}\)), settling time (\({T_s}\)), percent overshoot (\(OS\)), and peak time (\({T_p}\)) hold considerable importance. In Fig. 10, we can observe the step response of the buck converter system using the proposed controller, which has been fine-tuned through the GEO algorithm. Table 6 provides a comprehensive breakdown of performance metrics across different controller strategies in the time domain, encompassing parameters such as \({T_r}\), \({T_s}\), \(OS\), and \({T_p}\). By analyzing the numerical data in the table alongside the step response visuals in the figure, it’s clear that the GEO/PIDn(1+PD) controller showcases the most desirable transient response characteristics, including no overshoot, fast settling time, and swift rise time.

To enable a comprehensive numerical comparison, calculations and reporting on time domain evaluation metrics have been conducted across various scenarios. These metrics include the ISE, ITSE, IAE, and ITAE. The corresponding equations for these metrics are outlined in equations (17) through (20).

Where, K is simulation time in s, and \(e\left( t \right)\) is an error signal between reference voltage and output voltage in DC-DC buck converter. Table 7 represents value of different cost function.

Frequency response

When assessing controllers in the frequency domain, key factors like gain margin, phase margin, and bandwidth play a pivotal role. In Fig. 11, we observe the Bode plot of the buck converter system employing proposed controller, designed through GEO algorithm. Table 8 provides performance metrics for all approaches in the frequency domain, covering parameters such as gain margin, phase margin, and bandwidth. Comparing the numerical results in the table with the Bode plots in the figure, it becomes evident that the GEO/PIDn(1+PD) controller exhibits the most stable frequency response.

Simulation and discussion

In this section, the proposed PIDn(1+PD) controller is operationalized and integrated into the DC-DC buck converter control mechanism as discussed earlier in section “Motivation to use the proposed controller and optimization method”. Moreover, these findings show a strong correlation between the results obtained from classical controllers54,55. Subsequently, the closed-loop system is implemented using MATLAB 2023a with Simulink.

Analyzing a DC-DC buck converter in different operating contexts provides valuable insights into its versatility and performance. Through careful examination, it is possible to understand how the converter can have a suitable output with different input voltages, load conditions, and element values. Such an analysis helps to understand the behavior and performance characteristics of the converter. By studying its response to different operating parameters, we can achieve a deeper understanding of the capabilities and limitations of the converter and design a controller that has minimum loss of efficiency and maximum efficiency against these fluctuations. Basically, a comprehensive analysis of the buck DC-DC converter in different operating scenarios allows us to evaluate the appropriate performance of the designed controller.

Scenario I: analyzed system in different 3 steps

- Step 1::

-

Setting the initial reference voltage.

- Step 2::

-

Shifting to another output voltage level.

- Step 3::

-

Applying the disturbance in the output voltage.

At first, the output voltage level is set at 12 V (Vref = 12 V). After establishing this initial voltage, the reference voltage is decreased from 12 to 6 V at \(t=2 \times {10^{ - 6}}~s\). Subsequently, at \(t=4 \times {10^{ - 6}}~s\), a sudden positive disturbance of 1 V change emerges in the converter output voltage, necessitating swift resolution. This error in the output represents a significant disturbance, with the reference voltage at 6 V, constituting more than 16% of the disturbance visible at the output. This disturbance is assumed to manifest as a step increase of + 1 V at the output of the converter as shown in Fig. 12. Figure 12 shows the output voltage of the closed-loop buck converter during reference voltage changes and disturbances by employing proposed and different PID controllers. Figure 13 shows the output voltage of the closed-loop buck converter during reference voltage changes and disturbances by employing proposed and different FOPID controllers.

Scenario II: performance of DC-DC Buck converter in uncertainty inductance

The performance of DC-DC buck converters is critical in various electronic applications, particularly in efficiently regulating voltage. One significant factor influencing their performance is the inductance within the circuit. In this section, we investigate the impact of inductance uncertainty on the performance of a DC-DC buck converter. Specifically, we examine two scenarios. Through the analysis of these scenarios, our objective is to demonstrate the exceptional performance of the proposed controller and highlight its significant difference compared to other controllers under identical conditions.

Increase inductance + 10% to 1.1 (mH)

A 10% increase in inductance to 1.1 (mH) can induce substantial alterations in converter behavior. This rise might compromise the converter’s capacity to regulate voltage effectively, potentially resulting in fluctuations in output voltage and ripple. However, these effects can be mitigated through the design of a robust controller, ensuring a reliable output. The proposed controller offers this assurance compared to alternative controllers.

Decrease inductance − 10% to 0.9 (mH)

On the other hand, a decrease in inductance by ten% to 0.9 (mH) also presents challenges for the DC-DC buck converter’s performance. A reduction in inductance can alter the converter’s dynamics, affecting its transient response and overall stability. The decreased inductance may lead to higher ripple currents and voltage spikes, posing potential risks to the converter and other components in the circuit. As depicted in Table 9, the values demonstrate the remarkable performance of the proposed controller in comparison to others.

Scenario III: performance of DC-DC Buck converter in uncertainty capacitor

Another element that affects the efficiency and reliability of DC-DC buck converters is the capacitors used in their circuits. In this section, we examine how uncertainty in capacitor values affects the performance of such converters. In particular, we investigate two scenarios. By analyzing these scenarios, we aim to demonstrate the performance of the proposed controller in the condition that the circuit capacitors are defective.

Increase capacitor + 10% to 110 \(\mu F\)

A slight boost of 10% in capacitance to 110 (\(\mu F\)) can greatly impact the performance of the DC-DC buck converter. This adjustment might disrupt the converter’s capability to uphold a steady voltage output, leading to fluctuations in voltage regulation and ripple suppression.

Decrease capacitor − 10% to 90 \(\mu F\)

On the other hand, a 10% decrease in capacitance to 90 (\(\mu F\)) creates obstacles for the buck DC-DC converter performance. Decreasing capacitance may impair the converter’s ability to filter noise and react to sudden changes, possibly compromising its stability. With less capacity, there is a risk of increased voltage waves and reduced energy storage capacity, which can threaten the converter and other circuit components. As depicted in Table 10, the values demonstrate the remarkable performance of the proposed controller in comparison to others.

Scenario IV: performance of DC-DC Buck converter in uncertainty resistance

Another element that the performance of DC-DC buck converters is strongly dependent on is resistance. This resistance usually adjusts the voltage and current in the buck converter. In this part, we will examine the effect of uncertainty in the resistance values on the performance of the DC-DC buck converter. In particular, we examine two scenarios. By examining these scenarios, our goal is to reveal the effect of the strong controller in compensating the sudden increase or decrease in resistance in the buck converter circuit.

Increase resistance + 20% to 7.2 \(\:\varOmega\:\)

A 20% increase in resistance to 7.2 (\(\:\varOmega\:\)) can significantly change the behavior of the buck DC-DC converter. This change may impair the converter’s ability to regulate voltage effectively, potentially leading to output voltage fluctuations and increased power losses.

Decrease resistance − 20% to 4.8 \(\:\varOmega\:\)

On the other side, a 20% reduction in resistance to 4.8 (\(\:\varOmega\:\)) poses challenges for DC-DC buck converter performance. Reduced resistance may affect the converter’s current control capabilities and efficiency, potentially affecting its overall stability. Lower resistance levels can lead to increased current flow and increased power dissipation, creating hazards for the converter and other components in the circuit. As depicted in Table 11, the values demonstrate the remarkable performance of the proposed controller in comparison to others.

Conclusions and future research directions

This study introduced and analyzed the performance of a new multi-stage PIDn(1+PD) controller for DC-DC buck converters, with parameters optimized using the GEO algorithm. Our research shows the controller’s exceptional ability to achieve fast-tracking voltages and maintain robust performance across different operating modes. A thorough comparison with traditional PID and advanced FOPID controllers, along with various metaheuristic optimization techniques, confirms the superiority of the proposed controller. The PIDn(1+PD) controller demonstrates improved time and frequency domain characteristics, proving its effectiveness in handling the non-linear and fast dynamic nature of DC-DC converters. Using the GEO algorithm for parameter optimization has been successful in enhancing the controller’s performance, ensuring minimal steady-state error and a quick dynamic response. This innovative approach addresses the complexities inherent in power electronic converters, offering a high-speed, robust solution that outperforms existing controllers. Overall, the findings of this research provide valuable insights into the design and optimization of controllers for DC-DC buck converters, advancing the field of power electronics.

The PIDn(1+PD) controller, with its optimized parameters, stands out as a reliable and efficient solution, paving the way for future developments in this area. The practical applicability of the proposed PIDn(1+PD) controller in power electronics systems is reinforced by the mitigation strategies employed to handle high-frequency noise. By integrating a low-pass filter and derivative filtering, the controller is capable of attenuating high-frequency noise while maintaining the advantages provided by the additional zero in the transfer function. This ensures that the proposed controller can operate effectively in real-world power electronics environments, where high frequency switching signals are prevalent. Additionally, the robust design, coupled with practical considerations such as signal conditioning, makes this controller suitable for industrial applications requiring high stability, precision, and dynamic performance.

Future research endeavors could explore several avenues aimed at extending and refining the findings of this study. Firstly, there is a pressing need for hardware implementation to validate the proposed control strategy’s efficacy in real-world applications, thereby bridging the divide between theoretical analysis and practical deployment. Robustness analysis emerges as a critical domain, necessitating investigation into the controller’s resilience against diverse operating conditions, including load variations, input voltage perturbations, and voltage fluctuations, thereby ensuring stability and reliability across a spectrum of scenarios. Furthermore, the exploration of multi-objective optimization techniques presents a promising trajectory, enabling the simultaneous optimization of efficiency, transient response, and cost-effectiveness to meet the multifaceted demands of contemporary power electronics applications. Adaptive control strategies represent a compelling avenue for research, wherein dynamic parameter adjustment in response to evolving operating conditions could enhance adaptability and performance robustness in dynamic environments. Moreover, the integration of the proposed control strategy with renewable energy systems warrants scrutiny, with a focus on augmenting overall system efficiency and stability in distributed power generation contexts, thereby advancing the paradigm of sustainable energy conversion. By embarking on these research trajectories, the field stands poised to realize substantial advancements in the domain of power electronics, fostering innovation and addressing emerging challenges in energy conversion and management.

Data availability

The datasets used and/or analyzed during the current study available from the corresponding author on reasonable request.

Abbreviations

- \(DC\) :

-

Direct current

- \(GEO\) :

-

Golden eagle optimization

- \(EV\) :

-

Electric vehicle

- \(RES\) :

-

Renewable energy systems

- \(PID\) :

-

Proportional–integral–derivative

- \(FOPID\) :

-

Fractional order PID

- \(IoT\) :

-

Internet of thing

- \(TID\) :

-

Tilt-integral-derivative

- \(AO\) :

-

Aquila optimizer

- \(AVOA\) :

-

African vulture’s optimization algorithm

- \(HGS\) :

-

Hunger games search

- \(FDBRUN\) :

-

Fitness-distance balance based Runge Kutta

- \(ITAE\) :

-

Integral of time-weighted absolute error

- \(IAE\) :

-

Integral of absolute error

- \(ITSE\) :

-

Integral of time-weighted square error

- \(ISE\) :

-

Integral of square error

- \(GWO\) :

-

Grey wolf optimization

- \(AEONM\) :

-

Artificial ecosystem-based optimization integrated with the Nelder-Mead method

- \(WOASAT\) :

-

Whale optimization algorithm and simulated annealing

- \(IGJO\) :

-

Improved grasshopper jaya optimization

- \(AC\) :

-

Alternating current

- \(D\) :

-

Duty cycle

- \({F}_{S}\) :

-

Switching frequency

- \(POA\) :

-

Pelican optimization algorithm

- \(CF\) :

-

Cost function

- \({\Delta v}\) :

-

Voltage error between reference and actual angular voltage

- \({K}_{P}\) :

-

Proportional gains of multi-stage controller

- \({K}_{D}\) :

-

Derivative gains of multi-stage controller

- \(PI\) :

-

Proportional-Integral

- \(PD\) :

-

Proportional derivative

- \(MOA\) :

-

Mayfly optimization algorithm

- \(OCSANM\) :

-

Opposition-based cooperation search algorithm with Nelder- Mead

- \(AEO\) :

-

Artificial ecosystem optimization

- \(NM\) :

-

Nelder-Mead

- \(AOA\) :

-

Archimedes optimization algorithm

- \(GA\) :

-

Genetic algorithm

- \(SCA\) :

-

Sine cosine algorithm

- \(EO\) :

-

Equilibrium optimizer

- \(PSO\) :

-

Particle swarm optimization

- \(ISCA\) :

-

Improved sine cosine algorithm

- \(PWM\) :

-

Pulse-width modulation

- \({T}_{s}\) :

-

Switching time

- \({T}_{on}\) :

-

The duration of the switch is open

- \({T}_{off}\) :

-

The duration of the switch is close

- \(SFG\) :

-

Switching flow-graph

- \({i}_{L}\) :

-

Inductor current

- \({i}_{C}\) :

-

Capacitor current

- \({i}_{R}\) :

-

Resistance current

- \({V}_{G}\) :

-

Input voltage

- \({V}_{O}\) :

-

Output voltage

- \({V}_{ref}\) :

-

Referenced voltage

- \(E(s)\) :

-

Error signal between reference voltage and actual voltage

- \(HO\) :

-

Hippopotamus optimization

- \(e(t)\) :

-

Error value between reference voltage and actual voltage

- \({V}_{dist}\) :

-

Disturbance voltage

- \({K}_{I}\) :

-

Integral gains of multi-stage controller

- \(N\) :

-

Low-pass filter gain

References

Wang, H. & Blaabjerg, F. Reliability of capacitors for DC-link applications in power electronic converters—an overview. IEEE Trans. Ind. Appl. 50(5), 3569–3578 (2014).

Rahimpour, S., Husev, O., Vinnikov, D., Kurdkandi, N. V. & Tarzamni, H. Fault management techniques to enhance the reliability of power electronic converters: an overview. IEEE Access. 11, 13432–13446 (2023).

Farajdadian, S., Hajizadeh, A. & Soltani, M. Recent developments of multiport DC/DC converter topologies, control strategies, and applications: a comparative review and analysis. Energy Rep. 11, 1019–1052 (2024).

Rajamallaiah, A., Karri, S. P. K. & Sankar, Y. R. Deep reinforcement learning based control strategy for voltage regulation of DC-DC Buck converter feeding CPLs in DC microgrid. IEEE Access. (2024).

Kim, J. C., Lee, J., Lee, H. W., Park, C. B. & Lee, J. B. Comparison of buck-type DC-DC converter design for electric vehicle wireless charging system using railway power grid. J. Electr. Eng. Technol. 19(4), 2787–2801 (2024).

Surya, S. & Williamson, S. S. A comprehensive study on DC–DC and DC–AC converters in electric and hybrid electric vehicles. E-Mobility: New Era Autom. Technol. 2022, 59–81 (2022).

Manoj, E. & Yuvaraju, M. Bidirectional electric vehicle application using isolated DC-DC converter fed DC motor. In Advanced Technologies in Electric Vehicles 405–411 (Elsevier, 2024).

Kumar, D., Choudhary, S. D. & Tabrez, M. An approach for commutation current ripple alleviation in BLDCM drive using novel DC-DC converter. Int. J. Power Electron. 19(1), 24–52 (2024).

Saadaoui, A. & Ouassaid, M. Super-twisting sliding mode control approach for battery electric vehicles ultra-fast charger based on Vienna rectifier and three-phase interleaved DC/DC buck converter. J. Energy Storage 84, 110854 (2024).

Rathore, V., Reddy, S. R. P. & Rajashekara, K. An isolated multilevel DC–DC converter topology with hybrid resonant switching for EV fast charging application. IEEE Trans. Ind. Appl. 58(5), 5546–5557 (2022).

Shalbaf, A. A., Shahidi, N. & Hemati, M. A high-gain interleaved DC-DC converter with reduced components for EV charging application. Comput. Electr. Eng. 118, 109316 (2024).

Kang, B., Na, J. H. & Song, H. J. Analysis of a buck dc-dc converter for smart electronic applications. J. Korean Soc. Ind. Convergence 22(3), 373–379 (2019).

Zhao, M. et al. An ultra-low quiescent current tri-mode DC-DC buck converter with 92.1% peak efficiency for IoT applications. IEEE Trans. Circ. Syst. I Regul. Pap. 69(1), 428–439 (2021).

Park, Y. J. et al. A design of a 92.4% efficiency triple mode control DC–DC buck converter with low power retention mode and adaptive zero current detector for IoT/wearable applications. IEEE Trans. Power Electron. 32(9), 6946–6960 (2016).

Nduwamungu, A., Lie, T. T., Lestas, I., Nair, N. K. C. & Gunawardane, K. Control strategies and stabilization techniques for DC/DC converters application in DC MGs: challenges, opportunities, and prospects—a review. Energies 17(3), 669 (2024).

Xu, Q. et al. Review on advanced control technologies for bidirectional DC/DC converters in DC microgrids. IEEE J. Emerg. Sel. Top. Power Electron. 9(2), 1205–1221 (2020).

Ekinci, S. et al. Frequency regulation of PV-reheat thermal power system via a novel hybrid educational competition optimizer with pattern search and cascaded PDN-PI controller. Results Eng. 2024, 102958. (2024).

Mostafa, J. Efficient DC motor speed control using a novel multi-stage FOPD(1 + PI) controller optimized by the Pelican optimization algorithm. Sci. Rep. (2024).

Ounnas, D., Guiza, D., Soufi, Y., Dhaouadi, R. & Bouden, A. Design and Implementation of a digital PID controller for DC–DC Buck converter. In 1st International Conference on Sustainable Renewable Energy Systems and Applications (ICSRESA) 1–4 (IEEE, 2019).

Samosir, A. S., Sutikno, T. & Mardiyah, L. Simple formula for designing the PID controller of a DC-DC buck converter. Int. J. Power Electron. Drive Syst. 14(1), 327 (2023).

Hekimoğlu, B. & Ekinci, S. Optimally designed PID controller for a DC-DC buck converter via a hybrid whale optimization algorithm with simulated annealing. Electrica 20(1), 19–27 (2020).

Adeel, M., Fayyaz, U., Rafi, U. & Farooq, M. U. Design of a buck converter with an analogue PI controller for wide load range applications. In 4th International Conference on Computing, Mathematics and Engineering Technologies (iCoMET) 1–5 (IEEE, 2023).

Zafar, F. et al. Stabilization and tracking control of underactuated ball and beam system using metaheuristic optimization based TID-F and PIDD2–PI control schemes. Plos One 19(2), e0298624 (2024).

Mishra, A. K., Ray, P. K., Mallick, R. K., Mohanty, A. & Das, S. R. Adaptive fuzzy controlled hybrid shunt active power filter for power quality enhancement. Neural Comput. Appl. 33, 1435–1452 (2021).

Mishra, A. K. et al. PSO-GWO optimized fractional order PID based hybrid shunt active power filter for power quality improvements. IEEE Access. 8, 74497–74512 (2020).

Mishra, A. K., Nanda, P. K., Ray, P. K., Das, S. R. & Patra, A. K. IFGO optimized self-adaptive fuzzy-PID controlled HSAPF for PQ enhancement. Int. J. Fuzzy Syst. 25(2), 468–484 (2023).

Femi, R., Sree Renga, T., Raja & Shenbagalakshmi, R. Performance comparison of optimization algorithm tuned PID controllers in positive output re-lift Luo converter operation for electric vehicle applications. IETE J. Res. 69(12), 9394–9412 (2023).

Jabari, M. & Rad, A. Optimization of speed control and reduction of torque ripple in switched reluctance motors using metaheuristic algorithms based PID and FOPID controllers at the edge. Tsinghua Sci. Technol. (2024).

Nicola, M. & Nicola, C. I. Comparative performance analysis of the dc-ac converter control system based on linear robust or nonlinear PCH controllers and reinforcement learning agent. Sensors 22(23), 9535 (2022).

Sasmal, B., Hussien, A. G., Das, A. & Dhal, K. G. A comprehensive survey on aquila optimizer. Arch. Comput. Methods Eng. 30(7), 4449–4476 (2023).

Aribowo, W., Supari, S. & Suprianto, B. Optimization of PID parameters for controlling DC motor based on the aquila optimizer algorithm. Int. J. Power Electron. Drive Syst. 13(1), 216 (2022).

Ghazi, G. A. et al. African vulture optimization algorithm-based PI controllers for performance enhancement of hybrid renewable-energy systems. Sustainability 14(13), 8172 (2022).

Salah, B. et al. African vulture optimization-based optimal control strategy for voltage control of islanded DC microgrids. Sustainability 14(19), 11800 (2022).

Kumar, S. A., Narayana, M. S. S. & Gowd, K. J. AApplication of a TID controller for the LFC of a multi area system using HGS algorithm. Appl. Sci. Res. Eng. Technol. 13(3), 10691–10697 (2023).

Isen, E. Determination of different types of controller parameters using metaheuristic optimization algorithms for buck converter systems. IEEE Access. 10, 127984–127995 (2022).

Gupta, A. K., Kumar, D., Reddy, B. M. & Samuel, P. BBBC based optimization of PI controller parameters for buck converter. In 2017 Innovations in Power and Advanced Computing Technologies (i-PACT) 1–6 (IEEE, 2017).

Llama, M., Flores, A., Garcia-Hernandez, R. & Santibañez, V. Heuristic global optimization of an adaptive fuzzy controller for the inverted pendulum system: experimental comparison. Appl. Sci. 10(18), 6158 (2020).

Mohammed, I. K. & Abdulla, A. I. Balancing a Segway robot using LQR controller based on genetic and bacteria foraging optimization algorithms. TELKOMNIKA (Telecommuni Comput. Electron. Control). 18(5), 2642–2653 (2020).

Senthil Kumar, R., Mohana, K., Sundaram & Tamilselvan, K. Hybrid reference current generation theory for solar fed UPFC system. Energies 14(6), 1527 (2021).

Sekar, K., Arasan, E. & Chandrasekaran, K. Grey Wolf Optimization and Fed Fast Terminal Sliding mode controllers based on interleaved boost converters for symmetric pv systems under asymmetric partial shading. Symmetry 15(7), 1339 (2023).

Aribowo, W. et al. A Novel Hybrid Prairie Dog optimization algorithm-marine predator algorithm for tuning parameters Power System stabilizer. J. Rob. Control (JRC) 4(5), 686–695 (2023).

Izci, D., Hekimoğlu, B. & Ekinci, S. A new artificial ecosystem-based optimization integrated with nelder-mead method for PID controller design of buck converter. Alexandria Eng. J. 61(3), 2030–2044 (2022).

Ekinci, S., Izci, D., Eker, E. & Abualigah, L. An effective control design approach based on novel enhanced aquila optimizer for automatic voltage regulator. Artif. Intell. Rev. 56(2), 1731–1762 (2023).

Abdollahzadeh, M., Mollaee, H., Ghamari, S. M. & Khavari, F. Design of a novel robust adaptive neural network-based fractional‐order proportional‐integrated‐derivative controller on DC/DC Boost converter. J. Eng. 4, e12255 (2023).

Sangeetha, S., Revathi, B. S., Balamurugan, K. & Suresh, G. Performance analysis of buck converter with fractional PID controller using hybrid technique. Robot. Auton. Syst. 169, 104515 (2023).

Shayeghi, H., Rahnama, A., Takorabet, N., Thounthong, P. & Bizon, N. Designing a multi-stage PD (1 + PI) controller for DC–DC buck converter. Energy Rep. 8, 765–773 (2022).

Fong, L. K., Islam, M. S. & Ahmad, M. A. Optimized PID controller of DC-DC Buck converter based on archimedes optimization algorithm. Int. J. Rob. Control Syst. 3, 4 (2023).

Ersali, C. & Hekimoğlu, B. A novel opposition-based hybrid cooperation search algorithm with nelder–Mead for tuning of FOPID-controlled buck converter. Trans. Inst. Meas. Control 2024, 01423312231214593 (2024).

Nanyan, N. F., Ahmad, M. A. & Hekimoğlu, B. Optimal PID controller for the DC-DC Buck converter using the improved sine cosine algorithm. Results Control Optim. 14, 100352 (2024).

Izci, D., Ekinci, S. & Hekimoğlu, B. Fractional-order PID controller design for buck converter system via hybrid Lévy flight distribution and simulated annealing algorithm. Arab. J. Sci. Eng. 47(11), 13729–13747 (2022).

Izci, D. & Ekinci, S. A novel improved version of hunger games search algorithm for function optimization and efficient controller design of buck converter system. e-Prime-Adv. Electr. Eng. Electron. Energy 2, 100039 (2022).

Ekinci, S., Hekimoğlu, B., Demirören, A. & Kaya, S. DC-DC Düşürücü Dönüştürücüde FOPID Kontrolörünün Ayarlanması için Harris Şahinleri optimizasyon yaklaşimi harris hawks optimization approach for tuning of FOPID controller in DC-DC buck converter. In International Artificial Intelligence and Data Processing Symposium (IDAP) (2019).

Hekimoğlu, B., Ekinci, S. & Kaya, S. Optimal PID controller design of DC-DC buck converter using whale optimization algorithm. In 2018 International Conference on Artificial Intelligence and Data Processing (IDAP) 1–6 ( IEEE, 2018).

Xiu, J., Wang, S. & Xiu, Y. Optimum firing angles control for switched Reluctance Motor based on IPSO at Steady State. IEEE Trans. Energy Convers. (2023).

Scalcon, F. P., Vieira, R. P. & Gründling, H. A. PSO-based fast mechanical parameters estimation of switched reluctance motor drives. J. Control Autom. Electr. Syst. 33(4), 1286–1293 (2022).

Author information

Authors and Affiliations

Contributions

Mostafa Jabari: Conceptualization, Methodology, Software, Visualization, Investigation, Writing- Original draft preparation. Serdar Ekinci, Davut Izci: Data curation, Validation, Supervision, Resources, Writing - Review & Editing. Mohit Bajaj, Ievgen Zaitsev: Project administration, Supervision, Resources, Writing - Review & Editing.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Jabari, M., Izci, D., Ekinci, S. et al. Performance analysis of DC-DC Buck converter with innovative multi-stage PIDn(1+PD) controller using GEO algorithm. Sci Rep 14, 25612 (2024). https://doi.org/10.1038/s41598-024-77395-6

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-024-77395-6

Keywords

This article is cited by

-

A novel hyperbolic tangent-based PID controller tuned by the artificial lemming algorithm for nonlinear steam condenser pressure control

Scientific Reports (2026)

-

APSO-SVM Based Approach for Partial Discharge Pattern Recognition in Converter Transformer

Journal of Electrical Engineering & Technology (2026)

-

Three-phase inverter connection to a non-ideal grid control based on two-stage weight updates tactics for recurrent neural network controller

Electrical Engineering (2026)

-

PI controller design for non-ideal DC-DC buck converter using grey wolf optimization algorithm

International Journal of Information Technology (2026)

-

Efficient pressure regulation in nonlinear shell-and-tube steam condensers via a Novel TDn(1 + PIDn) controller and DCSA algorithm

Scientific Reports (2025)