Abstract

This study investigates the physical mechanisms for channel-length-dependent positive bias temperature stress (PBTS) reliability in self-aligned top-gate (SA TG) coplanar indium-gallium-zinc oxide (IGZO) thin-film transistors (TFTs). We fabricated devices with channel lengths of 3 µm, 12 µm, and 20 µm and characterized them using high-low frequency capacitance-voltage measurements and low-frequency noise analysis. Experimental results show that the 3 µm channel length device exhibits a significantly lower subgap density of states in the IGZO channel and a reduced near-interface trap density in the gate dielectric compared to its longer-channel counterparts. These reductions are strongly correlated with the enhanced PBTS reliability of the short-channel SA TG coplanar IGZO TFTs. We propose that hydrogen diffusion from the n+-IGZO source/drain extensions during fabrication may be the underlying mechanism, leading to defect passivation in both the IGZO channel and the SiO2 gate dielectric. These findings offer physical insights into the degradation behavior of IGZO TFTs and provide practical guidance for designing highly reliable backplane transistors for advanced active-matrix organic light-emitting diode displays.

Similar content being viewed by others

Introduction

Indium-gallium-zinc oxide (IGZO) has emerged as a promising alternative to conventional amorphous silicon (a-Si) for thin-film transistor (TFT) applications, owing to its superior carrier mobility, compatibility with low-temperature processing, and low off-state current1,2,3. As a result, IGZO TFTs have been widely employed in commercial displays, particularly in active-matrix organic light-emitting diode (AMOLED) technologies4,5,6. Among the various IGZO TFT architectures, the self-aligned top-gate (SA TG) coplanar structure has been widely adopted for AMOLED backplanes, offering advantages such as low parasitic capacitance and enhanced process controllability7,8. As AMOLED displays push toward higher pixel densities, scaling the channel length of TFTs has become a key design requirement. However, it has been reported that in SA TG coplanar IGZO TFTs, both the electrical characteristics and long-term reliability can vary significantly with channel length9,10,11,12. In particular, several studies have shown that positive bias temperature stress (PBTS) reliability tends to improve as the channel length decreases13,14,15. This phenomenon has been discussed in previous studies with several hypotheses, but a clear physical explanation supported by experimental validation remains insufficient.

In this study, we investigated the origin of the channel-length-dependent PBTS behavior in SA TG coplanar IGZO TFTs. Devices with different channel lengths were characterized using high-low frequency capacitance-voltage (C-V) measurements and low-frequency noise (LFN) techniques. These methods allow for the quantitative extraction of the subgap density of states (DOS) in the IGZO channel and the near-interface trap density in the gate dielectric, both of which are key contributors to PBTS-induced degradation in IGZO TFTs. Our results indicate that the improved PBTS reliability in short-channel devices is associated with concurrent reductions in both the subgap DOS of the IGZO channel and the near-interface trap density in the gate dielectric. These findings provide physical insight into the channel-length-dependent degradation behavior in SA TG coplanar IGZO TFTs and offer guidance for the design of highly reliable IGZO TFTs for advanced display applications.

Result and discussion

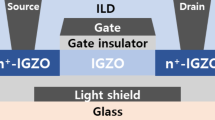

Figure 1a presents a schematic cross-sectional view of the fabricated SA TG coplanar IGZO TFTs. The detailed fabrication procedure is provided in the Methods section. Figure 1b shows the transfer characteristics of devices with channel lengths (L) of 3 µm, 12 µm, and 20 µm, with a fixed channel width (W) of 10 µm, measured at room temperature (RT). During the measurements, the gate voltage (VG) was swept from − 15 V to + 15 V, while the drain voltage (VD) was held constant at 0.1 V, and the corresponding drain current (ID) was recorded. All electrical measurements were conducted using an Agilent 4156 C semiconductor parameter analyzer. Figure 1c summarizes the electrical parameters of SA TG coplanar IGZO TFTs with various Ls(W/L = 10 µm/3, 12, 20 µm). Each point is the mean of five devices for a given channel length, and the vertical error bars denote ± 1 standard deviation. The threshold voltage VTH was extracted as the gate voltage VG corresponding to ID = (W/L) × 1 nA. As the channel becomes shorter, VTH decreases, which is attributed to hydrogen diffusion from the n+-IGZO source/drain extension regions into the channel, increasing the carrier concentration16. The field-effect mobility µFE denotes the apparent mobility, extracted without considering the source/drain parasitic resistance Rext. It was computed in the linear region at VD = 0.1 V using µFE = gmL/WCOXVD, where gm is the transconductance and COX is the gate dielectric per unit area, and the reported value corresponds to the maximum extracted µFE. Consequently, shorter channels, for which the relative Rext is larger, exhibit a smaller extracted µFE despite their higher carrier concentration. The subthreshold swing SS was calculated as (dlog(ID)/dVG)−1 in the ID range of 10− 11 – 10− 10 A and decreases as L becomes shorter.

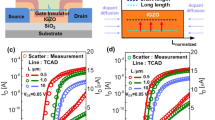

Figure 2a–c display the time evolution of the transfer characteristics for SA TG coplanar IGZO TFTs with channel lengths of (a) 3 µm, (b) 12 µm, and (c) 20 µm under PBTS conditions: overdrive voltage VOV (= VG - VTH) = 30 V, VS = VD = 0 V, and temperature = 60 ℃, where VS denotes the source voltage. Figure 2d summarizes the threshold voltage shift (ΔVTH) under PBTS for devices with different channel lengths as a function of stress time. From Fig. 2, it is observed that VTH increases with stress time in all devices: however, the ΔVTH values decrease as the channel length becomes shorter. This trend is consistent with previous reports indicating that short-channel SA TG coplanar IGZO TFTs exhibit improved PBTS stability compared to their long-channel counterparts13,14,15. Furthermore, the results in Fig. 2 clearly show that the device with a 3 µm channel length demonstrates particularly enhanced PBTS reliability relative to the devices with channel lengths of 12 µm and 20 µm.

To elucidate the physical mechanisms responsible for the phenomena observed in Fig. 2, we characterized the fabricated SA TG coplanar IGZO TFTs with various channel lengths using high-low frequency (f) C-V measurements and LFN techniques. Figure 3a–c present the normalized CG-VG (CG/COX-VG) curves measured at low (f = 100 Hz) and high (f = 1 MHz) frequencies for IGZO TFTs with L = (a) 3 µm, (b) 12 µm, (c) 20 µm, respectively. Here, CG denotes the gate-to-channel capacitance per unit area measured between the gate and the source/drain electrodes. C-V measurements were performed using a Solartron SI 1260 impedance analyzer coupled with an SI 1296 dielectric interface module. The results in Fig. 3a–c clearly demonstrate that the frequency-dependent dispersion of the normalized CG-VG characteristics becomes more pronounced with increasing channel length. In IGZO TFTs, the capacitance per unit area induced by localized subgap states (CLOC) can be extracted using the high-low frequency C-V method, as shown in Eq. (1)17,18, and the subgap DOS (g(E)) can be calculated using Eq. (2)19.

Here, CLF and CHF denote the gate-to-channel capacitance per unit area measured at low and high frequencies, respectively; tIGZO is the channel thickness of the TFTs; and q is the elementary charge. The surface potential (\(\:{\varphi\:}_{s}\)) can be nonlinearly mapped to VG using Eq. (3)20

where VFB is the flat-band voltage. Figure 3d presents the energy distribution of subgap DOS values extracted from the fabricated SA TG coplanar IGZO TFTs with L = 3 µm, 12 µm, and 20 µm near conduction band minimum (EC). The extracted subgap DOS values are divided into two components according to their energy level distribution: acceptor-like deep states (gDA) and acceptor-like tail states (gTA), in an increasing order of the energy levels. The subgap DOS profiles of each TFT near EC are well fitted with the following model

where E is the electron energy; NDA and NTA are the densities of acceptor-like deep and tail states, extrapolated to EC, respectively; and kTDA and kTTA are the corresponding characteristic energies. Table 1 summarizes the subgap DOS parameters extracted from every TFT. Figure 3d and Table 1 indicate that the subgap DOS decreases with decreasing channel length in the fabricated SA TG IGZO TFTs. In particular, the subgap DOS extracted from the device with L = 3 µm is significantly lower than that extracted from the devices with L = 12 µm or 20 µm. Previous studies have reported that a high density of acceptor-like states can degrade the PBTS reliability of IGZO TFTs21,22,23,24. The experimental results in Fig. 3; Table 1 are consistent with those in Fig. 2 and suggest that the lower subgap DOS contributes to the superior PBTS reliability observed in the short-channel SA TG coplanar IGZO TFTs.

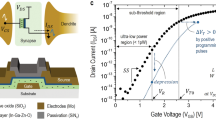

Figure 4a–c show the frequency-dependent behavior of the normalized drain current noise power spectral density (SID/ID2), measured at various ID levels by sweeping VG under a fixed VD of 0.1 V, for SA TG coplanar IGZO TFTs with channel lengths of (a) 3 µm, (b) 12 µm, and (c) 20 µm, respectively. LFN characteristics were measured under ambient conditions at RT using an Agilent 89,441 vector signal analyzer and an SR570 low-noise current amplifier (Stanford Research Systems). Figure 5a–c present SID/ID2 as a function of ID at f = 10 Hz for each device. The symbols represent the experimental data, while the solid lines denote the fitting curves obtained using the modified LFN model described in Eq. (5), which was developed by our group to accurately capture the LFN behavior in SA TG coplanar oxide TFTs25.

This model extends the conventional ΔN-Δµ framework by incorporating structural effects unique to SA TG architectures-specifically, gate-length modulation (ΔL) and large source/drain parasitic resistance (Rext)-thereby enabling improved extraction of gate dielectric trap parameters in SA TG coplanar IGZO TFTs. Therefore, the quality of the gate dielectric can be evaluated more precisely and quantitatively, and it can be effectively used to analyze the reliability of devices, especially in short-channel structures where the influence of effective channel length and parasitic resistance elements are relatively large. In Eq. (5), NB is the near-interface trap density, k the Boltzmann constant, T the temperature, gmi the intrinsic transconductance, αC the Coulomb scattering coefficient, λ the tunneling attenuation length in the gate dielectric (= 10− 8 cm)26, and RCh and RTot the channel and total resistances, respectively. The effective mobility µeff is defined in Eq. (6), which accounts for the effective channel length (Leff = L - ΔL) and Rext extracted from the fabricated devices.

Figure 5d and the inset present the extracted ΔL and W·Rext as functions of VG, obtained using the paired VG-based transmission line method at VD = 0.1 V27. Figure 6 illustrates the spatial profiles of NB as a function of tunneling depth from the IGZO/SiO2 interface, where the depth x is calculated from frequency via Eq. (7), assuming a characteristic interface time constant τ0 ≈ 10− 10s28.

As shown in Fig. 6, the extracted NB values over the tunneling depth range (x ~ 1.1–1.4 nm) show a decreasing trend with shorter channel lengths, and this trend appears more noticeable in the device with L = 3 µm compared to those with L = 12 µm and 20 µm. Given that enhanced electron trapping into the gate dielectric under PBTS typically results in greater threshold voltage shifts29,30, this observation suggests that reduced NB near the IGZO/SiO2 interface also contributes to the improved PBTS reliability seen in the short-channel SA TG coplanar IGZO TFTs.

The experimental results presented in Figs. 3, 4, 5 and 6 clearly indicate that the enhanced PBTS reliability observed in shorter-channel SA TG coplanar IGZO TFTs is closely related to the simultaneous reduction in both the subgap DOS in the IGZO channel and the near-interface trap density in the SiO2 gate dielectric. To account for the observed behavior, we propose the following physical model to explain the underlying mechanism responsible for the improved PBTS reliability in short-channel devices, as illustrated in Fig. 7. In SA TG coplanar IGZO TFTs, the source/drain extension regions are heavily n+-doped, primarily due to the diffusion of hydrogen atoms originating from the PECVD-deposited ILD into the IGZO films. The role of hydrogen in IGZO TFTs has been reported to vary depending on its concentration31,32. Given that VTH and SS both decrease as the channel length decreases, this study focused on hydrogen serving dual roles as an electron donor (e.g., H0 → H+ + e-) and as a defect passivator (e.g., ≡M-O• + H → ≡M-OH)33,34,35. During the post-deposition annealing step, hydrogen diffuses from the n+-IGZO extension regions into the adjacent channel region, leading to an increased free electron concentration and suppressed subgap DOS in IGZO16. In addition, the elevated hydrogen concentration in the IGZO channel facilitates the subsequent diffusion of hydrogen into the SiO2 gate insulator. The incorporated hydrogen atoms can passivate pre-existing defects in SiO2, likely via hydrogen-related chemical reactions such as ≡ Si• + H → ≡Si-H36,37, thereby reducing the electrical trap density near the IGZO/SiO2 interface. Figure 7a and 7(b) schematically compare the spatial distributions of carrier concentration and hydrogen diffusion effects between short-channel (L = 3 µm) and long-channel (L = 12 or 20 µm) devices. Given that the effective hydrogen diffusion length from the n+-IGZO source/drain extension into the channel region is approximately 2.5-3.0 µm, as shown in Fig. 5d, it is plausible that almost the entire channel of the 3 µm device is subject to hydrogen-induced modifications. This may account for the markedly improved PBTS reliability of the shortest-channel device relative to its longer-channel counterparts. However, when the channel length becomes shorter than the hydrogen diffusion length (ΔL) from the n+-IGZO source/drain extension regions, the carrier concentration in the channel increases excessively, which may lead to abnormal device operation. Therefore, the excellent PBTS tendency for shorter channel devices should only be considered valid within the channel length range where normal operation is guaranteed. However, since ΔL in SA TG Coplanar Oxide TFTs varies depending on process conditions such as temperature during the post-deposition process, if normal operation characteristics are secured for devices with submicron-scale channel lengths through process optimization, the phenomenon observed in this study is expected to be valid for the relevant devices as well.

Conclusion

In this study, we conducted a comprehensive analysis to identify the physical mechanisms responsible for the channel-length-dependent PBTS reliability in SA TG coplanar IGZO TFTs. Our experimental results demonstrated that short-channel devices exhibited superior PBTS reliability, with a significantly reduced ΔVTH compared to longer-channel devices. To understand this phenomenon, we employed high-low frequency C-V and LFN characterization methods. The C-V analysis revealed a clear trend: the subgap DOS in the IGZO channel decreased as the channel length was reduced. Concurrently, LFN measurements showed that the near-interface trap density in the SiO2 gate dielectric also decreased with shorter channel lengths. These findings confirm that both the IGZO bulk properties and the quality of the SiO2 gate dielectric are improved in shorter-channel devices. We possibly attribute this improvement to hydrogen diffusion from the n+-IGZO source/drain extensions during fabrication, which may passivate defects in both regions. In particular, in devices with L = 3 µm, almost the entire channel lies within the effective hydrogen diffusion range, leading to a substantial reduction in defect density and, consequently, improved PBTS reliability.

Methods

The fabrication process commenced with the deposition of a 300 nm-thick SiO2 buffer layer on a glass substrate via plasma-enhanced chemical vapor deposition (PECVD). A 30 nm-thick amorphous IGZO film (In: Ga: Zn = 1:1:1 mol%) was subsequently formed at room temperature using DC magnetron sputtering. A 150 nm-thick SiO2 gate dielectric was then deposited through PECVD, followed by the formation of a Cu/MoTi gate electrode using DC sputtering. After photolithographic definition of both the gate and gate insulator layers, interlayer dielectric (ILD) films consisting of SiOx and SiNx were sequentially deposited by PECVD and patterned to create contact vias. Source and drain electrodes composed of Cu/MoTi were then deposited and patterned to align with the gate, completing the formation of n+-IGZO source/drain extension regions. During this process, hydrogen atoms originating from the PECVD-deposited ILD layers diffused into the IGZO films, donating electrons and thereby modulating its conductivity in the source/drain extension regions. Finally, a top passivation layer of SiO2 was deposited over the entire device structure, and thermal annealing was performed to stabilize electrical characteristics and improve film uniformity.

(a) Schematic cross-sectional of the fabricated SA TG coplanar IGZO TFTs. (b) Transfer characteristics of the SA TG coplanar IGZO TFTs with various Ls (W/L = 10 µm/3, 12, 20 µm) measured in the linear region (VD = 0.1 V) at RT. (c) VTH, µFE, and SS values extracted from the SA TG coplanar IGZO TFTs with various Ls (W/L = 10 µm/3, 12, 20 µm), where each value represents the average of five devices, and the vertical error bars indicate ± 1 standard deviation.

Normalized CG-VG (CG/COX-VG) curves measured at low (f = 100 Hz) and high (f = 1 MHz) frequencies for SA TG coplanar IGZO TFTs with channel lengths of (a) 3 µm, (b) 12 µm and (c) 20 µm. (d) Energy distribution of subgap DOS value (g(E)) extracted from the fabricated SA TG coplanar IGZO TFTs with L = 3 µm, 12 µm, and 20 µm near EC.

SID/ID2 versus ID plot for SA TG coplanar IGZO TFTs with channel lengths of (a) 3 µm, (b) 12 µm, and (c) 20 µm. The symbols represent the experimental data, while the solid lines denote the fitting curves obtained using the modified LFN model. (d) ΔL values as a function of VG; the inset shows W·Rext versus VG, both extracted using the VG-based transmission line method.

Data availability

The datasets used and/or analyzed during the current study available from the corresponding author on reasonable request.

References

Kamiya, T., Nomura, K. & Hosono, H. Origins of high mobility and low operation voltage of amorphous oxide tfts: electronic structure, electron transport, defects and doping. J. Disp. Technol. 5, 273–288 (2009).

Kamiya, T., Nomura, K. & Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 11, 044305 (2010).

Kim, J. Y., Kim, H., Kim, D. & Jang, H. W. Advancements of amorphous IGZO-based transistors: materials, processing, and devices. ACS Appl. Electron. Mater. 7, 4703–4728 (2025).

Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24, 2945–2986 (2012).

Hendy, I., Brewer, J. & Muir, S. Development of high-performance IGZO backplanes for displays. Inform. Disp. 38, 60–68 (2022).

Huang, S. et al. IGZO source-gated transistor for AMOLED pixel circuit. IEEE Trans. Electron. Devices. 70, 3637–3642 (2023).

Park, J. et al. Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors. Appl. Phys. Lett. 93, 053501 (2008).

Ota, K. et al. Physical mechanism of source and drain resistance reduction for high-performance short-channel InGaZnO thin-film transistors. Jpn J. Appl. Phys. 54, 04DF06 (2015).

Kang, D. H., Han, J. U., Mativenga, M., Ha, S. H. & Jang, J. Threshold voltage dependence on channel length in amorphous-indium-gallium-zinc-oxide thin-film transistors. Appl. Phys. Lett. 102, 083508 (2013).

Kim, H. W., Kim, E. S., Park, J. S., Lim, J. H. & Kim, B. S. Influence of effective channel length in self-aligned coplanar amorphous-indium-gallium-zinc-oxide thin-film transistors with different annealing temperatures. Appl. Phys. Lett. 113, 022104 (2018).

Kim, J. B. et al. Highly stable self-aligned coplanar InGaZnO thin-film transistors and investigation on effective channel length. SID Symp. Digest Tech. Papers. 50, 874–877 (2019).

Yen, P. Y. et al. Analysis of channel-length dependence of residual hydrogen diffusion from the gate insulator during oxygen annealing treatment in IGZO TFTs. IEEE Electron. Device Lett. 45, 1586–1589 (2024).

Ha, S. H. et al. Channel length dependent bias-stability of self-aligned coplanar a-IGZO TFTs. J. Disp. Technol. 9, 985–988 (2013).

Kim, D. et al. Cation composition ratio and channel length effects on bias stress instability in amorphous InGaZnO back-end-of-line field-effect transistors. Sci. Rep. 14, 30873 (2024).

Oh, C. E. et al. Demonstration of SA TG coplanar IGZO TFTs with large subthreshold swing using the back-gate biasing technique for AMOLED applications. IEEE J. Electron. Devices Soc. 12, 564–568 (2024).

Chen, H. C. et al. Hydrogen diffusion and threshold voltage shifts in top-gate amorphous InGaZnO thin-film transistors. IEEE Trans. Electron. Devices. 67, 3123–3128 (2020).

Castagne, R. & Vapaille, A. Description of the SiO2-Si interface properties by means of very low frequency MOS capacitance measurements. Surf. Sci. 28, 157–193 (1971).

Lee, W. et al. Comparative study of C–V-based extraction methods of interface state density for a low-temperature polysilicon thin film. Mater. Res. Express. 8, 085902 (2021).

Bae, H. et al. Modified conductance method for extraction of subgap density of states in a-IGZO thin-film transistors. IEEE Electron. Device Lett. 33, 1138–1140 (2012).

Bae, M. et al. Differential ideality factor technique for extraction of subgap density of States in amorphous InGaZnO thin-film transistors. IEEE Electron Device Lett. 33, 399–401 (2012).

Oh, S. et al. Comparison of top-gate and bottom-gate amorphous InGaZnO thin-film transistors with the same SiO2/a-InGaZnO/SiO2 stack. IEEE Electron. Device Lett. 35, 1037–1039 (2014).

Lee, Y. S. et al. Oxygen flow effects on electrical properties, stability, and density of States of amorphous In–Ga–Zn–O thin-film transistors. Jpn J. Appl. Phys. 53, 121101 (2014).

Nakata, M., Zhao, C. & Kanicki, J. DC sputtered amorphous In–Sn–Zn–O thin-film transistors: electrical properties and stability. Solid State Electron. 116, 22–29 (2016).

Kim, D. H. et al. Experimental decomposition of the positive bias temperature stress-induced instability in self‐aligned coplanar InGaZnO thin‐film transistors and its modeling based on the multiple stretched‐exponential functions. Jnl Soc. Info Disp. 25, 98–107 (2017).

Lee, S. H. et al. Modeling and characterization of low frequency noise in self-aligned top-gate coplanar IGZO thin-film transistors. Semicond. Sci. Technol. 39, 115019 (2024).

Tejada, J. A. J. et al. Effects of gate oxide and junction nonuniformity on the DC and low-frequency noise performance of four-gate transistors. IEEE Trans. Electron. Devices. 59, 459–467 (2011).

Hong, S. Y. et al. Study on the lateral carrier diffusion and source-drain series resistance in self-aligned top-gate coplanar InGaZnO thin-film transistors. Sci. Rep. 9, 6588 (2019).

Ioannidis, E. G. et al. Characterization of traps in the gate dielectric of amorphous and nanocrystalline silicon thin-film transistors by 1/f noise. J. Appl. Phys. 108, 106103 (2010).

Choi, S. et al. Systematic decomposition of the positive bias stress instability in self-aligned coplanar InGaZnO thin-film transistors. IEEE Electron. Device Lett. 38, 580–583 (2017).

Rhee, J. et al. The electron trap parameter extraction-based investigation of the relationship between charge trapping and activation energy in IGZO TFTs under positive bias temperature stress. Solid State Electron. 140, 90–95 (2018).

Pan, W. et al. Multiple effects of hydrogen on InGaZnO thin-film transistor and the hydrogenation-resistibility enhancement. J. Alloys Compd. 047, 169509 (2023).

Huang, H., Peng, C., Xu, M., Chen, L. & Li, X. Dependence of a hydrogen buffer layer on the properties of top-gate IGZO TFT. Micromachines 15, 722 (2024).

Han, K. L., Cho, H. S., Ok, K. C., Oh, S. & Park, J. S. Comparative study on hydrogen behavior in InGaZnO thin film transistors with a SiO2/SiNx/SiO2 buffer on polyimide and glass substrates. Electron. Mater. Lett. 14, 749–754 (2018).

Hong, H. et al. Quantitative dynamic evolution of unoccupied states in hydrogen diffused InGaZnSnO TFT under positive bias temperature stress. ACS Appl. Electron. Mater. 6, 7584–7590 (2024).

Ge, S., Xiao, J., Yuan, D. & Zhang, S. Role of oxygen interstitials in drain current drop effect of a-InGaZnO thin‐film transistors. Jnl Soc. Info Disp. 33, 770–776 (2025).

Noh, J. Y., Han, D. M., Jeong, W. C., Kim, J. W. & Cha, S. Y. Development of 55 4K UHD OLED TV employing the internal gate IC with high reliability and short channel IGZO TFTs. Jnl Soc. Info Disp. 26, 36–41 (2018).

Park, Y. G. et al. Defect engineering for high performance and extremely reliable a-IGZO thin‐film transistor in QD‐OLED. Adv. Electron. Mater. 8, 2101273 (2022).

Acknowledgements

This research was supported by LG Display Co., Ltd. and the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (RS-2023-NR076667). This work was also supported by the Industry Technology R&D Program (RS-2025-25454815), HRD Program for Industrial Innovation (P0017011) funded by the Ministry of Trade, Industry & Energy (MOTIE) of the Republic of Korea, and the Korea Institute for Advancement of Technology (KIAT) grant funded by the Korea Government (MOTIE) (20220726).

Author information

Authors and Affiliations

Contributions

D.H.S. and C.E.O. performed numerical calculations and analyzed the results. D.H.S., C.E.O. and H.W.L. measured the electrical characteristics of the device. C.Y.J., J.M.J., B.D.A. and J.U.B. fabricated the devices. D.H.S. and C.E.O. wrote the manuscript. The project was supervised by H.I.K.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Son, DH., Oh, CE., Lee, HW. et al. Analysis of physical mechanisms for channel-length-dependent PBTS reliability in SA TG coplanar IGZO TFTs. Sci Rep 15, 43556 (2025). https://doi.org/10.1038/s41598-025-27549-x

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-27549-x