Abstract

Transformerless photovoltaic (PV) inverters are widely used in grid-connected solar energy systems due to their high efficiency and compact design. However, conventional transformerless inverters suffer from oscillating common-mode voltage (CMV), which leads to higher common-mode leakage current (CM-LC) due to the lack of galvanic isolation. This issue adversely affects system performance, safety, and compliance with grid standards. To address these challenges, this paper proposes a novel H6 Neutral Point Clamped (NPC) transformerless inverter topology, termed the H6-Diode (H6-D) topology, which integrates the advantages of AC-bypass low-loss switching and common-mode leakage current (CM-LC) elimination. The proposed topology features a clamping circuit that restricts the freewheeling voltage to half of the DC-link voltage, effectively minimizing CM-LC. The theoretical framework of the proposed design is rigorously validated through comprehensive simulations in MATLAB/Simulink and experimental verification using a laboratory prototype. The performance of the proposed inverter is evaluated based on key criteria, including common-mode voltage (CMV), common-mode leakage current (CM-LC), total harmonic distortion (%THD), switching and conduction losses, and overall efficiency. Compared to recent transformerless inverter topologies, the proposed H6-D topology demonstrates superior performance, achieving higher efficiency, lower THD, reduced voltage stress across components, and effective suppression of CM-LC. These results highlight its potential as a promising solution for high-performance grid-connected photovoltaic (PV) applications.

Similar content being viewed by others

Introduction

Photovoltaic (PV) energy is highly valued for its eco-friendly attributes and its growing role in renewable energy solutions. In grid-connected PV applications, inverters are crucial for energy conversion and can be classified as either with or without transformers. Inverters with transformers face limitations of their bulky size, weight, higher cost and power losses as well1,2. To overcome these limitations, transformer-less photovoltaic inverters (TL-PVIs) have been developed and are gaining significant attention across various fields4,5. However, TL-PVIs also present some technical challenges, primarily due to the lack of galvanic isolation between the PV system and the grid. This lack of isolation can lead to dangerous common mode leakage currents (CM-LCs) in the resonance circuit parameters, which affect current ripples, human safety, and cause electromagnetic interference (EMI) problems2,3,4. According to the VDE-AR-N 4105 standard, PV panels must disconnect from the grid if the leakage current exceeds 300mA3.

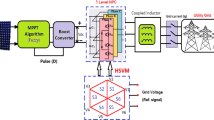

Thus, eliminating CM-LCs has become a critical issue in distributed PV systems. Various solutions have been proposed to address CM-LC issues, focusing on two main approaches. The first approach involves creating a freewheeling current path to reduce CM-LC by separating the grid from PV arrays referred as non-neutral-point-clamped method (non-NPCM). The second approach incorporates an additional clamping branch to maintain a stable common-mode voltage (CMV) with low common-mode leakage current (CM-LC), commonly known as the neutral-point-clamped method (NPCM)4,5,6. In recent advancements, super-junction metal-oxide-semiconductor field-effect transistors (SJ-MOSFETs) have been adopted as power devices to enhance the efficiency of photovoltaic (PV) systems. However, SJ-MOSFETs exhibit significant reverse recovery issues, which can lead to shoot-through effects between upper and lower complementary switches, thereby complicating the design of transformerless photovoltaic inverters (TL-PVIs)7,8. To address these challenges, various topologies have been developed using MOSFETs as the primary power devices to achieve optimal European (EU) efficiency9,10.For example, SMA proposed a non-NPC H5 topology by adding a one more switch between the DC side of the PV panel and the H4 circuit legs11. Similarly, Sunway introduced the “Highly Efficient and Reliable Inverter Concept” (HERIC) for high-efficiency applications, featuring a freewheeling branch with two IGBTs (S5 and S6) and four MOSFETs (S1-S4) to achieve higher EU efficiency12, as shown in Fig. 1(a). However, non-NPC topologies like H5 and HERIC are not ideal for PV applications due to poor common-mode behavior throughout the grid cycle. In conclusion, while TL-PVIs offer a promising solution for efficient and eco-friendly energy conversion in PV systems, addressing CM-LC issues and optimizing inverter designs remain critical areas for ongoing research and development.

On the other hand, NPCM topologies combine the benefits of galvanic isolation and common-mode (CM) clamping16,17,18. For instance, a rectifier bridge type topology namely HBZVR introduced with rectifier bridge circuit such as one active S5 switch and four diodes (D1-D4) at DC-link midpoint across the capacitor, as illustrated in Fig. 1(b)13. However, it struggles to maintain a constant CMV due to inadequate clamping during freewheeling periods. To report this issue, an additional diode was introduced in the HBZVR-D topology, which shown in Fig. 1(c)14. This modification ensures CMV constant and leakage current elimination throughout the entire grid cycle. Recently, another variant called the rectifier bridge type topology namely HB-ZVSCR was proposed to enhance common-mode characteristics depicted in Fig. 1(d)15. Similarly, positive-negative NPC (PN-NPC) and H6-family TL-PVI topologies have been developed, featuring a bidirectional active CM-clamping section presented in Fig. 1(e) and (f)16,17,18,19,20. These topologies clamp half of the DC input voltage, effectively eliminating CM-LC. However, they suffer from relatively higher losses due to the increased number of switches (S2, S5, S7 and S8) involved during freewheeling periods.

From these discussions, it is clear that while galvanic separation is crucial, it alone cannot entirely eliminate CM-LC due to device junction and stray capacitance influence on the system18–20. Further advancements in topology design and component optimization are necessary to fully address CM-LC issues and improve the performance of TL-PVIs. Another noteworthy topology, known as the oH5, utilizes a CM-active clamping technique as detailed in17. In this design, one more switch is added at the center-point of the DC-link capacitor and bridge arms to maintain a constant CMV. However, this topology fails to achieve constant CMV during dead time periods. An elegant H6 topology, introduced in20, incorporates two active switches and two passive diodes at DC-link midpoint and bridge arms. This configuration addresses some of the CMV issues but still faces challenges. In addition to the aforementioned challenges, the HBZVR, H6-type also faces limitations concerning shoot-through on the DC link in non-NPC topologies. The use of IGBTs as the main switch in this configuration further hampers performance, resulting in lower European (EU) efficiency compared to other designs. This is primarily due to the inherent characteristics of IGBTs, which generally have higher switching losses and slower response times compared to MOSFETs. The Heric topology has also seen improvements with the introduction of the Oheric inverter, as discussed in22–23. Its design includes two additional active IGBT devices (S7 and S8) at the center-point of the DC-link capacitor, which enhances CM behavior and reduces CM-LC. Nevertheless, the H6 and Oheric configurations, while effective in managing CM issues and reducing leakage currents but due to more active switches in freewheeling periods it from higher conduction losses.

Additionally, other high-efficiency clamped topologies such as I-NPC and T-NPC type half-bridge inverters have been proposed in24–25. In the I-NPC design, clamping circuits are constructed using two passive diodes, whereas the T-NPC designed by the bidirectional active devices at the center-point of the DC-link capacitor. These designs require operation at double the input DC voltage (2Vdc) in full-bridge circuits26,28,29. In the literature, another notable H6-type MOSFET solution is proposed in27–30,31, which claims excellent control of common-mode voltage (CMV) and effectively reduces leakage currents. However, it suffers from the drawback of requiring large components during freewheeling periods, which leads to increased losses. In summary, while various topologies referred as HBZVR, HBZVR-D, HBZVSCR, oH5, H6-Ttype1, H6-type2, Oheric, PN-NPC, I-NPC, and T-NPC offer solutions to manage CMV and reduce leakage currents, each has trade-offs in terms of efficiency, complexity, and switching losses32,33,34. Ongoing research and innovation are essential to optimize these designs for better performance and reliability in PV applications35,36,37.

Based on the H6-type with NPCM, a new H6 MOSFET topology is introduced to unify the ac-bypass low loss scheme with the common mode leakage current eradication capabilities of the clamping method referred as H6-D neutral point clamped inverter. This topology aims to address several critical issues in photovoltaic inverter design while enhancing overall performance.

The key features of the H6-D topology are highlighted below:

-

CMV is constant at 0.5Vdc and CM-LC is eliminated, close zero.

-

Shoot-through issues are suppressed.

-

No reverse recovery loss.

-

Overall losses reduced significantly.

-

Lower switching stress across the clamping circuit elements.

-

Enhanced European (EU) efficiency.

This H6-D MOSFET inverter offers a comprehensive solution by merging the best features of low-loss and leakage current elimination methods, paving the way for more efficient and reliable photovoltaic energy systems. Additionally, the H6-D topology is capable of reactive power generation during in non-unity power factor, which is a crucial feature for future transformer-less photovoltaic inverter (TL-PVI) topologies. The performance comparison of proposed new H6-D topology among other non-NPC (Heric, HBZVR) and NPC (HBZVSCR, PN-NPC, H6-1) TL-PVI topologies are evaluated in terms of common-mode-voltage (CMV), CM-leakage current, total harmonic distortion (%THD), loss analysis, switching stress and efficiency respectively. These comparisons are conducted through simulations and verified further with experimental tests.

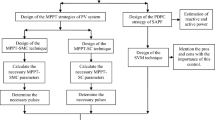

This article is systematized as follows; in Sect. "Proposed H6-type neutral-point-clamped topology" discussed the proposed H6-D topology description, principles and its modes of operations as well. Simulation and loss evaluations are framed in Sect. "Simulation results" and experimental results confirming the theoretical and simulation findings are contributed in Sect. "Experimental results" At the end summarizes the elicited results and concludes the article in Sect. "Conclusion".

Proposed H6-type neutral-point-clamped topologyy

Description of H6-D MOSFET topology and modulation method strategy

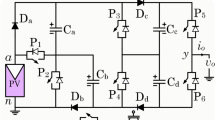

Based on the above discussions, a new H6 configuration is proposed with SJ-MOSFETs as main power devices to merge the features of the ac-bypass low-loss technique and NPCM to eliminate the common mode-leakage-current. Its topological source derivations are presented in21, which results in the failures of the gate drive circuit (shoot-through) being reduced significantly and thus enhanced system reliability and efficiency as well. Both point legs (A, B) across the DC-link are coupled with two identical inductors either L1 or L2. The proposed new H6-D consists of a five switches (S1 − S5) and the CM clamping section is realized with a trivalent rectifier bridge with one switch (S6), four diodes (D1-D4), and freewheeling path current is provided via D5 and D6 at mid-point of the DC-link capacitors, as shown in Fig. 2(a).

The proposed H6-D topology employs a modified unipolar sinusoidal pulse-width modulation (SPWM) technique, specifically tailored to align with the inverter’s structural design. This modulation approach facilitates the coordinated operation of the active switches and clamping circuit, ensuring the advantages of AC-bypass low-loss switching and effective suppression of common-mode leakage current (CM-LC). Additionally, the strategy is optimized to lower switching losses, minimize voltage stress, and maintain low total harmonic distortion (THD), enhancing the overall performance of the inverter.

The chosen modulation method was selected after a comprehensive analysis and comparison with alternative techniques, including bipolar SPWM and hybrid modulation. The unipolar SPWM approach proved to be the most effective for the H6-D topology due to the following advantages:

-

Ensures smooth operation of the clamping circuit, limiting freewheeling voltage to half of the DC-link voltage.

-

Reduces switching losses by minimizing the number of switching transitions.

-

Effectively suppresses CM-LC by maintaining a stable common-mode voltage (CMV).

Operating principles of the proposed new H6-D TL-PVI topology

The switching scheme of the H6-D TL-PVI with Unity PF is demonstrated in Fig. 2(b). Here the G1 to G6 are the modulating signals for the S1 to S6 respectively. And S6 is switched at grid frequency in the whole grid periods. Similarly, variant of proposed H6-D topology and corresponding gate pulse pattern at non-UPF, as shown in Fig. 2(c-d), where MOSFET body diodes are active and hence limited applications. The operating modes for the.

H6-D TL-PVI with three-level output voltages (+ VPV, 0, and -VPV) are described in Fig. 3. The detailed switching modes, CMV and DM evaluations on non-NPC and NPC topologies are presented in Table 12.

In mode 1 which is the active positive half-period stage (APHPS), two switches S1, S4 are tuned on and others are switched off. The current rises linearly and flows via S1, load, S4, as illustrated in Fig. 3(a).

In mode 2, during the positive half freewheeling period (PHFP) dc source is completely isolated from the grid. In this mode, S6 is switched on while the remaining switches are turned off. As depicted in Fig. 3(b), the current freewheels through D2, D3, S6, and D5, causing the inductor current to decrease accordingly. During this stage, the voltage values change: VAN decreases and VBN increases until they reach 0.5Vdc or become equal. Consequently, the freewheeling voltage is

In mode 3 it is active negative period stage (ANHP), the two switches S1, S3 are tuned on and others are switched off. During this stage current freewheels via S4, load, S3 and S5, as shown in Fig. 3(c).

In mode 4, during the negative half freewheeling period (NHFP) dc source is completely isolated from the grid. In this mode, S5, S6 are switched on while the remaining switches are turned off. As depicted in Fig. 3(d), the load current freewheels through D6, S6, load, D1 and D4, causing the inductor current to increases accordingly. During this stage, the voltage values change: VAN increases and VBN decreases until they reach 0.5Vdc or become equal. Consequently, the freewheeling voltage is

However, during the freewheeling modes, the potential of freewheeling path (PFP) is operated in two ways such as if PFP> Vdc then clamping diode D5 is active to carry the current to fixed at constant CMV and PFP< Vdc then clamping diode D6 active to flow the current to fixed at constant CMV across the centre-point of dc-link. On the other hand, in the proposed H6-D, the extra switch (S6) is helpful during the freewheeling modes such as to clamp the DC input voltage at 0.5Vdcunder abnormal conditions and also reactive power generation as well in future-generation inverters. From the discussions, it is noticed that mode1 to mode4 constant CMV achieved due to improved clamping branch in the freewheeling periods. Therefore, the CM-LC is completely eliminated20. It is clearly shown that the MOSFETs body diodes are absent in the whole grid cycle. To prevent body diode conduction and eliminate reverse recovery losses, the proposed H6-D topology is designed to operate at unity power factor (PF = 1). At non-unity PF, reactive power causes current reversals, activating MOSFET body diodes, which leads to reverse recovery losses. By maintaining unity PF, the current stays in phase with the voltage, preventing body diode conduction. The unipolar SPWM modulation used in the H6-D topology ensures smooth switching transitions, avoiding freewheeling through body diodes. Additionally, the clamping branch keeps the common-mode voltage (CMV) stable, further preventing diode activation. As a result, the H6-D topology eliminates reverse recovery losses, improving overall efficiency and reliability in transformerless PV inverters.For this reason, H6-D is made with MOSFETs as main power devices without any surplus issues. Moreover, in H6-D all MOSFETs are working at lower voltage rating, which is compared with other non-NPC and NPC topologies, and it will be discuss in the next section. It makes proposed new H6-D topology is most worthy for high efficiency PV applications.

Simulation results

Here proposed topology is tested and compared with other non-NPC and NPC configurations through simulation studies. The parameters used in these simulations include an input DC voltage of 400 V, parasitic capacitors (CPV1 and CPV2) of 100nF, and ground resistances (RG1 and RG2) of 11Ω. Additionally, the system features two identical filter inductors (L1 and L2) rated at 3mH, and a switching frequency of 10 kHz4. These parameters provide a origin for evaluating the performance of the H6-D topology against other configurations, with a focus on key metrics such as common-mode voltage (CMV), common mode leakage current (CM-LC), total harmonic distortion (THD), loss analysis, and efficiency.

Performance of output characteristics and common-mode results

Figures 4 and 5 illustrate the simulation results, showcasing the output characteristics (Vout, Iout, ileak) and the common-mode characteristics (VAN, VCM, VBN) of non-neutral-point-clamped and NPC topologies. The results demonstrate that all topologies achieve a 3-level output voltage (+ Vpv, 0, -Vpv) and produce output current in a sinusoidal behaviour. However, the HERIC has poor common-mode behavior, which is not meet theoretical expectations, particularly with floating phase-leg voltages (VAN, VBN), leading to a common-mode voltage (CMV) that oscillates around ~ 220 V, as depicted in Fig. 5(a). mode voltage (CMV) to oscillate around ~ 230 V, as shown in Fig. 5(b). This oscillation leads to a significant increase in common-mode leakage current, as depicted in Fig. 4(b). The poor clamping behavior during freewheeling periods is a key factor contributing to this issue.

Therefore, the common mode leakage current is not limited to suppress, which is displayed in Fig. 4(a). However, the HBZVR exhibits worst common-mode performance, despite the use of a clamping section. The presence of spikes in the voltages VAN, VBN and causes the common-. It has been demonstrated that neither galvanic isolation nor PWM methods alone can generate a constant CMV. Consequently, the HBZVR is categorized under the non-NPC category, exhibiting similar behavior to the HERIC topology. The aforementioned issues are overcome by NPC configurations such as HBZVR-D, HBZVSCR, PN-NPC, H6-1 such as demonstrate excellent common-mode performance, maintaining constant phase-leg voltages (VAN, VBN) and a constant CMV at 200 V, as illustrated in Fig. 5(c-f). Consequently, common mode leakage current is successfully eliminated to zero in presented in Fig. 4(c-f). The proposed H6-D topology shows enhanced common-mode performance in the clamping branch, as seen in Fig. 5(g). In this topology, no voltage spikes are observed in VAN and VBN, since they are complementary to each other. Consequently, the common-mode voltage (CMV) remains constant at 200 V across all periods, which completely eliminates the common-mode leakage current such as close zero, as depicted in Fig. 4(g).

To substantiate the claim of the voltage stress across the switches as well as zero reverse recovery losses in the MOSFET body diodes, the corresponding waveforms are presented in Fig. 6. Figure 6(a) illustrates the voltage stress across all six switches in the proposed H6-D topology. Four switches (S1, S2, S3, S4) operate at half of the DC-link voltage (0.5Vdc), while the remaining two (S5, S6) experience the full DC-link voltage (Vdc ). This arrangement effectively reduces voltage stress on most switches, enabling the use of lower voltage-rated MOSFETs. Similarly, Fig. 6(b) presents the drain-source current of the MOSFET body diodes to verify the absence of reverse recovery losses in the proposed H6-D topology. The waveform clearly shows that there are no negative transitions or spikes in the body diode current of any switch, confirming the elimination of reverse recovery losses. Consequently, the reduction in switching losses leads to improved efficiency and enhanced overall reliability of the inverter, making the H6-D topology a highly efficient solution for low-voltage applications Table 2.

Loss studies breakdown and its comparisons

This study demonstrates the loss distributions of different non-NPC and NPC topologies configured at 1 kW rated power using the thermal module in the PSIM software. And detailed simulation device parameters are listed in Table 338. In general losses are categorized into three ways referred as conduction, switching and freewheeling losses16. All theoretical calculations are little bit hard to understand but for the reader’s understanding here in-detailed loss calculations approach between IGBT and MOSFET based topologies are discussed in here.

For IGBTs conductions, diode and switching losses are calculated by the following Eqs. (10)–(14)17.

where on-state current is \(\:{I}_{C}\), \(\:{V}_{F}\:\) is forward voltage drop, \(\:\:{I}_{F}\:\) defines freewheeling current and last \(\:{V}_{dc-datasheet}\:\) is actual dc-bus voltage respectively.

And MOSFET losses are calculated by Eqs. (15) and (16)

where \(\:{R}_{ds}\:\) defines the on-state drain-source resistance, \(\:{I}_{m}\) is peak output current, M for modulation index, \(\:{f}_{sw}\:\) is switching frequency and \(\:{E}_{oss}\) is energy loss from the device data sheet respectively.

The overall device losses for each inverter are presented in the histogram in Fig. 7, where S1-S7 and D1-D6 represent the active switches and diodes of the discussed inverter topologies, as summarized in Table 4. However, the power loss calculations depend on the accuracy of the device data sheet, which is provided by the manufacturer. For the readers understanding, a comparative loss analysis between IGBT vs. MOSFET losses for heric, and proposed H6-D topologies are highlighted and recorded in Table 5. Therefore, it is noted that MOSFET based topologies are lower losses such as half of the losses are reduced if MOSFET as main power devices than IGBT topologies. However, the theoretical losses are lower than the simulation results because all values are running at real time environment and forward voltage of the device diode. But theoretical values are closer to the simulation results. For the confirmation here conduction, switching and freewheeling loss are included at one place.

Figure 8 highlights the significance of loss distribution using MOSFET designs and seen that the anti-parallel-body diode losses are entirely disregarded. As a result, the overall losses are reduced and this is reason why proposed topology placed in the second lowest losses among the Heric topology. This comprehensive analysis underscores the efficiency and effectiveness of the H6-D design in reducing overall device losses while maintaining high performance efficiency. By effectively minimizing losses, the H6-D design demonstrates a significant improvement over other topologies, making it a highly efficient solution. In addition, the detailed device operation of the discussed non-NPC and NPC topologies to compare their performance against the H6-D topology is outlined in Table 6.

As expected, the non-NPC HERIC TL-PVI topology exhibits the fewer amounts of losses due to the reduced switching count, only with active two MOSFETs during modes 1 and 3, while the other two switches operate at grid frequency during freewheeling periods (modes 2 and 4). Conversely, the HBZVR, HBZVR-D, HBZVSCR, PN-NPC and H6-1 topologies experience the highest device losses due to excessive switching count throughout the grid cycle. Among these, the H6-1 inverter has relatively lower device losses compared to the PN-NPC topology. The H6-D topology, in comparison to the PN-NPC, demonstrates lower losses primarily because it employs MOSFETs as the main power devices, which are only four switches, operate at a lower voltage rating (600 V) and one switch (S5) runs at grid frequency throughout the grid cycle. A key advantage of this setup is that the MOSFETs body diodes do not conduct during operation. This characteristic mitigates the slow reverse recovery time, which otherwise could impose a shoot-through issue on upper and lower complementary devices. Overall, these design choices in the H6-D topology contribute to its enhanced efficiency and reduced losses, making it a more effective solution for transformer-less photovoltaic inverter systems. The other detailed familiar works on loss calculation procedure and theoretical studies have been discussed in16,17,18.

Experimental results

Here a practical setup with rating of 1 kW was realized to prove with the simulation results in our laboratory test bench presented in Fig. 9. Table 7listed the specifications of the prototype bed13. All control algorithms were developed using the FPGA SPARTAN-6 platform. In this setup, only resistive loads are considered instead of a grid connection for practical development.

This type of arrangement does not affect the overall performance of the system, as similar assumptions have been made in many topologies, as referenced in12.

The output response in terms of Vout and Ioutis depicted in Fig. 10. As expected, both non-NPC and NPC topologies generate unique output voltage and current waveforms, such as unipolar and sinusoidal load waveforms. The total harmonic distortion (%THD) of the output load current was measured using the HIOKI 3197 power quality analyzer. The THD values were found to be 2.2%, 1.90%, 1.80%, 1.60%, 1.62%, and 1.43% with respect to the output voltage (V), output current (A), and output power (W) at selected measuring input parameters, as shown in Fig. 10. In Fig. 9(b) and (c), the absence of spikes in the unipolar output voltage indicates no dead time issues, resulting in slightly lower %THD compared to other topologies39. Additionally, the proposed new H6-D topology exhibits lower current harmonics compared to other established topologies, mainly because the absence of body-diodes prevents currents from circulating through the anti-parallel body diode of the MOSFET switches. This absence of body-diodes explains why the THD is lower in the proposed topology.

Figure 11 illustrates the common mode analysis of both non-NPC and NPC topologies. The common mode leakage current magnitudes for the Heric, HBZVR, HBZVSCR, PN-NPC, H6-I, and H6-D topologies are 29.19 mA, 27.13 mA, 13.94 mA, 13.46 mA, 13.43 mA, and 12.84 mA, respectively. It is observed that all configurations comply with VDE-AR-N 4105 and VDE0126-1-1 standards, with the proposed H6-D topology exhibiting the lowest common mode leakage current. Non-NPC topologies have double the common mode leakage current compared to NPC topologies due to poorer clamping ability during the freewheeling period, as explained earlier.

As expected, the non-NPC Heric and HBZVR topologies exhibit oscillating VAN, VCM, and VBN voltages with spikes up to 220 V, significantly increasing common mode leakage current, as seen in Fig. 12(a) and (b). This confirms that using PWM methods alone fails to generate a constant common mode voltage (CMV). Therefore, the realization of clamping circuits in NPC-based HBZVSCR, PN-NPC, H6-I, and H6-D topologies achieves constant CMV practically, clarifying why common mode leakage current is considerably suppressed, as seen in Fig. 12(c-f).

Figure 13 illustrations the voltage stress on S1, S2 and S3, S4 switches, which are good agreement with theoretical device operation in Table 7 such as exactly clamped at 200 V for the given input dc voltage.

The European efficiency is computed based on the following equation given below (16)28.

Efficiency measurements were conducted using the HIOKI 3197 power analyzer. The calculated efficiency performance analysis of both non-NPC and NPC inverters is illustrated in Fig. 14, showing efficiencies of 98.13%, 94.28%, 95.10%, 96.42%, 96.18%, and 97.25% for the Heric, HBZVR, HBZVSCR, PN-NPC, H6-I, and H6-D topologies, respectively. The proposed H6-D TL-PVI topology achieved the second-highest efficiency, surpassed only by the Heric topology. This high efficiency is attributed to the low switching count during freewheeling modes and the presence of only one grid frequency switch.

Overall performance comparisons are summarized in Table 8. These results demonstrate that the H6-D topology not only reduces common mode leakage current (CM-LC) and total harmonic distortion (%THD) but also offers high efficiency, making it a superior choice for transformer-less photovoltaic inverter systems.

Conclusion

This article reviews various single-phase, highly efficient, and low common-mode leakage current (CM-LC) transformerless PV inverter topologies from the H6 family, including both non-neutral point clamped (non-NPC) and neutral point clamped (NPC) configurations. The analysis reveals that non-NPC topologies, such as Heric and HBZVR, achieve excellent efficiency but demonstrate poor common-mode (CM) performance. In contrast, NPC topologies like HBZVSCR, PN-NPC, and H6-1 excel in reducing CM-LC but incur higher losses. To address these trades-offs, a novel neutral-point-clamped H6 MOSFET inverter, referred to as H6-D, is proposed. This new topology combines the low-loss characteristics of non-NPC methods with the CM-LC reduction capabilities of NPC methods. The performance of the H6-D topology is evaluated and compared to established non-NPC and NPC topologies across key metrics, including common-mode voltage (CMV), common-mode leakage current (CM-LC), losses, total harmonic distortion (%THD), voltage stress, and efficiency. Experimental results demonstrate that the H6-D topology delivers superior performance across all parameters, making it an ideal solution for high-efficiency photovoltaic (PV) applications.

Data availability

The datasets used and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Xiao, H. Overview of transformerless photovoltaic grid-connected inverters. IEEE Trans. Power Electron. 36(1), 533–548 (2021).

Khan, M. N. H. et al. Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review. IEEE J. Emerg. Sel. Top. Power Electron. 8(1), 805–835 (2020).

DKE Deutsche Kommission Elektrotechnik. Elektronik Informationstechnik im DIN und VDE, DIN VDE 0126-1-1, (2005).

Syasegov, Y. Y., Barzegarkhoo, R., Hasan, S., Li, L. & Siwakoti, Y. P. A 5-Level Mid-Point Clamped HERIC Inverter, 2022 IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems, PEDG 2022. (2022).

Li, W. et al. Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression. IEEE Trans. Industr. Electron. 62(7), 4537–4551 (2015).

Salem, A., Van Khang, H., Robbersmyr, K. G., Norambuena, M. & Rodriguez, J. Voltage source multilevel inverters with reduced device count: Topological review and novel comparative factors. IEEE Trans. Power Electron. 36, 2720–2747 (2021).

Gub´ıa, E., Sanchis, P., Urs´ua, A. & L´opez, J. andL.Marroyo, Ground currents in single-phase transformerless photovoltaic systems, Prog. Photovolt.,Res. Appl., 15(7), 629–650 (2007).

Islam, M. & Mekhilef, S. Efficient Transformerless MOSFET inverter for a Grid-Tied Photovoltaic System IEEE Trans. Power Electron., 31(9), 6310–6316, (2016).

Chen, B. et al. A high efficiency MOSFET transformerless inverter for non-isolated micro-inverter applications, IEEE Trans. Power Electron., 30(7), 3610–3622, (2015).

Schmidt, D., Siedle, D. & Ketterer, J. Inverter for transforming a DC voltage into an AC current or an AC voltage. EP Patent 1, 369 985 (2003).

Victor, M., Greizer, F., Bremicker, S. & Hubler, U. Method of converting direct current voltage from a source of direct current voltage, more specifically from a photovoltaic source of direct current voltage, into a alternating current voltage. U S Patent 7, 411 802 (2008).

Kerekes, T. et al. A New High-Efficiency Single-Phase Transformerless PV Inverter Topology, IEEE Transactions on Industrial Electronics, 58, 184–191 (2011).

Freddy, T. K. S., Rahim, N. A., Hew, W. & Che, H. S. Comparison and Analysis of Single-Phase Transformerless Grid-Connected PV Inverters, in IEEE Transactions on Power Electronics, 29(10), 5358–5369 (2014).

Khan, M. N. H., Siwakoti, Y. P., Li, L. & Blaabjerg, F. H-Bridge Zero-Voltage Switch-Controlled Rectifier Transformerless Midpoint-Clamped Inverter for Photovoltaic Applications, in IEEE Journal of Emerging and Selected Topics in Power Electronics, 8(4), 4382–4394 (2020).

Li & Zhang Kai, Feng, Hongfei and Yana A family of neutral point clamped full Bridge topologies for transformerless photovoltaic grid tied inverter. IEEE Tran Power Electron., 28, 730–739 (2013).

Xiao, H., Xi e, S. & Chen, Y. and R. Hu ang An Optimized Transformerless Photovoltaic Grid-Connected Inverter, IEEE Trans Ind Electron., 58(5), 1887–1895 (2011).

Zhu, X. et al. A novel single-phase five-level transformer-less photovoltaic (PV) inverter. CES Trans. Electr. Machines Syst. 4(4), 329–338 (2020).

Ji, B., Wang, J. & Zhao, J. High-efficiency single-phase transformer less PV H6 inverter with hybrid modulation method. IEEE Trans. Ind. Electron. 60(5), 2104–2115 (2013).

Zhang, L., Sun, K., Xing, Y. & Xing, M. H6 transformerless full-bridge PV grid-tied inverters, IEEE Trans. Power Electron., 29(3), 1229–1238, (2014).

Li, H. et al. An improved H5 topology with low common-mode current for transformerless PV grid-connected inverter. IEEE Trans. Power Electron. 34(2), 1254–1265 (2019).

Li, H., Zeng, Y., Zheng, T. Q. & Zh ang, B. A Novel H5-D Topology for Transformerless Photovoltaic G rid-connected Inverter Application, IEEE I Nt. Power Electron 731–735 (Motion Control Conf. and ECCE Asia, Hefei, May 2016).

Valderrama, G. E. et al. A single-phase asymmetrical T-type five-level transformerless PV inverter. IEEE J. Emerg. Sel. Top. Power Electron. 6(1), 140–150 (2018).

Munaretto, L. & Heldwein, M. L. Single-phase transformerless dual buck-based grid-connected inverter, in 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), 161–166, (2018).

Siwakoti, Y. P. & Blaabjerg, F. Common-ground-type transformerless inverters for single-phase solar photovoltaic systems. IEEE Trans. Industr. Electron. 65(3), 2100–2111 (2018).

Islam, M. & Mekhilef, S. H6-type transformerless single-phase inverter for grid-tied photovoltaic system IET power electroncs., 8, 636–644 (2015).

Zameer Ahmad, S. N. & Singh An improved single phase transformerless inverter topology for grid connected PV systm with reduce ground leakage current and reactive power capability. Sol. Energy. 157, 133–146 (2017).

Anandababu, C. & Fernandes, B. G. Neutral point clamped MOSFET inverter with Full-Bridge configuration for nonisolated Grid-Tied photovoltaic system. IEEE J. Emerg. Sel. Top. Power Electron. 5(1), 445–457 (2017).

Khan, M. N. H. et al. Transformerless inverter topologies for single-phase photovoltaic systems: A comparative review, IEEE J. Emerg. Sel. Topics Power Electron., 8(1), 805–835 (2020).

Meraj, S. T. et al. A novel extendable multilevel inverter for efficient energy conversion with fewer power components: configuration and experimental validation. Int. J. Circuit Theory Appl. 52(6), 2760–2785 (2024).

Yao, Z., Zhang, Y. & Hu, X. Transformerless grid-connected PV inverter without common mode leakage current and shoot-through problems. IEEE Trans. Circuits Syst. II Express Briefs. 67(12), 3257–3261 (2020).

Debela, T. & Singh, J. Switched capacitor-based single DC source boost multilevel inverter (S2-MLI) featuring isolation-based soft charging with minimum device count. Int. J. Emerg. Elec Power Syst. 22, 493–504 (2021).

Meraj, S. T. et al. sept. Three-phase six-level multilevel voltage source inverter: Modeling and experimental validation. Micromachines. 12(9), 1133 (2021).

Debela, T., Singh, J. & Sood, V. K. Evaluation of a grid-connected reduced component boost multilevel inverter (BMLI) topology. Int. J. Circ. Theor. Appl. 50, 2075–2107 (2022).

Debela, T., Singh, J. & Sood, V. K. An assessment of H-bridge less grid-tied multilevel inverter with minimum device count and lesser total standing voltage. IET Power Electron. 1–15 (2023).

Debela, T. & Singh, J. Jan., Performance evaluation of seven level grid-tied PV inverter employs seven switches with the triple gain. Int. J. Emerg. Electr. Power Syst. 1–14 (2023).

Debela, T. & Singh, J. High-gain nine-level switched-capacitor multilevel inverter featuring less number of devices and leakage current. Int. J. Circuit Theory Appl. 51 (2023).

Meraj, S. T. et al. Energy management schemes, challenges and impacts of emerging inverter technology for renewable energy integration towards grid decarbonization. J. Clean. Prod. 405, 137002 (2023).

PSIM User’s Guide. [Online]. (2007). http://www.psimeurope.com

IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed Resources With Electric Power Systems, IEEE Std 1547.1–2005, pp. 0_1–54, 2005 and Exposition (ECCE). 442–449 (2015).

Funding

This work is supported by National Foreign Experts Program of China (Y20240250).

Author information

Authors and Affiliations

Contributions

Author Contributions: Data curation, A.S.; Formal analysis, A.S., and S.B.T; Funding acquisition, S.B.T. and M.K.; Methodology, A.S., and X.G.; Project administration, S.B.T. and M.K., Resources, A.S.,, and X.G.; Supervision, X.G.; Writing–original draft, A.S. and X.G. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License, which permits any non-commercial use, sharing, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if you modified the licensed material. You do not have permission under this licence to share adapted material derived from this article or parts of it. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by-nc-nd/4.0/.

About this article

Cite this article

Syed, A., Guo, X., Thanikanti, S.B. et al. A new H6 neutral point clamped transformerless photo voltaic inverter. Sci Rep 15, 10387 (2025). https://doi.org/10.1038/s41598-025-94736-1

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s41598-025-94736-1