Abstract

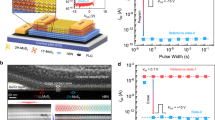

The explosion of artificial intelligence and edge devices has exposed a critical bottleneck in traditional hardware: the slow data transfer between memory and processing. Content-addressable memories offer a promising solution by processing information directly within the memory, but existing implementations using static random-access memory and, more recently, those using emerging non-volatile memories are constrained by the performance of silicon transistors. Here we introduce an analogue content-addressable memory utilizing atomically thin two-dimensional MoS2 flash memories with semimetal antimony contacts. Our device achieves a high read-out current (60 μA μm−1) and large ON/OFF ratios (>109) in two-dimensional flash memories. These breakthroughs have led to very low energy consumption (under 0.1 fJ per search per cell) and latency (36 ps) during analogue in-memory search operations within our 8 × 16 analogue content-addressable memory array, featuring 256 MoS2 flash memory devices. We have also successfully demonstrated analogue Hamming distance computing for k-nearest neighbour classification, showcasing high accuracy, high energy efficiency and low latency for machine learning applications. This research highlights the transformative potential of two-dimensional materials in overcoming current hardware limitations, enabling more efficient and scalable computing solutions in intelligent edge devices.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on SpringerLink

- Instant access to the full article PDF.

USD 39.95

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data supporting this study’s findings are available from the corresponding authors on request. Source data are provided with this paper.

Code availability

All codes supporting this study’s findings are available from the corresponding authors upon reasonable request.

References

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. Nature 601, 211–216 (2022).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Li, C. et al. Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 1, 49–57 (2019).

Pagiamtzis, K. & Sheikholeslami, A. Content-addressable memory (CAM) circuits and architectures: a tutorial and survey. IEEE J. Solid-State Circuits 41, 712–727 (2006).

McAuley, A. J. & Francis, P. Fast routing table lookup using CAMs. In Proc. IEEE INFOCOM ’93 The Conference on Computer Communications 1382–1391 (IEEE, 1993).

Chao, H. J. Next generation routers. Proc. IEEE 90, 1518–1558 (2002).

Allam, A. & Mahmoud, O. in Computer Memory and Data Storage (ed Azam, S.) Ch. 5 (IntechOpen, 2023).

Graves, C. E. et al. In-memory computing with memristor content addressable memories for pattern matching. Adv. Mater. 32, 2003437 (2020).

Liu, X. et al. Analog content-addressable memory from complementary FeFETs. Device 2, 100218 (2024).

Yin, X. et al. Deep random forest with ferroelectric analog content addressable memory. Sci. Adv. 10, eadk8471 (2024).

Yin, X. et al. FeCAM: a universal compact digital and analog content addressable memory using ferroelectric. IEEE Trans. Electron Devices 67, 2785–2792 (2020).

Ni, K. et al. Ferroelectric ternary content-addressable memory for one-shot learning. Nat. Electron. 2, 521–529 (2019).

Li, C. et al. Analog content-addressable memories with memristors. Nat. Commun. 11, 1638 (2020).

Pedretti, G. et al. Tree-based machine learning performed in-memory with memristive analog CAM. Nat. Commun. 12, 5806 (2021).

Mao, R. et al. Experimentally validated memristive memory augmented neural network with efficient hashing and similarity search. Nat. Commun. 13, 6284 (2022).

Luo, J. et al. A novel ambipolar ferroelectric tunnel FinFET-based content-addressable memory with ultra-low hardware cost and high energy efficiency for machine learning. In Proc. 2022 IEEE Symposium on VLSI Technology and Circuits 226–227 (IEEE, 2022).

Qiu, H. et al. Two-dimensional materials for future information technology: status and prospects. Sci. China Inf. Sci. 67, 160400 (2024).

Lin, Y.-C. et al. Recent advances in 2D material theory, synthesis, properties, and applications. ACS Nano 17, 9694–9747 (2023).

Liu, L. et al. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Nat. Nanotechnol. 16, 874–881 (2021).

Yu, J. et al. Simultaneously ultrafast and robust two-dimensional flash memory devices based on phase-engineered edge contacts. Nat. Commun. 14, 5662 (2023).

Wu, L. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021).

Jiang, Y. et al. A scalable integration process for ultrafast two-dimensional flash memory. Nat. Electron. 7, 868–875 (2024).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Liu, X., Choi, M. S., Hwang, E., Yoo, W. J. & Sun, J. Fermi level pinning dependent 2D semiconductor devices: challenges and prospects. Adv. Mater. 34, 2108425 (2022).

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Gao, G. et al. Enabling highly efficient, low-latency analog CAM operations with optimized MoS2 flash memory devices. In Proc. 2025 9th IEEE Electron Devices Technology & Manufacturing Conference (EDTM) 1–3 (IEEE, 2025).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Kaasbjerg, K., Thygesen, K. S. & Jacobsen, K. W. Phonon-limited mobility in n-type single-layer MoS2 from first principles. Phys. Rev. B 85, 115317 (2012).

Lu, Y.-C., Huang, J.-K., Chao, K.-Y., Li, L.-J. & Hu, V. P.-H. Projected performance of Si- and 2D-material-based SRAM circuits ranging from 16 nm to 1 nm technology nodes. Nat. Nanotechnol. 19, 1066–1072 (2024).

Agarwal, S. et al. Using floating-gate memory to train ideal accuracy neural networks. IEEE J. Explor. Solid-State Comput. Devices Circuits 5, 52–57 (2019).

Yabuuchi, M., Morimoto, M., Tsukamoto, Y. & Tanaka, S. A 7 nm FinFET 4.04-Mb mm−2 TCAM with improved electromigration reliability using far-side driving scheme and self-adjust reference match-line amplifier. In Proc. 2020 IEEE Symposium on VLSI Circuits 1–2 (IEEE, 2020).

Chang, M.-F. et al. 17.3 A 28 nm 256 kb 6T-SRAM with 280 mV improvement in Vmin using a dual-split-control assist scheme. In Proc. 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers 1–3 (IEEE, 2015).

Chang, M. F. et al. A ReRAM-based 4T2R nonvolatile TCAM using RC-filtered stress-decoupled scheme for frequent-OFF instant-ON search engines used in IoT and big-data processing. IEEE J. Solid-State Circuits 51, 2786–2798 (2016).

Lin, C.-C. et al. 7.4 A 256 b-wordlength ReRAM-based TCAM with 1 ns search time and 14× improvement in wordlength–energy-efficiency–density product using 2.5T1R cell. In Proc. 2016 IEEE International Solid-State Circuits Conference (ISSCC) 136–137 (IEEE, 2016).

Yang, R. et al. Ternary content-addressable memory with MoS2 transistors for massively parallel data search. Nat. Electron. 2, 108–114 (2019).

Lemke, C., Budka, M. & Gabrys, B. Metalearning: a survey of trends and technologies. Artif. Intell. Rev. 44, 117–130 (2015).

Vilalta, R. & Drissi, Y. A perspective view and survey of meta-learning. Artif. Intell. Rev. 18, 77–95 (2002).

Somvanshi, D. et al. Nature of carrier injection in metal/2D-semiconductor interface and its implications for the limits of contact resistance. Phys. Rev. B 96, 205423 (2017).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS2 devices. 2D Mater. 4, 011009 (2017).

Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Cui, X. et al. Low-temperature ohmic contact to monolayer MoS2 by van der Waals bonded Co/h-BN electrodes. Nano Lett. 17, 4781–4786 (2017).

Smithe, K. K. H., Suryavanshi, S. V., Muñoz Rojo, M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Guimarães, M. H. D. et al. Atomically thin ohmic edge contacts between two-dimensional materials. ACS Nano 10, 6392–6399 (2016).

Cheng, Z. et al. Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Lett. 19, 5077–5085 (2019).

McClellan, C. J., Yalon, E., Smithe, K. K. H., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Zhu, Y. et al. Monolayer molybdenum disulfide transistors with single-atom-thick gates. Nano Lett. 18, 3807–3813 (2018).

Migliato Marega, G. et al. A large-scale integrated vector–matrix multiplication processor based on monolayer molybdenum disulfide memories. Nat. Electron. 6, 991–998 (2023).

Vu, Q. A. et al. A high-on/off-ratio floating-gate memristor array on a flexible substrate via CVD-grown large-area 2D layer stacking. Adv. Mater. 29, 1703363 (2017).

Vu, Q. A. et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat. Commun. 7, 12725 (2016).

Zhang, E. et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 9, 612–619 (2015).

Migliato Marega, G. et al. Logic-in-memory based on an atomically thin semiconductor. Nature 587, 72–77 (2020).

Dodda, A., Trainor, N., Redwing, J. M. & Das, S. All-in-one, bio-inspired, and low-power crypto engines for near-sensor security based on two-dimensional memtransistors. Nat. Commun. 13, 3587 (2022).

Acknowledgements

This work was supported in part by Research Grants Council (RGC) of Hong Kong SAR (27210321 (C.L.), C7003-24Y (C.L.), C1009-22GF (C.L.), T45-701/22-R (C.L.), T46-705/23-R (L.-J.L.), CRS_PolyU502/22 (L.-J.L.), AoE/P-701/20 (D.-K.K.), the National Natural Science Foundation of China (62122005 (C.L.)); ACCESS—an InnoHK center by ITC (C.L.), MIND project (MINDXZ202503 (C.L.)), and Croucher Foundation (C.L.). L.-J.L. acknowledges support from the National Research Foundation Singapore (NRF Professorship NRF-P2025-002 (L.-J.L.)). This fabrication was performed in part at the Central Fabrication Laboratory (CFL) at HKU and the Nanosystem Fabrication Facility of HKUST.

Author information

Authors and Affiliations

Contributions

C.L. and L.-J.L. conceived the idea and supervised the project. G.G., B.W., Z.D., M.J., R.Q. and H.X. contributed to the device fabrication, measurements and data analysis. B.W. performed the simulations and data analysis. G.G., Y.C., D.Z., P.S.Y. and Q.L. performed the ALD of Al2O3 and HfO2. G.G., N.Y. and Y.W. performed the thermal deposition of Sb/Au, chemical vapour deposition growth of MoS2 and Raman characterization. G.G., B.W. and C.L. wrote and revised the manuscript with input from all authors. All authors discussed the results and provided comments on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Nanotechnology thanks Byung Chul Jang, Sungjun Kim and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

Extended Data Fig. 1 Temperature-dependent electrical characteristics and extracted Schottky barrier.

(a) Transfer characteristic curves of the MoS2 flash memory (LCH = 200 nm) measured at low temperature. (b) Output characteristic curves of the MoS2 flash memory measured at 10 K, VG = -6 V ~ 10 V. The linear IV curves at small bias voltage indicate an ideal Ohmic contact of Sb–MoS2. (c) Arrhenius plots of the ohmic Sb–MoS2 flash memory at different VG = -5 V ~ 7 V and VD = 0.1 V. (d) The extracted energy barrier vs VG, showing a negligible Schottky barrier for Sb–MoS2 flash memory at flat band state.

Extended Data Fig. 2 The extracted contact resistance Rc and benchmark.

(a) Output characteristic curves of Sb/Au Ohmic contact and Cr/Au Schottky contact devices. When using Cr/Au as contact electrodes, there exists an unavoidable Schottky barrier due to the strong Fermi level pinning at the contact interface, which usually induces non-linear output characteristic curves. In comparison, the Sb/Au contact device not only shows linear output characteristic curves, but also much larger output current. (b) Transfer characteristic curves of a typical TLM with channel length LCH ranging from 200 nm to 500 nm and VD = 1 V. Inset shows scanning electron microscope image of the Sb/Au contact devices with a TLM structure. MoS2 film was patterned into a strip with a width of 1.5 μm. Scale bar: 2 μm. (c) Rc extraction using the TLM method under different carrier densities. The y-intercept represents 2Rc = 800~1400 Ω μm, suggesting a Rc ranging from 400 Ω μm to 700 Ω μm at different carrier densities ranging from 0.19 ×1013 cm−2 to 0.77 ×1013 cm−2. (d) Rc as a function of carrier density n2D (n2D = Cox (VG – Vth)/q) for monolayer MoS2 with various contact metals or semimetals in the literature. The grey dashed line represents the quantum limit for Rc, πh/(4q2kF) ≈ 0.036(n2D)−0.5 kΩ μm, where h is Planck’s constant, q is the elementary charge, kF is the Fermi wavevector. The state-of-the-art Sb/Au-MoS2 FET was reported to approach the quantum limit in 2D semiconductor contacts26. We first reported the Sb/Au-MoS2 flash memory with ultra-small contact resistance, while at a lower carrier density, surpassing most metal contact FETs at a similar carrier density.

Extended Data Fig. 3 More data and statistics.

(a) Transfer characteristic curves of 1024 devices in four 16×16 arrays (LCH = 500 nm). (b) Statistical histograms and Gaussian fits of maximum readout current (VG = 3 V, VD = 1 V), showing a good batch-to-batch uniformity.

Extended Data Fig. 4 Selective erasing/programming of MoS2 flash memory array.

(a) Selectively erase a single cell in the same column. (b) The distribution of readout current of 96 devices within a 6x16 array, read at VG = -1.2 V and VD = 1 V. 32 devices were selectively programmed, through the readout current, three letters of “HKU” can be observed.

Extended Data Fig. 5 Cycle-to-cycle test.

(a) 1000-time program/erase (P/E) cycling experiment in DC mode, with program voltage of 13 V and erase voltage of -6V. (b) Vth drift for each cycle. (c) 105-time P/E cycling experiment in pulse mode, with pulse amplitude of 10 V for programming and -10V for erasing, pulse width of 100 ms. We observed some Vth drift over cycling. This is characteristic of an open-loop cycling test, where fixed programming/erasing conditions are applied without feedback. This drift is also exacerbated when operating near equipment limitations for pulse amplitude that necessitate longer pulse widths. In practical applications, such drift can be effectively managed. Closed-loop adaptive schemes, such as iterative program-and-verify algorithms, can be used to precisely set and maintain desired Vth levels, compensating for inherent device variations and cycling-induced shifts.

Extended Data Fig. 6 Long-term reliability and retention.

(a) The transfer characteristic curves of the original state and programmed state. The device can still be programmed even after 30 months. (b) Retention measurement over 104 s (3 h), and (c) over 15 h after 30 months.

Extended Data Fig. 7 Search operation for 1-bit to 7-bit mismatch.

(a) Programmed search boundaries of 8 analog CAM cells in the same row during search operations for 1-bit to 7-bit mismatch (bottom to top). Some cell curves appear outside the visible range as they are programmed to mismatch everything. A 0.1 V signal was applied to all DLs as input data. The cells were programmed with different search ranges to create controlled mismatch scenarios: The experimental searching boundaries for each cellb, where red traces indicate mismatch bits (high discharge current at 0.1 V input), while blue traces indicate match bits (low discharge current at 0.1 V input). (b) Input and stored data during search operations for 1-bit to 7-bit mismatch. (c) Experimental discharge behaviors observed during search operations for 1-bit to 7-bit mismatch.

Extended Data Fig. 8 TCAM used classification applications using k-nearest neighbor (KNN, k = 3) search in analog CAM and the inference latency comparison with CPU.

(a) The embedded digital data after the binarization encoding, and distance computing results for a given digital input query. The hamming distance which can be computed by TCAM is used after the binarization of data, while with limited accuracy. (b) KNN inference latency for each sample with Hamming distance or analog Hamming distance on CPU or CAM. The latency is averaged over 10 times on the 4 datasets. TCAM is a traditional 45 nm node 16 T CMOS. Compared with hamming distance, the analog hamming distance costs more time in CPU but can be efficiently accelerated by analog CAM (ACAM), about 108 times faster.

Extended Data Fig. 9 The electrical performance of MoS2 dual-gate flash memory array.

(a) The optical image 16x16 MoS2 dual-gate flash memory array, which can be used as an 8×16 analog CAM array with 256 MoS2 dual-gate flash memories (LCH/WCH = 0.5/10 µm). The scale bar is 200 µm. Inset is a zoomed-in image, showing two analog CAM cells with four MoS2 dual-gate flash memories. The scale bar is 10 µm. (b) ID-VG curves of the dual gate device at VD = 1 V, showing increased current ON/OFF ratio (~1010), ION, and steeper subthreshold slop (SS), indicating that the dual gate configuration can enhance electrostatic control, facilitate additional carrier accumulation, and improve the carrier transfer efficiency. (c) Statistics of readout current at VG = 3 V and VD = 1 V for 104 dual-gate and 586 back-gate MoS2 flash memories with LCH = 500 nm, showing a 1.5-time improvement of average readout current by dual-gate configuration. Statistical distribution of readout current at VD = 1 V and VG = 2 V for the fifty flash memories. Each box plot displays the 25% to 75% (box boundaries), median (central line), and mean (square symbol) of the data range. Whiskers extend to a full range (min to max). The symmetric distribution curve scales the full data range. (d) 10-time cycles-to-cycle test for ten programmed states with a programming voltage of 7 V ~ 12 V, showing a cycle-to-cycle uniformity. (e) The ten extracted Vth maintain distinct after over 1000 s cycles-to-cycle measurement.

Extended Data Fig. 10 Experimental demonstration of the search operations performance of one analog CAM cell with 3D-stacked complementary 2D flash memories.

(a) The schematic diagram of one analog CAM cell with 3D monolithic integration of complementary flash memories (N-type MoS2 and P-type WSe2). (b) The I_ML - V_DL curves of the analog CAM cell, showing a tunable match range. (c) The optical image of the 3D monolithic integration of complementary flash memories. Inset shows the circuit diagram. (d) Cross-sectional HAADF-STEM image, and (e) EDS mapping of the device.

Supplementary information

Supplementary Information (download PDF )

Supplementary Figs. 1–18, Notes 1–7, Tables 1 and 2 and References.

Source data

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Gao, G., Wen, B., Yang, N. et al. Sb-contacted MoS2 flash memory for analogue in-memory searches. Nat. Nanotechnol. 21, 198–206 (2026). https://doi.org/10.1038/s41565-025-02089-7

Received:

Accepted:

Published:

Version of record:

Issue date:

DOI: https://doi.org/10.1038/s41565-025-02089-7