Abstract

Memristors are a class of emerging electronic devices for in-memory computation systems, which promise to overcome the von Neumann bottleneck in traditional computer architectures. Simulation plays a critical role in designing circuits for memristive in-memory computation systems. Fast and reliable simulations require a behavioral model that accurately emulates device characteristics, accounting for real-world non-idealities. In this work, we present a memristor behavioral model that incorporates key non-idealities, including cycle-to-cycle and device-to-device resistance variations, threshold voltage variations, resistance drift in the absence of external stimulus and variations in switching dynamics. The model has been fitted to experimental data from two types of real devices: vacuum-processed self-directed channel memristors and inkjet-printed electrochemical metallization memristors, showing good agreement with both datasets. This model is used to simulate memristive stateful logic gates. Our study highlights the significance of considering device non-idealities in the practical design of memristive circuits.

Similar content being viewed by others

Introduction

Memristors are a class of two-terminal electronic components whose internal resistance is determined based on the history of applied external voltage or current. A memristor can be programmed in a non-volatile manner into a high- or low-resistive state (or a state in between)1,2,3. This unique feature was initially exploited for non-volatile memory and is recently gaining more and more interest in in-memory computation (IMC) systems4,5,6. IMC is a solution to overcome the von Neumann bottleneck, i.e., the limited throughput and large energy consumption in computing systems due to the intensive data movement between the separated memory and processing units7. In memristive-based IMC systems, the non-volatile resistive switching characteristics are exploited to store data and perform in-situ computational tasks within the memory cell itself4,5,6. The IMC systems are expected to provide high-performance and low-power computing platforms, which will facilitate further development of data-intensive applications and enhance their performance.

One promising implementation of memristive IMC systems relies on stateful logics, in which the logic inputs and outputs are represented by the state (i.e., resistance level) of memristors, and the Boolean operations are achieved by conditional resistive switching between memristors6,8. Realizing a functioning memristor-based IMC circuit requires the synergy of multiple stateful logic gates incorporated in a memristive crossbar. Therefore, simulation is an important step in assessing and optimizing the design of a memristive IMC circuit. An accurate, fast, and compact behavioral model is crucial for a reliable and computationally efficient simulation. The importance of such a model is further heightened in the memristive circuits and systems community since access to this technology is significantly more limited than traditional complementary metal-oxide semiconductor (CMOS), and simulation is the key design tool in the community. For larger circuits, this challenge is further aggravated not only because the access is more limited but also because the time necessary for simulations using physics-based models grows exponentially, limiting the size of circuits that can be simulated. This makes the design of circuits with practical relevance very difficult since the correct functionality of a conceptual circuit heavily depends on technological parameters as well as the non-idealities of the devices in that given technology. Here, circuit-technology co-design is crucial as it ensures that both the circuit and the underlying technology are optimized synergistically. By considering the unique characteristics and limitations of the underlying technology, engineers can address potential issues at the early stage of the circuit design, which will eventually yield multiple desirable attributes of the circuits, including enhanced reliability, reduced power consumption, increased speed, and improved scalability. This synergistic approach allows for the development of robust and innovative electronic systems.

There are a few widely accepted memristor compact models, including Strachan’s TaOx model9, Stanford ReRAM model10, RWTH Aachen model11, TEAM model12, and VTEAM model13. These reported compact models have their own strengths and can describe the resistive switching behavior of memristive devices. Nonetheless, these models only consider one physical state variable while overlooking non-idealities of memristive technology, such as device-to-device (D2D) variations, cycle-to-cycle (C2C) variations, and resistance drift14,15,16. We note that in the literature, we can find models that model drift; however, the implication of the term used in those papers is different than ours. For instance, in17, state drift is induced by the application of read voltage pulses, while in18, resistive drift is stimulated through the combined application of voltage and temperature. In contrast, we define drift as a change in resistance in the absence of any stimulus. These factors are highly important for designing any memristive circuit and system, including those based on stateful logic. Although some works19,20,21,22,23,24 extended existing models to reflect non-idealities, variability was mainly incorporated in a single model. None of these works considers the full aspects of real-world non-idealities. In addition, almost all of these variability-aware models were experimentally validated through one type of memristive device and may not be necessarily generalizable.

In this work, we present MemSim+, a realistic behavioral model fitted to measurement data that considers and simulates D2D and C2C variations of resistance, threshold voltage, resistance drift, and speed of state change. The developed behavioral model is validated through experimental data collected from two memristor types: vacuum-processed self-directed channel (SDC) memristors and inkjet-printed electrochemical metallization (ECM) memristors. The simulated device performance closely replicates the non-idealities observed in experimentally measured data of both memristor technologies, achieving a minimum Cohen’s d of 0.0059 for low resistance state (LRS) in SDC memristors and a Cohen’s d of 0 for SET voltage in ECM memristors. MemSim+ was applied to simulate two stateful logic gates (IMPLY and FELIX OR) as case studies, assuming implementation using SDC and ECM memristors. The key metrics of the logic gates’ operation were assessed considering device non-idealities. The assessment results further guided the subsequent optimization of the circuit design through adjustments to critical design parameters, significantly improving the output correctness probabilities. These results showcase the significance of circuit-technology co-design and their co-dependence, as well as the importance of considering non-idealities in the behavior of real devices when developing a behavioral model of memristors.

Results and discussion

Concept description

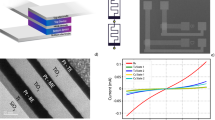

A key advantage of behavioral models is their independence from the underlying technology. This renders them universal and broadens their usage potential. Two types of memristors are studied to verify the universality of MemSim+. Their structures and underlying mechanisms are illustrated with the cross-sectional schematics in Fig. 1. The upper device, known as an SDC memristor, is fabricated using magnetron sputtering. The resistive switching of this type of device relies on the reversible concentration change of Ag that agglomerates along an SDC in the active layer25. The device at the bottom is categorized as ECM memristor, in which the resistive switching is attributed to the formation and rupture of conductive filaments in the active layer26. A detailed description of the resistive switching mechanisms in these two types of memristors is provided in Supplementary Note S1 and Supplementary Fig. S1. The ECM memristor is fabricated with inkjet printing, which is a solution-based additive manufacturing method. The details of fabricating the ECM memristor are described in the Methods section.

Two completely different types of memristors, i.e., vacuum-processed SDC and inkjet-printed ECM memristors, are characterized through electrical measurements. The experimental data serves as input to extract device characteristics parameters, which are used to complete the technology-specific MemSim+ model. The comprehensive technology-specific model can simulate device non-idealities, including D2D and C2C variations, as well as the resistance drift effect. The technology-specific MemSim+ model is validated by comparing the simulated device behavior with the experimental data of the respective memristor. The validated MemSim+ models are used to simulate stateful logic. The circuit’s performance based on different technologies can be directly compared through output distribution, considering device behavioral non-idealities.

The two types of memristors are electrically characterized separately, following the protocol described in the Methods section. The purpose is to extract key characteristic parameters from the experimental data, which can affect the operation of memristive circuits. These key characteristics are incorporated into the developed MemSim+ model to complete the construction of a comprehensive statistical model encompassing D2D and C2C variations for both technologies. The MemSim+ model, using statistically collected parameters across all devices, is then employed to simulate their respective electrical behavior and to model important figures of merit such as threshold voltage, resistance distribution, resistance drift, and speed of resistive switching. The simulated data is then compared with the experimental data to verify the model. The comprehensive MemSim+ models of two types of memristors are used for circuit simulation as case studies. The development of the MemSim+ model and its application in circuit simulation are discussed in detail in the following sections.

MemSim+ model descriptions

The MemSim+ model is developed based on a linear equation, which describes the current-voltage (I−V) characteristics of a memristor at a particular state:

where the state variable of a memristor, voltage, and current at a particular instant of time are represented by w(t), v(t), and i(t), respectively. \({w}_{\max }\) and \({w}_{\min }\) are two bounds of w(t) at which the device’s resistance at LRS (Ron) and at High Resistance State (HRS) (Roff) are determined. This description method is widely used in behavioral models of memristors12,13,27,28,29.

The state-switching dynamics of MemSim+ are described by the derivative of the state variable:

where SET and RESET differ in three parameter pairs, including coefficients of state change rate (koff and kon), threshold voltage (voff and von), and degree of (non-)linearity (αoff and αon). Instead of a precise window function, MemSim+ leverages the inherent properties of a diode, specifically its ability to allow current to flow only in one direction after crossing the threshold voltage (with the ideal diode threshold voltage being 0 V), to model a similar behavior at reduced complexity. This property enables the voltage to be limited to a specific range12,30. A complex window function, which is derived from the physics-based model31, will largely increase the complexity of behavioral models12,13. This will sacrifice the speed of a behavioral model. A term that represents a decaying integral of resistance change (Θ(t)) simulates the drift of the memristor in the absence of stimulus or under conditions where the stimulus is unable to trigger resistive switching. Θ(t) is defined as the integral of the drift depending on the state of the memristor, which is calculated using

where τ is the fade-out time constant, θoff and θon represent the influence of state change on the initial drift rate during SET and RESET processes, respectively. The ascending resistance drift in the LRS is modeled by correspondingly decreasing the value of the state variable w(t) from \({w}_{\max }\) as defined by Equation (2) and Equation (3). Similarly, the descending resistance drift in the HRS is captured by those same equations. These resistance drifts affect both state variables as well as the resistance of memristors. However, Equation (2) falls short in capturing the descending resistance drift in LRS, which requires an increase in the state variable w(t) from \({w}_{\max }\) and similarly the ascending resistance drift in HRS due to the constraints of the state variable w(t), which is restricted to the range [\({w}_{\min }\), \({w}_{\max }\)]. Consequently, instead of affecting the state w(t), these drifts only impact the resistance. According to the definition of Θ(t), the resistance drift can be integrated over time:

where D(t) represents the drift over time. By incorporating D(t) in Equation (1), the I−V characteristics of a memristor considering resistance drift effect can be expressed as:

The above equations, describing the MemSim+ model, are implemented using sub-circuits in LTspice. A detailed description of this implementation is provided in Supplementary Note S10.

Variation model

Unlike nominal models largely and typically used, MemSim+ is a behavioral model based on equations that -with appropriate coefficients- emulate the memristors’ behavior. An important aspect is that fixed coefficients can describe a single behavior, which omits the variability in the memristors’ behavior. Therefore, in the fitting process, distributions for coefficient values are considered and extracted to reproduce these variations. In this variation model, C2C variations refer to changes in a memristor’s properties, such as threshold voltages, rates of state change, and programmed resistance between each switching cycle. D2D variations encompass the aforementioned dissimilarity in device properties across different memristors (of the same technology). To assess C2C variation in device parameters, the stimulus described in the Method was repeatedly applied, 100 times to SDC memristors and 50 times ECM memristors, respectively. To capture D2D variations, 26 SDC memristors and 8 ECM memristors were characterized.

To model C2C and D2D variations, the Simulation Program With Integrated Circuit Emphasis (SPICE) function .gauss() and if-else command formatted as-if(cond., arg1, arg2)-are utilized to dynamically set model parameters rather than using nominal values. In this structure, if the condition is true, arg1 is selected; otherwise, arg2 is executed. The .gauss function generates random values based on a normal distribution (G), given a specified mean and standard deviation. In addition, to more accurately represent the real characteristics of fabricated memristors, a modified Gaussian distribution, which we call clipped Gaussian distribution (cG) is introduced. The clipped Gaussian distribution randomly selects values according to the specified mean and standard deviation, and it excludes values outside the clipping point (i.e., does not produce any value in the clipped region). This function is used as a suitable (SPICE-compatible) function to model (strongly) lobe-sided distributions. More detailed information on clipped Gaussian can be found in Supplementary Note S3 and Fig. S3. To replicate this behavior, we use a conditional statement to select a random value from the valid Gaussian distribution up to three times. If none of these values fall within the acceptable range, the function defaults to the mean value with a probability of \({(1-\frac{{R}_{{{{\rm{VG}}}}}}{{R}_{{{{\rm{total}}}}}})}^{3}\), where RVG represents the resistance values selected from the valid Gaussian distribution, and Rtotal represents the resistance values selected from the Gaussian distribution. The SPICE command for a clipped Gaussian (in this example, for the value of Roff) is given by:

which translates to

where Roff1, Roff2, and Roff3 are the three randomly selected values from the Gaussian distribution, Roffμ, is the Gaussian mean value, 40 kΩ is the clipping point, and Roff is the result of a randomly selected clipped Gaussian value. Our approach enables the simulation of both C2C and D2D variations of memristors, encompassing variations in HRS and LRS resistance, threshold voltage, resistance drift, and resistance change dynamics.

Fitting

In this section, the respective model-fitting process for SDC memristors and ECM memristors is introduced in four parts: resistance in HRS and LRS, threshold voltages, observed resistance drift, and resistance change rate. The parameter values for the nominal model (corresponding to nominal values) for both SDC and ECM memristor technologies are presented in Table 1. Table 2 provides the distributions of individual parameters, including Gaussian (G), clipped Gaussian (cG), and clipped Gaussian (cG*) with conditions, respectively denoted as \({G}_{{{{\rm{N}}}}}^{{{{\rm{M}}}}}\), \(c{G}_{{{{\rm{N}}}}}^{{{{\rm{M}}}}}\), and \(c{G}_{{{{\rm{N}}}}}^{* {{{\rm{M}}}}}\), where M represents the type of memristor (either SDC or ECM) and N indicates the modeled variable (e.g., Roff or von). The values of \({G}_{{{{\rm{N}}}}}^{{{{\rm{M}}}}}\), \(c{G}_{{{{\rm{N}}}}}^{{{{\rm{M}}}}}\), and \(c{G}_{{{{\rm{N}}}}}^{* {{{\rm{M}}}}}\) are determined during the fitting process, such that they represent the realistic behavior of actual memristors for both technologies.A flowchart is provided in Supplementary Fig. S18 under Supplementary Note S10 for an intuitive demonstration of the model-fitting and validating process.

LRS and HRS

The variations in LRS and HRS are key properties in a memristor behavior and are of substantial interest to designers of memristive circuits. The experimental data of SDC memristors show that the LRS (Ron) exhibits a Gaussian distribution \({G}_{{R}_{{{{\rm{on}}}}}}^{{{{\rm{SDC}}}}}\), whereas the distribution of the HRS (Roff) is very lobe-sided and better fits into a clipped Gaussian \(c{G}_{{R}_{{{{\rm{off}}}}}}^{{{{\rm{SDC}}}}}\). The behavior of ECM memristors is more complex. The LRS (Ron) varies significantly and doesn’t fit into one Gaussian. Hence, the experimental results are captured using three Gaussian distributions: \({G}_{{R}_{{{{\rm{on1}}}}}}^{{{{\rm{ECM}}}}}\), \({G}_{{R}_{{{{\rm{on2}}}}}}^{{{{\rm{ECM}}}}}\), and \({G}_{{R}_{{{{\rm{on3}}}}}}^{{{{\rm{ECM}}}}}\). To fit into the model, a random value is selected from \({G}_{{R}_{{{{\rm{on1}}}}}}^{{{{\rm{ECM}}}}}\), if it falls within the range of [116.32, 230] Ω; if it exceeds 230 Ω, a value is selected from \({G}_{{R}_{{{{\rm{on3}}}}}}^{{{{\rm{ECM}}}}}\), ensuring it lies within [100, 500] Ω. In all other cases, \({G}_{{R}_{{{{\rm{on2}}}}}}^{{{{\rm{ECM}}}}}\) is used. The data of HRS (Roff) follows a clipped Gaussian distribution, characterized by \(c{G}_{{R}_{{{{\rm{off}}}}}}^{{{{\rm{ECM}}}}}\). A detailed discussion on why and how we have used multiple Gaussians for modeling the memristance of ECM better is provided in Supplementary Note S3. The extracted distributions are fitted to the proposed SPICE MemSim+ model.

The stimuli with the same parameter values as those used during the experiments are applied to the modeled memristors to test the suitability of fitted functions. For SDC memristors 2600 simulation runs (corresponding to 26 devices, with each device undergoing 100 cycles) and 400 simulation runs for ECM memristors (corresponding to 8 devices, with each device undergoing 50 cycles), were executed for this evaluation. The obtained experimental and modeled memristances for SDC memristors and ECM memristors are in good agreement, as illustrated in Fig. 2a, b, respectively. A more intuitive comparison is provided in Supplementary Fig. S8, where normal distribution curves of the experimental and modeled data are superimposed. Cohen’s d32 is calculated (Supplementary Note S4) to assess the standardized difference between the mean of experimental and modeled data with respect to the memristance of two types of memristors. The calculated d further indicates a close agreement between the modeled and experimental data, with effect size33 ranging from very small (d for Ron in SDC = 0.0059) to small (d for Roff in SDC = 0.4204; d for Ron and Roff in ECM = 0.2469 and 0.3157, respectively). The reasoning behind selecting Gaussian and clipped Gaussian approaches is elaborated in detail in Supplementary Notes S3.3 and S3.4 for SDC and ECM technologies, respectively.

a Combined SET/RESET cycles for 26 SDC devices, each undergoing 100 cycles. b Combined SET/RESET cycles for 8 ECM devices, each undergoing 50 cycles. c Combined threshold voltages of 23 SDC devices, selected 20 measurements per device at the end of the forming. d Combined threshold voltages of 8 SDC devices, 20 measurements per device at the end of the hysteresis curve. e Average resistance drifts in LRS and HRS of 26 SDC devices. f Average resistance drifts in HRS of 8 ECM devices.

Threshold voltages

The threshold voltages of the memristors were extracted from the hysteresis curves recorded during repeated resistive switching cycles. For SDC memristors (measurement) and modeled memristors of both SDC and ECM technologies (using LTspice simulations with the MemSim+ model fitted to both technologies), the threshold voltages are calculated by the maximum derivative of current with respect to the voltage from I−V curves, which is illustrated in Supplementary Figs. S9 and S10. In the case of ECM memristors, the SET threshold voltage is defined as the voltage at which the maximum value of the derivative of voltage with respect to current occurs, while the RESET threshold voltage is identified at the point where current drops during the voltage sweeping, i.e., the voltage where the maximum current is observed. The variability of the experimental threshold voltages measured from SDC memristors and ECM memristors can not be captured with a single Gaussian distribution or clipped Gaussian distribution. For SDC memristors, the SET threshold voltage voff is modeled using Gaussian distribution \({G}_{{v}_{{{{\rm{off1}}}}}}^{{{{\rm{SDC}}}}}\), if it falls within the range of [150, 600] mV; otherwise, it is modeled using \({G}_{{v}_{{{{\rm{off2}}}}}}^{{{{\rm{SDC}}}}}\). Similarly, RESET threshold voltage (von) is selected from \({G}_{{v}_{{{{\rm{on1}}}}}}^{{{{\rm{SDC}}}}}\) if it is within [−550, 0] mV, or from \({G}_{{v}_{{{{\rm{on2}}}}}}^{{{{\rm{SDC}}}}}\) otherwise. For ECM memristors, SET threshold voltage is fitted with \({G}_{{v}_{{{{\rm{off1}}}}}}^{* {{{\rm{ECM}}}}}\), if the voltage is below 2.30 V. When SET voltage exceeds this threshold, it is represented by mean values due to observed higher probability in this range. RESET threshold voltage is dynamically selected from \({G}_{{v}_{{{{\rm{on1}}}}}}^{{{{\rm{ECM}}}}}\), if between −1000 mV and −190 mV, or from \(c{G}_{{v}_{{{{\rm{on2}}}}}}^{{{{\rm{ECM}}}}}\). The MemSim+ model can closely simulate the distribution of threshold voltage that is experimentally measured from SDC and ECM memristors, as depicted in Fig. 2c, d, respectively. The results presented in Fig. 2c, d are also plotted as superimposed normal distribution curves in Supplementary Fig. S11 for statistical analysis. The good agreement between modeled and experimental measured threshold voltage distribution is indicated by Cohen’s d values: for SDC memristors, d = 0.4975 and 0.3805 corresponding to Von and Voff, respectively, while for ECM devices, d = 0.2108 and 0 for Von and Voff, respectively.

Resistance drift

Resistance drift is a common phenomenon in memristors, referring to a deviation in resistance from the designed value in the absence of external electrical stimuli34,35,36. This non-ideality affects the performance of the practical memristive circuits and, therefore, needs to be considered when designing memristive circuits37,38,39. The simulation of resistance drift in the MemSim+ model is performed by representing the average resistance drift in both LRS and HRS states across multiple devices. The drift model describes an exponential behavior, where at t = 5τ the value deviates by less than 0.1% from its value at t → ∞. τ is set to one-fifth of the observed duration (t) of resistance change due to drift. The experimental data of SDC memristors indicate that the average ascending resistance drift is ~6 kΩ in LRS, and the average descending resistance drift is around 8 kΩ in HRS from the programmed values. These drifts diminish within ~25 s for both states, leading to τ being set at 5 s. The extraction of the coefficient of resistance drift after SET and RESET (θoff and θon) for modeling the resistance drift follows a process similar to that of simulating state change dynamics, where the threshold voltage and the coefficient of the state change rate corresponding to the nominal value model are considered. The ascending resistance drift in LRS and the descending resistance drift in HRS are modeled using clipped Gaussian distributions \(c{G}_{{\theta }_{{{{\rm{off}}}}}}^{* {{{\rm{SDC}}}}}\) and \(c{G}_{{\theta }_{{{{\rm{on}}}}}}^{* {{{\rm{SDC}}}}}\) respectively. The coefficients of resistance drift influence both the state as well as resistances of the memristors for these drifts. For ECM memristors, the average ascending resistance drift is 131.32 Ω in HRS. The changes in resistance over 100 seconds were modeled exponentially by setting τ to 33.34 s. The details of this fitting and calculation are described in Supplementary Note S7. No drifts occur in the LRS state of ECM memristors, hence θoff is set to zero for these memristors. To extract θon of ECM memristors, similar to the approach used for SDC memristors, kon, von, and other parameters were chosen from the nominal value model, with only resistance variations considered. The fitted value of θon does not exhibit any distribution and is properly represented by a nominal value of 203.04 ns−1. The θon only alters the resistance without affecting the state of the memristors, as the minimum value of w(t) is \({w}_{\min }\), which cannot be further reduced. The modeled resistance drifts closely replicate the experimentally observed resistance drift phenomenon, as illustrated in Fig. 2e and in Fig. 2f for SDC and ECM memristors, respectively.

State change dynamics

The rates of resistance change during the SET and RESET processes are highly complex, driven by several interdependent factors that we aim to observe and replicate as closely as possible. These intricate processes are modeled using parameters such as koff, kon, αoff, αon, voff, von, and the applied voltage. The path traversed during resistance changes is governed by αoff and αon, which are fixed at 2 to reduce mathematical complexity at the cost of accuracy. Meanwhile, koff and kon scale the state change linearly, whereas variations in the threshold voltages voff and von significantly influence the time required to change the resistance. The changes in resistance, including the initial and final resistance values, as well as the required time obtained from experimental data during the SET and RESET pulses for both technologies, are noted. The variability in kon and koff arises from differences in transition times between states that are extracted from the SET and RESET experiments, as well as from fluctuations in the threshold voltages. Once the threshold voltage is crossed, the resistance state of the device transitions completely from one state to another when the applied voltage is increased by 100 mV for SDC memristors and by 300 mV for ECM memristors. The SDC experimental data reveal a Gaussian distribution \({G}_{{k}_{{{{\rm{off}}}}}}^{{{{\rm{SDC}}}}}\) and \({G}_{{k}_{{{{\rm{on}}}}}}^{{{{\rm{SDC}}}}}\) for both koff and kon, respectively. For the ECM technology, although koff and kon do not perfectly follow a Gaussian or clipped Gaussian distribution, they can still be approximated using these distributions under certain conditions. Specifically, koff is modeled using a Gaussian distribution, \({G}_{{k}_{{{{\rm{off}}}}}}^{{{{\rm{ECM}}}}}\), for values greater than 40.80 mm s−1; if the sampled value is below this, the mean values are used instead due to the higher occurrence of mean values compared to the Gaussian distribution. Similarly, the kon parameter is approximated using a clipped Gaussian distribution \(c{G}_{{k}_{{{{\rm{on}}}}}}^{* {{{\rm{ECM}}}}}\). The kon is initially sampled from the distribution \({G}_{{k}_{{{{\rm{on}}}}}}^{{{{\rm{ECM}}}}}\) such that if the sampled value does not fall within the acceptable range defined by the distribution after three sampling attempts, a fixed value of -745 mm s−1 is selected instead of the mean value. Fig. 3a, b demonstrate a good degree of agreement during the SET pulse for SDC and ECM technology. However, during RESET pulse, we see that it follows the overall trend as opposed to instantaneous values. This is because the HRS state varies continuously, and we modeled the HRS state with a fixed resistance value using piecewise linear segments.

State change dynamics are derived from the speed of state transitions between HRS and LRS during SET and RESET operations. HRS and LRS are overall mean values calculated from 26 SDC and 8 ECM memristors, respectively. Each SDC memristor was cycled 100 times while each ECM memristor was cycled 50 times. a, b SET of SDC and ECM memristor, respectively. c, d RESET of SDC and ECM memristor, respectively.

Case study

Several memristive logics have been reported40, among which many are stateful logics41,42,43, including prominent ones such as Material Implication (IMPLY)44, and Fast and energy-efficient Logic in Memory (FELIX)45. In stateful logic, the input and output logic values are represented by the state of a device (e.g., the resistance of a memristor), and logic gates function based on the application of certain, predefined voltages to achieve the desired output. The case study in this work focuses on IMPLY logic and (2-bit) FELIX OR gate to underline the significance of considering variations in the design of memristive logic circuits.

The circuit diagram, as well as the truth table of IMPLY logic and FELIX OR gates, are illustrated in Fig. 4. The design constraints for IMPLY logic is Vset > voff, Vset > Vcond. and Ron < RG < Roff, where Vset, Vcond. are the required voltages to perform the IMPLY operation, and RG is a load resistor.

For 2-bit FELIX OR logic, the design constraints are defined as:

where \({v}_{{{{\rm{offmax}}}}}\) and \({v}_{{{{\rm{offmin}}}}}\) are the maximum and minimum set threshold voltages of the memristor, and V0 is the operating voltage required to implement the OR function. Additional design constraints are given in45 and46, and are detailed in Supplementary Notes S8 and S9 for IMPLY logic and FELIX OR, respectively.

Setup

To validate the advantages of the MemSim+ model, simulations of logic gates based on SDC and ECM memristors were conducted using the LTspice simulator47. These simulations use nominal parameter values, as outlined in Table 1, and parameter values with variations, as detailed in Table 2. In the case study, the logic gates are simulated under three scenarios for both memristor technologies. The flowchart for the simulations is provided in Fig. 5.

Each circuit was simulated and optimized through three sequential scenarios: nominal (1), realistic (2), and optimized (3). In the first scenario (gray box), the MemSim+ nominal model was used along with the selected design parameters to ensure the overall output was 100% correct. Next, the circuit was simulated again with the same design parameters while using the MemSim+ variability-aware model in the second scenario (red box). When considering the device variability, the simulated output in the second scenario dropped significantly from 100%. Therefore, the third scenario (green box) was engaged to maximize the overall output correctness by iteratively optimizing the design parameters.

As shown in Fig. 5, the three scenarios are: 1) Nominal (gray box): The logic gates were designed using a nominal model, similar to other works44,45. This approach reflects the traditional practice in circuit design, where circuits are simulated using models with nominal parameter values. 2) Realistic (red box): To assess the impact of parameter variations in circuit design, the probabilities of correct output calculation were determined by simulating the memristive logic gates using a variation model under the same setup conditions as in the first scenario (i.e., designed using nominal values). 3) Optimized (green box): By analyzing and taking into account the variation patterns of key parameters (Roff, Ron, voff, von) that influence gate functionalities, the adjustable parameters, including operating voltages (Vcond. and Vset of IMPLY; V0 of FELIX) and the resistance value of the load resistor (RG of IMPLY), were systematically altered to improve the probability of output correctness.

The range of these key parameters is shown separately in Supplementary Table S1. The resulting correct output probabilities were observed and recorded, highlighting the critical effect variations have on logic gate performance. There are several degrees of freedom concerning the investigated logic, for instance, execution time (pulse duration) or the selection of certain voltages from an allowed interval, which result in different trade-offs for performance (e.g., speed) or different aspects of robustness. However, it is out of the scope of this work to find an optimal gate design. We rather concentrate on showing this effect, which is possible to study thanks to the MemSim+ model.

For simplicity, logical value mapping threshold of 0.5 is used as example, where \(0\le s \, < \, 0.5\widehat{=}\) ‘0’ and \(0.5\le s\le 1\widehat{=}\) ‘1’, where s denotes the state of the memristor. Additionally, the results for various logic mapping schemes, considering different noise margins (the undefined region between the low logic and high logic), are provided in Supplementary Tables S2–S5. Overall correctness of logical operation was calculated as the overall probability of correctly processed outputs, i.e, \({P}_{{{{\rm{correct}}}}}=\frac{1}{4}{P}_{{{{\rm{00}}}}}+\frac{1}{4}{P}_{{{{\rm{01}}}}}+\frac{1}{4}{P}_{{{{\rm{10}}}}}+\frac{1}{4}{P}_{{{{\rm{11}}}}}\), where Pcorrect is the overall correctness, and Pij are the probabilities of the individual input combinations (for input i and j) to yield correct outputs. It is worth noting that although individual cases might experience a minor impact in relation to the logic mapping scheme, the overall correctness in all case studies shows to be negligibly impacted by the logic mapping schemes, as shown in Supplementary Figs. S12–S15.

Circuit-technology co-design and results

For the SDC memristors, the IMPLY circuit was designed by selecting the midpoint between the LRS and HRS as RG, which is calculated as 97 kΩ. All calculations under all three scenarios of IMPLY logic for SDC memristors are provided in Supplementary Note S8.1. Given the design constraints of the circuit, it has been determined that for a logic input of ‘10’, the value of Vcond. must exceed 0.76 V, while for a logic input of ‘00’, Vcond. should remain below 1.64 V to ensure proper circuit operation. These determinations are based on a Vset of 1 V. For the logic inputs ‘01’ and ‘11’, the probability of correctness of 100% was achieved without specific constraints on Vcond.. This is because if the constraints for the inputs ‘00’ are satisfied, then inputs ‘01’ and ‘11’ will automatically be satisfied as well (Supplementary Note S8.1). As a result, when Vset = 1 V and Vcond. = 0.8 V, an overall correctness of 100% is realized under the nominal scenario.

The simulation results of the realistic scenario reveal that the circuit does not perform as flawlessly as it did in the nominal scenario. In the realistic scenario, the individual output correctness dropped to 51% and 92%, respectively, for the input of ‘00’ and ‘10’, as the simulated histograms in Fig. 6a, b shows. This highlights the necessity of accounting for parameter variations to enhance performance. Taking into account the variations (Roff, Ron, voff) in memristors, RG was subsequently adjusted to 32 kΩ, which is the midpoint between maximum Ron and minimum Roff. A worst-case analysis (Supplementary Note S8.1) using the extreme values of Roff, Ron, and voff has indicated that no solution exists for Vset and Vcond. ensuring 100% output correctness in all input combinations. Still, the simulation under optimized scenario suggested that (Supplementary Table S2), an optimal overall correctness of 88.75% is achievable, when Vset, Vcond., and RG are assigned values of 1 V, 0.85 V, and 70 kΩ respectively. Specifically, individual output correctness of case ‘00’ and ‘10’ was optimized to 62% and 93%, respectively, as shown in Fig. 6c, d.

IMPLY outputs correspond to the input combinations ‘00’ and ‘10’ simulated under the realistic and optimized scenarios. SDC technology: a Inputs ‘00’ and b Inputs ‘10’ under the realistic scenario with Vcond. = 0.8 V and RG = 97 kΩ. c Inputs ‘00’ and d Inputs ‘10’ under the optimized scenario with Vcond. = 0.85 V and RG = 70 kΩ. ECM technology: e Inputs ‘00’ and f Inputs ‘10’ under the realistic scenario with Vcond. = 2 V and RG = 0.9 kΩ. g Inputs ‘00’ and h Inputs ‘10’ under the optimized scenario with Vcond. = 2 V and RG = 0.4 kΩ.

For the ECM memristors, the IMPLY circuit has been designed by selecting RG as the midpoint between the LRS and HRS, calculated as 1 kΩ for the nominal scenario. All calculations for the three scenarios of IMPLY logic for the ECM memristors are detailed in Supplementary Note S8.2. Considering the circuit design constraints, Vcond. should have been greater than 0.90 V for logic inputs ‘10’ and less than 1.19 V for logic ‘00’ when Vset is 2.5 V. Calculation and detailed discussion for this phenomenon is provided in Supplementary Note S8.2. Consequently, RG has been adjusted to 200 Ω and Vcond. to 2 V, according to the calculations derived from the optimization for the nominal scenario in Supplementary Note S8.2, can provide a sufficient voltage margin to ensure proper circuit functionality. The simulation results indicate that in the nominal scenario, the circuit operates with a 100% success rate. When considering variability under the realistic scenario, the resistor value RG was adjusted to a mid-range value between the maximum Roff and minimum Ron, settling at 900 Ω. With this adjustment, the overall output correctness dropped to 81.50%. Previous optimization efforts in the nominal scenario have demonstrated that decreasing RG enhances the success rate; simulation results indicate an improved success rate of 85.75% with RG set to 400 Ω. The optimization details are provided in Supplementary Note S8.2. The histograms of the output for inputs ‘00’ and ‘10’ across both technologies are presented in Fig. 6e–h, offering a visual representation of the data within the range of 0 to 1 and aiding in the selection of the logical mapping scheme.

The FELIX OR gate performs correctly with a probability of 100% at V0 of 0.4 V for the SDC technology and 2 V for the ECM technology, as required under the nominal scenario for both technologies, and the calculations are provided in Supplementary Note S9. A circuit designer, who considers the memristor model as a black box, would expect this behavior on a real device. In an experiment, however, the memristive circuit might not work for unknown reasons. The simulation under the realistic scenario is capable of emulating the reality of memristors’ behavior and showing the probability of correct outputs for all input logic combinations, as detailed in Table 3. The two cases inputs ‘01’ and ‘10’ do not need to be distinguished since FELIX is symmetrical regarding the inputs. Due to variations in memristors’ parameters, the probability of occurrence of correct output for FELIX OR gate is 52.00% and 73.50% as presented in Table 3 for both technologies in the realistic scenario. To address this issue, V0 is recalculated by considering the parameter variations obtained from the proposed model for both technologies. Increasing V0 raises the probability of correctness for the logic states ‘01’, ‘10’, and ‘11’ while decreasing it for the logic state ‘00’, and vice versa when V0 is reduced, as shown in Table 3. Supplementary Note S9 contains all the calculations for the three scenarios of FELIX logic applied to both technologies. Through variation-aware optimization, we achieved a probability of correct output of 87.25% for the SDC technology and 84.00% for the ECM technology. Figure 7 displays the output histograms corresponding to the logic inputs ‘00’, ‘01’, ‘10’, and ‘11’ for both technologies, providing qualitative information about the correct output for various logical mapping schemes.

FELIX OR outputs correspond to input combinations ‘00’ ‘01’/‘10’, and ‘11’ for both technologies under realistic and optimized scenarios. For SDC under realistic scenario (V0 = 0.4 V): a Inputs ‘00’. b Inputs ‘01’/‘10’. c Inputs ‘11’. For SDC under optimized scenario (V0 = 0.66 V): d Inputs ‘00’. e Inputs ‘01’/‘10’. f Inputs ‘11’. For ECM under realistic (V0 = 2 V): g Inputs ‘00’. h Inputs ‘01’/‘10’. i Inputs ‘11’. For ECM under optimized scenario (V0 = 2.6 V): j Inputs ‘00’. k Inputs ‘01’/‘10’. l Inputs ‘11’.

All design parameters involved in three simulation scenarios for the IMPLY and the FELIX OR logic gates based on two memristor technologies, together with the corresponding individual and overall output correctness for all input combinations, are summarized in Table 3. An intuitive comparison of overall output correctness simulated under three scenarios is provided in Fig. 8 as bar diagrams, where optimization of IMPLY (Fig. 8a) and FELIX OR (Fig. 8b), based on two different memristor technologies, is quantitatively demonstrated. The results for selected logical mapping schemes other than 50–50% are detailed quantitatively in Supplementary Notes S8 and S9. Due to space limitations, we only studied simulations based on SDC and ECM memristors. However, MemSim+ is capable of modeling other types of memristors and simulating circuits based on those devices.

The simulation results of IMPLY (a) and FELIX OR (b) based on SDC and ECM memristors are presented with overall correctness Pcorrect, which is the weighted sum of individual correctness Pij of all input combinations, with equal weights of \(\frac{1}{4}\). For both technologies, each logic gate was simulated in three scenarios sequentially: nominal (gray bin), realistic (red bin), and optimized (green bin).

Conclusion

The work at hand presents the MemSim+ model for ReRAMs, a realistic behavioral model that can capture non-idealities, including resistance drift, as well as C2C and D2D variations. MemSim+ is fitted to experimental data from vacuum-processed SDC memristors and ECM memristors fabricated using inkjet printing technology. The model is implemented in SPICE without additional procedural, software, or solver engines. By incorporating the statistical variation of model parameters, our model enables a more robust and reliable simulation of memristive circuits and systems. This is demonstrated by the case study that variation-aware circuit-technology co-design can significantly enhance the correctness probabilities of the IMPLY logic gate circuit, achieving correctness probability up to 88.75% (↑3.00%) for SDC technology and 85.75% (↑4.25%) for the ECM technology. Additionally, for the FELIX OR gate, the correctness probabilities increase to 85.75% (↑35.25%) for SDC technology and 84.00% (↑10.50%) for the ECM technology. The findings also indicate that the typical simulation approach (using nominal values) leads to lower chances of the fabricated circuits functioning as expected. The results showcase the significance of circuit-technology co-design and their co-dependence, as well as the importance of considering non-idealities in the behavior of real devices when designing memristive circuits and systems.

Methods

Characterization of SDC memristors

Commercial SDC memristors (W+SDC 16 Discrete Memristor Encapsulated Edge48) were electrically characterized to provide experimental data. The electrical characterizations were performed on a breadboard with the core components of the setup consisting of a low-input-offset operational amplifier49 and a multi-function instrument serving as a function generator and oscilloscope50. To avoid introducing unnecessary parasitics and charge injection effects from CMOS switching and multiplexing circuits, each memristor in the array was directly wired to the amplifier. A diligent USB oscilloscope was used to simultaneously apply the input stimulus and record the circuit’s response. The stimulus is applied to the active electrode of the memristor while the counter electrode is held at a virtual ground by the amplifier (Setup diagram and detailed description see Supplementary Fig. S2 and Supplementary Note S2.). The memristors were formed by applying a fixed sinusoidal voltage of 0.8 V, with a frequency of 100 Hz for a duration of 160 ms. Subsequently, experiments to study conductance state and resistance drift were performed. These are briefly outlined next.

SET & RESET: The memristor’s state is alternated between set (LRS) and reset (high resistance state), interleaved with read pulses to identify the established state. That is, a set pulse of amplitude 1 V (1 ms) was applied, followed by a read pulse of 0.1 V (200 μs). Next, a −1 V (1 ms) reset pulse is applied, followed by a similar read pulse. The procedure was repeated 100 times.

Resistance drift: Resistance drift is defined as a change of the memristor state in the absence of any stimulus or the stimulus whose amplitude is between the threshold voltages. To identify these dynamics, a −0.5 V reset pulse followed by three set pulses of 0.5 V was applied. In between the write pulses, 50 read pulses were issued to record the state of the memristor. All stimuli were applied one second apart.

Fabrication of ECM memristors

The fabrication process of inkjet-printed memristors is described in the following. The counter Au electrodes were patterned by laser-ablating a commercially available Au-coated glass (Sigma Aldrich) using a Trumpf TruMicro 5000 picosecond laser. The storage layer, covering the gold electrode, is fabricated by inkjet printing of an in-house-prepared Zinc nitrate-based salt, and precursor ink was prepared by dissolving 0.1 M Zn(NO3)2⋅6H2O (98%, Sigma Aldrich) in a mixed solution of de-ionized water and glycerin (Merck) (9:1 in volume). The ink was later printed onto Au counter electrodes with a drop-on-demand piezo inkjet printer (DMP2831, Fujifilm). After printing, annealing of the precursor at 400 °C over 2 h is required, to form the ZnO thin film. For the active electrode, a commercially obtained silver nanoparticulate dispersion ink (Silverjet DGP, Sigma Aldrich) was inkjet-printed onto the ZnO layer vertically, to build a crossing junction with the counter electrode, and subsequently annealed at 120 °C for 1 h.

Characterization of ECM memristors

Electrical characterizations on inkjet-printed memristors were carried out at room temperature with a semiconductor parameter analyzer (4200A-SCS, Keithley). The device under test was probed with a probe station (Cascade SUMMIT200) connected to the semiconductor parameter analyzer. For all electrical characterization, the Ag active electrode was electrically stimulated while the Au counter electrode remained grounded at all times.

The threshold voltage was collected through quasi-static voltage sweeping with a forward-and-backward sweeping rate of 0.01 V per step and 0.1 V per step, respectively. First, the printed memristors were formed following the voltage sweeping protocol of 0 V→10 V→0 V with a Compliance Current (CC) of 3 mA. Next, the formed devices were RESET and SET 20 cycles following the voltage sweeping protocol: RESET: 0 V→−1.5 V→0 V without CC and SET: 0 V→3 V→0 V with a CC of 3 mA.

SET & RESET: The HRS and LRS resistance values were collected through a dynamic pulsed voltage. The voltage pulse is generated by a Keithley 4225-PMU and 4225-RPM. The width and amplitude of voltage pulse were fixed at 10 μs and 3 V for SET, and at 50 μs and − 2.5 V for RESET. A read pulse (1 μs in width and 0.01 V in height) was used to determine the resistance after each SET and RESET voltage pulse.

Resistance drift: To evaluate the resistance drift of HRS and LRS, the device under test was SET and RESET using the same voltage pulse as aforementioned, while after each operation voltage pulse, the resistance was continuously read by 100 repeated voltage pulses (0.2 s in width and 0.01 V in height). An interval of 1 s was put between two read pulsed voltages.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

Code availability

The code supporting this work is available at https://github.com/EclectX/MemSim-Model, providing access to relevant scripts and resources to the model MemSim+.

References

Chua, L. O. & Kang, S. M. Memristive devices and systems. Proc. IEEE 64, 209–223 (1976).

Ielmini, D. & Waser, R. Resistive Switching: From Fundamentals Of Nanoionic Redox Processes To Memristive Device Applications (John Wiley & Sons, 2015).

Dittmann, R., Menzel, S. & Waser, R. Nanoionic memristive phenomena in metal oxides: the valence change mechanism. Adv. Phys. 70, 155–349 (2021).

Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. Nat. Electron. 1, 333–343 (2018).

Wang, Z. et al. Resistive switching materials for information processing. Nat. Rev. Mater. 5, 173–195 (2020).

Xu, N., Park, T., Yoon, K. J. & Hwang, C. S. In-memory stateful logic computing using memristors: gate, calculation, and application. Phys. Status Solidi (RRL)–Rapid Res. Lett. 15, 2100208 (2021).

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Kim, Y. S., Son, M. W. & Kim, K. M. Memristive stateful logic for edge boolean computers. Adv. Intell. Syst. 3, 2000278 (2021).

Demirkol, A. S. et al. A compact and continuous reformulation of the strachan tao x memristor model with improved numerical stability. IEEE Trans. Circuits Syst. I: Regul. Pap. 69, 1266–1277 (2021).

Jiang, Z. et al. A compact model for metal–oxide resistive random access memory with experiment verification. IEEE Trans. Electron Devices 63, 1884–1892 (2016).

Fleck, K. et al. Uniting gradual and abrupt set processes in resistive switching oxides. Phys. Rev. Appl. 6, 064015 (2016).

Kvatinsky, S., Friedman, E. G., Kolodny, A. & Weiser, U. C. Team: threshold adaptive memristor model. IEEE Trans. circuits Syst. I: Regul. Pap. 60, 211–221 (2012).

Kvatinsky, S., Ramadan, M., Friedman, E. G. & Kolodny, A. Vteam: a general model for voltage-controlled memristors. IEEE Trans. Circuits Syst. II Express Briefs 62, 786–790 (2015).

Menzel, S., Siemon, A., Ascoli, A. & Tetzlaff, R. Requirements and challenges for modelling redox-based memristive devices. In 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 1–5 (IEEE, 2018).

Zanotti, T., Puglisi, F. M. & Pavan, P. Circuit reliability of low-power rram-based logic-in-memory architectures. In 2019 IEEE International Integrated Reliability Workshop (IIRW), 1–5 (IEEE, 2019).

Pérez, E. et al. Analysis of the statistics of device-to-device and cycle-to-cycle variability in tin/ti/al:hfo2/tin rrams. Microelectron. Eng. 214, 104–109 (2019).

Liu, T. et al. Aidx: Adaptive inference scheme to mitigate state-drift in memristive vmm accelerators. IEEE Trans. Circuits Syst. II Express Briefs 68, 1128–1132 (2021).

Abbey, T., Giotis, C., Serb, A., Stathopoulos, S. & Prodromakis, T. Thermal effects on initial volatile response and relaxation dynamics of resistive ram devices. IEEE Electron Device Lett. 43, 386–389 (2022).

Bengel, C. et al. Variability-aware modeling of filamentary oxide-based bipolar resistive switching cells using spice level compact models. IEEE Trans. Circuits Syst. I: Regul. Pap. 67, 4618–4630 (2020).

Salvador, E. et al. Spice modeling of cycle-to-cycle variability in rram devices. Solid-State Electron. 185, 108040 (2021).

Cayo, J., Vourkas, I. & Rubio, A. A circuit-level spice modeling strategy for the simulation of behavioral variability in reram. In 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration (VLSI-SoC), 1–4 (IEEE, 2022).

Ntinas, V. et al. A simplified variability-aware vcm memristor model for efficient circuit simulation. In 2023 19th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), 1–4 (IEEE, 2023).

Ahmad, R. W. et al. Variability-aware modelling of electrochemical metallization memory cells. Neuromorph. Comput. Eng. 4, 034007 (2024).

Liu, T. et al. Aidx: Adaptive inference scheme to mitigate state-drift in memristive vmm accelerators. IEEE Trans. Circuits Syst. II Express Briefs 68, 1128–1132 (2020).

Campbell, K. A. Self-directed channel memristor for high temperature operation. Microelectron. J. 59, 10–14 (2017).

Hu, H. et al. Inkjet-printed bipolar resistive switching device based on ag/zno/au structure. Appl. Phys. Lett. 119, 112103(2021).

Strukov, D. B. et al. The missing memristor found. Nature 453, 80–83 (2008).

Joglekar, Y. N. & Wolf, S. J. The elusive memristor: properties of basic electrical circuits. Eur. J. Phys. 30, 661 (2009).

Biolek, Z., Biolek, D. & Biolkova, V. Spice model of memristor with nonlinear dopant drift. Radioengineering 18 (2009).

Cayo, J., Vourkas, I. & Rubio, A. A circuit-level spice modeling strategy for the simulation of behavioral variability in reram. In 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration (VLSI-SoC), 1–4 (2022).

Pickett, M. D. et al. Switching dynamics in titanium dioxide memristive devices. J. Appl. Phys. 106, 074508 (2009).

Goulet-Pelletier, J.-C. & Cousineau, D. A review of effect sizes and their confidence intervals, part i: the cohen’sd family. Quant. Meth. Psych. 14, 242–265 (2018).

Cohen, J. Statistical Power Analysis For The Behavioral Sciences (Routledge, 2013).

Adhikari, S. P., Kim, H., Kong, B.-S. & Chua, L. O. Memristance drift avoidance with charge bouncing for memristor-based nonvolatile memories. J. Korean Phys. Soc. 61, 1418–1421 (2012).

Amirsoleimani, A. et al. Mitigating state-drift in memristor crossbar arrays for vector matrix multiplication. In Memristor-an Emerging Device for Post-Moore’s Computing and Applications, Ch. 4 (2021).

Radakovits, D. & TaheriNejad, N. Implementation and characterization of a memristive memory system. In 2019 IEEE Canadian Conference of Electrical and Computer Engineering (CCECE), 1–4 (IEEE, 2019).

Kvatinsky, S. et al. Memristor-based material implication (imply) logic: design principles and methodologies. IEEE Trans. Very Large Scale Integr. VLSI Syst. 22, 2054–2066 (2013).

Yan, B., Yang, J., Wu, Q., Chen, Y. & Li, H. A closed-loop design to enhance weight stability of memristor based neural network chips. In 2017 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 541–548 (IEEE, 2017).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Vourkas, I. & Sirakoulis, G. C. Emerging memristor-based logic circuit design approaches: a review. IEEE Circuits Syst. Mag. 16, 15–30 (2016).

Kvatinsky, S. et al. Magic—memristor-aided logic. IEEE Trans. Circuits Syst. II Express Briefs 61, 895–899 (2014).

Huang, P. et al. Reconfigurable nonvolatile logic operations in resistance switching crossbar array for large-scale circuits. Adv. Mater. 28, 9758–9764 (2016).

TaheriNejad, N. SIXOR: single-cycle in-memristor XOR. IEEE Trans. Very Large Scale Integr. VLSI Syst. 29, 925–935 (2021).

Borghetti, J. et al. ‘memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873 (2010).

Gupta, S., Imani, M. & Rosing, T. FELIX: fast and energy-efficient logic in memory. In IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 1–7 (2018).

Kvatinsky, S. et al. Memristor-based imply logic design procedure. In ICCD2011, 142–147 (IEEE, 2011).

Ltspice simulator https://www.analog.com/en/resources/design-tools-and-calculators/ltspice-simulator.html. Accessed: 2024-09-21.

KNOWM Inc. Self Directed Channel Memristors Datasheet https://knowm.org/downloads/Knowm_Memristors.pdf (2019).

Instruments, T. Tl03x, tl03xa Enhanced-ffet Low-power Low-offset Operational Amplifiers https://www.ti.com/lit/ds/symlink/tl031.pdf (2001).

Inc., D. Analog Discovery 2 (legacy) https://digilent.com/reference/test-and-measurement/analog-discovery-2/start (2024).

Acknowledgements

The authors gratefully acknowledge the funding support from the Hector Stiftung (2304191) and from Germany’s Excellent Strategy 2082/1-390761711 (Cluster of Excellence “3D Matter Made to Order”, 3DMM2O) of Deutsche Forschungsgemeinschaft (DFG, German Research Foundation). We would like to thank Reza Rashidi and Diego Milardovich, who accompanied us during parts of this journey. Although their work did not make it into the final product, we appreciate their support. We acknowledge the financial support by Heidelberg University for the publication fee.

Funding

Open Access funding enabled and organized by Projekt DEAL.

Author information

Authors and Affiliations

Contributions

Conceptualization and methodology: G.G., D.R., and N.T.; fabrication: H.H.; measurements: H.H. and L.V. Fitting: G.G. and D.R.; simulation and co-design: G.G.; validation: G.G., H.H., D.R., L.V., and N.T.; formal analysis: G.G. and N.T.; investigation: G.G., H.H., and N.T.; resources: J.A and N.T.; writing—original draft preparation: G.G., D.R., H.H., L.V., and N.T.; writing—review and editing: G.G., H.H., L.V., G.M., J.A., and N.T.; supervision, project administration, and funding acquisition: J.A. and N.T. All authors have read and agreed to the published version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Communications Materials thanks the anonymous reviewers for their contribution to the peer review of this work. Primary Handling Editors: Sunkook Kim and Aldo Isidori.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Gulafshan, G., Hu, H., Raber-Radakovits, D. et al. Realistic behavioral model for ReRAMs capturing non-idealities. Commun Mater 6, 93 (2025). https://doi.org/10.1038/s43246-025-00807-1

Received:

Accepted:

Published:

Version of record:

DOI: https://doi.org/10.1038/s43246-025-00807-1